测试平台软件是用硬件描述语言编写的程序,在该程序中用语句为一个设计电路或系统生成测试条件,如输入的高低电平、时钟信号等,在EDA工具的支持下,直接运行程序(不需要再设计输入条件),就可以得到仿真结果。下面介绍Verilog HDL测试平台软件的设计。

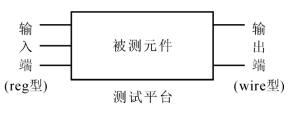

图6-38 测试平台软件的结构

测试平台软件的结构如图6-38所示,被测元件是一个已经设计好的电路或系统,测试平台软件用元件例化语句将其嵌入程序。Verilog HDL测试平台软件是一个没有输入/输出端口的设计模块,被测元件的输入端被定义为reg型(寄存器型)变量,在always块或initial块中赋值(产生测试条件),被测元件的输出端被定义为wire型变量,产生相应输入变化的输出结果(波形)。

下面介绍组合逻辑电路和时序逻辑电路的测试平台软件的设计,并以ModelSim为EDA工具,验证这些测试软件。

1.组合逻辑电路测试平台软件的设计

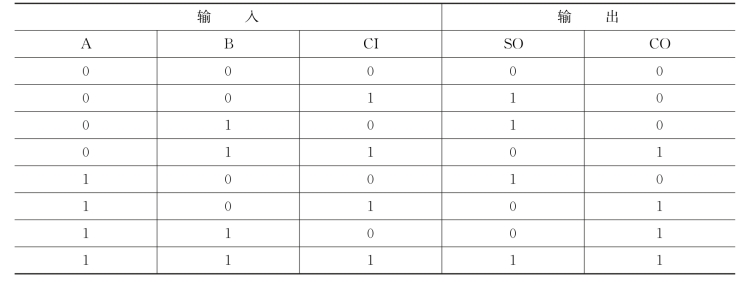

组合逻辑电路的设计验证,主要是检查设计结果是否符合该电路真值表的功能,因此在组合逻辑电路测试平台软件设计编写时,用initial块把被测电路的输入按照真值表提供的数据进行变化,作为测试条件,就能实现软件的设计。

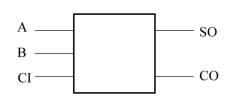

图6-39 全加器电路的逻辑符号

例6-27 编写全加器电路的测试平台软件。

全加器电路的逻辑符号如图6-39所示,全加器真值表如表6-8所示。A、B是两个1位二进制加数的输入端,CI是低位进位输入端,SO是和数输出端,CO是向高位进位输出端。

表6-8 全加器真值表

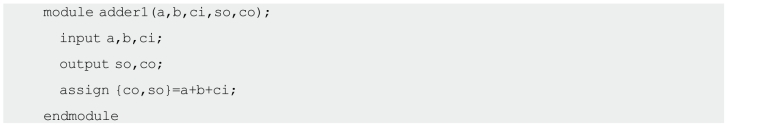

用Verilog HDL编写的全加器源程序(adder1.v)如下:

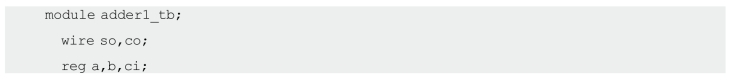

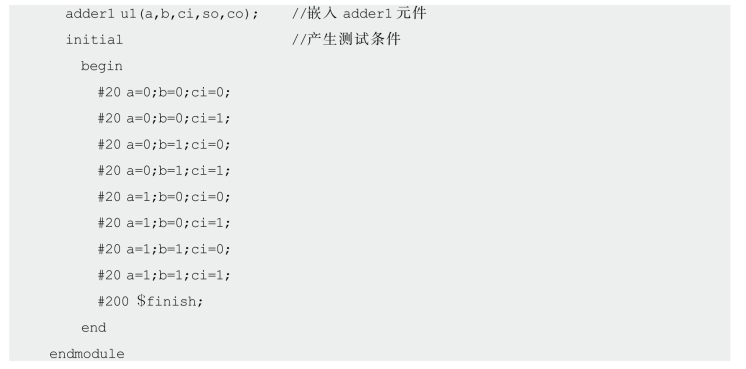

根据全加器的真值表,编写的全加器测试程序(adder1_tb.v)如下:(https://www.daowen.com)

在测试程序中,把全加器的输入a、b和ci定义为reg型变量;把输出so和co定义为wire型变量;用元件例化语句“adder1 u1(a,b,ci,so,co);”把全加器设计电路嵌入测试平台软件;用initial块语句来改变输入的变化而生成测试条件,输入的变化语句完全根据全加器的真值表编写。

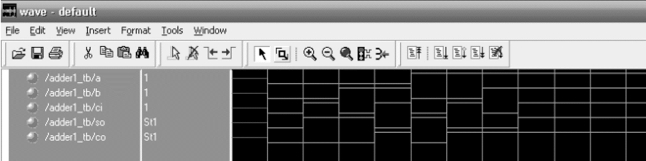

用ModelSim工具完成全加器源程序adder1.v及其测试程度adder1_tb.v的编译。测试平台软件的仿真过程与波形仿真相同,包括装载设计文件、设置仿真激励信号和执行仿真3个操作。全加器(adder1_tb.v文件)的仿真结果如图6-40所示。

图6-40 全加器的仿真结果

2.时序逻辑电路测试平台软件的设计

时序逻辑电路测试平台软件设计的要求与组合逻辑基本相同,主要区别在于,时序逻辑电路测试平台软件中,需要用always块语句生成时钟信号。

例6-28 编写十进制加法计数器的测试程序。

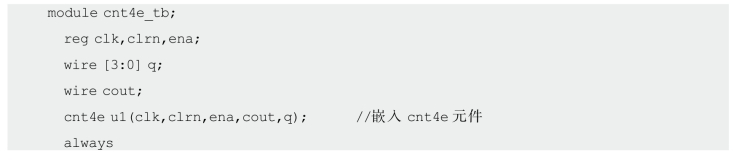

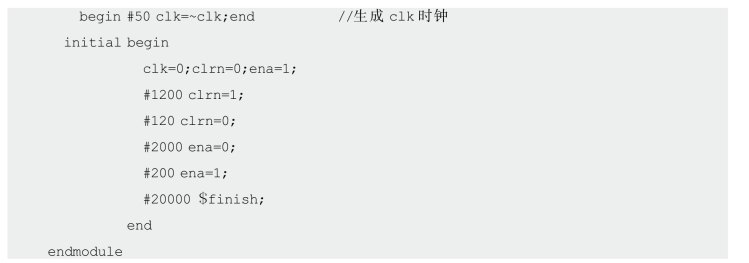

用Verilog HDL编写的4位二进制加法计数器源程序cnt4e.v已在例6-24中给出,其测试程序(cnt4e_tb.v)如下:

在源程序中,用元件例化语句“cnt4e u1(clk,clrn,ena,cout,q);”把二进制计数器设计元件嵌入测试软件;在always块中用语句“#50 clk=~clk;”产生周期为100(标准时间单位)的时钟(方波);用initial块生成复位信号clrn和使能控制信号ena的测试条件。

注意:

时钟clk只能用always块语句生成,但要在initial块中设置时钟的初值(如clk=0或clk=1),如果不设置时钟的初值,则在仿真时时钟输出端是一个未知x(不变)结果。另外,用always块生成时钟后,一定要用“$finish”语句结束仿真,否则仿真执行将不会结束。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。