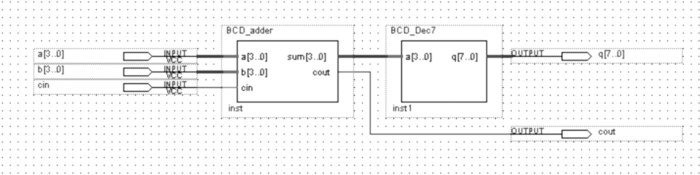

生成的BCD_adder和BCD_Dec7设计电路的元件图形符号只是代表两个分立的电路设计结果,并没有形成系统。设计顶层文件就是调用BCD_adder和BCD_Dec7两个功能元件,将它们组装起来,成为一个完整的设计。bcd_dec.bdf是本例的顶层设计文件,在QuartusⅡ集成环境下,首先为顶层设计文件建立一个新工程(bcd_dec),然后打开一个新文件,并进入图形编辑方式(选择“Block Diagram/Schematic File”)。在图形编辑框中,调出BCD_adder和BCD_Dec7元件符号以及输入和输出元件符号。

根据BCD码加法器电路设计原理,用鼠标按连接关系将各端口拉接在一起。具体操作如下:

①把输入元件INPUT与BCD_adder的cin拉接在一起,并把输入元件的名称改为cin,作为加法器低位进位输入端。

②把输入元件INPUT与BCD_adder的加数输入拉接在一起,并把输入元件的名称分别改为a[3..0]和b[3..0],作为加法器4位加数输入端。

③把BCD_adder输出sum[3..0]与BCD_Dec的输入a[3..0]拉接在一起,把BCD_Dec7的输出q[7..0]与输出元件OUTPUT拉接在一起,并把输出元件的名称改为q[7..0],作为译码器输出端。

④把输出元件OUTPUT与BCD_adder的cout拉接在一起,并把输出元件的名称改为cout,作为加法器进位输出端。(www.daowen.com)

完成上述操作后,得到BCD码加法器的顶层设计图形,如图6-35所示。顶层设计图形完成后,用bcd_dec.bdf作为文件名存入工程目录。“bcd_dec”是用户为顶层文件定义的名字,后缀.bdf表示文件为图形设计文件。

图6-35 BCD码加法器的顶层设计图形

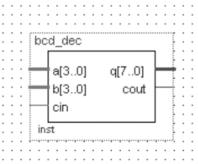

图6-36 BCD码加法器的元件符号

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。