在QuartusⅡ集成环境下,首先为BCD码加法器设计电路建立一个新工程,然后执行“File”菜单的“New”命令,弹出如图6-31所示的打开新文件对话框,选择对话框中的“Verilog HDL File”文件类型,进入Verilog HDL文本编辑方式。

图6-31 打开新文件对话框

1.编辑BCD码加法器的Verilog HDL源程序

进入Verilog HDL文本编辑方式后,编辑BCD码加法器的Verilog HDL源程序,并以BCD_adder.v为源程序的文件名,保存在D:\myeda\v工程目录中,后缀.v表示文件为Verilog HDL源程序文件。

注意:

Verilog HDL源程序的文件名应与设计模块名相同,否则将是一个错误,无法通过编译。

BCD码加法器的BCD_adder.v源程序如下:

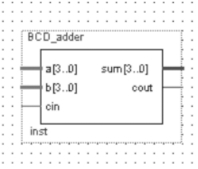

图6-32 BCD_adder元件符号(https://www.daowen.com)

完成BCD码加法器源程序的编辑后,用BCD_adder.v文件名存盘,然后在QuartusⅡ集成环境下,对BCD_adder进行编译,执行“File”菜单的“Create/Update”项的“Create Symbol Files for Current File”命令,为BCD_adder设计文件生成元件符号,如图6-32所示。在元件符号中,细的输入/输出线表示单变量线,如cin和cout;粗的输入/输出线表示多变量总线,如a[3..0]、b[3..0]和sum[3..0]。

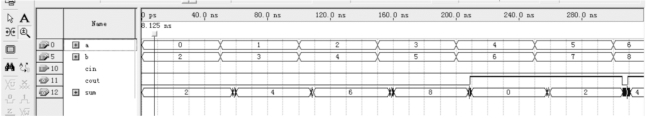

BCD码加法器的仿真波形如图6-33所示,仿真结果验证了设计的正确性。

图6-33 BCD码加法器的仿真波形

2.编辑七段数码显示译码器的源程序

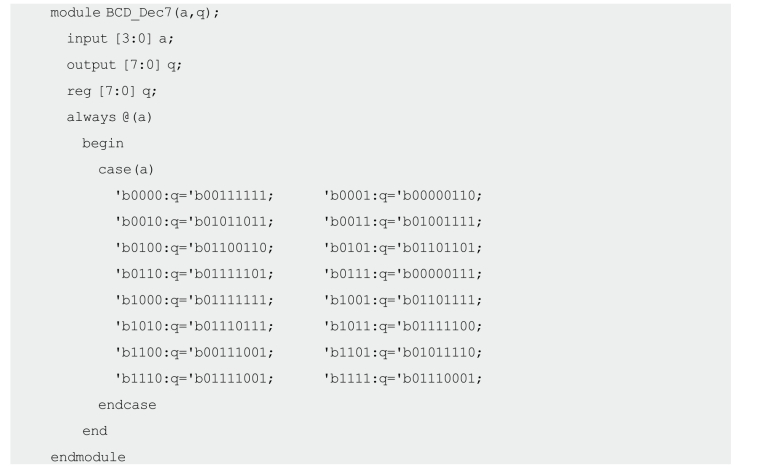

首先为七段数码显示译码器设计电路建立一个新工程,然后在Verilog HDL文本编辑方式下,编辑七段数码显示译码器的源程序,并以BCD_Dec7.v为源程序名,保存在工程目录中。BCD_Dec7.v源程序如下:

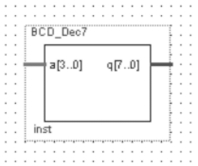

图6-34 显示译码器的元件符号

为了使BCD_Dec.v源程序也能作为十六进制译码器,应将A~F十六进制数的译码输出也包括在内。BCD_Dec.v通过编译后,生成显示译码器的元件符号,如图6-34所示。在元件符号中,a[3..0]是译码器的输入端,将与BCD码加法器的输出端sum[3..0]连接;q[7..0]是译码器的输出端,为七段数码显示译码器提供显示数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。