任何用Verilog HDL描述的电路设计模块,均可用模块例化语句,例化一个元件,来实现系统电路的设计。

模块例化语句格式与逻辑门例化语句格式类似,具体格式如下:

设计模块名 例化电路名(端口列表);

其中,“设计模块名”是用户设计的电路模块名,相当于设计电路中的一个元件;“例化电路名”是用户为系统电路设计定义的标识符(为可选项),相当于系统电路板上为插入设计模块元件而定义的插座;而“端口列表”用于描述设计模块元件上的引脚与“插座”上引脚的连接关系。

端口列表的关联方法有两种:

一种是位置关联法。要求端口列表中的引脚名称与设计模块的输入/输出端口一一对应。例如,设计模块名为cnt10的输入/输出端口为clk和cout,而以u1为例化电路名的两个引脚名是x1和x2,那么采用位置关联法描述的模块例化语句为

cnt10 u1(x1,x2);

另一种是名称关联法。名称关联法的格式如下:

设计模块名 例化电路名(.设计模块端口名(插座引脚名),.设计模块端口名(插座引脚名),…);

例如,用名称关联法完成cnt10的模块例化语句如下:

cnt10 u1(.c l k(x1),.cout(x2));

两种关联法各有特点,位置关联法简单,但没有名称关联法直观。

例6-24 用模块例化语句设计8位计数译码器系统电路。

在8位计数译码器系统电路设计中,需要事先设计一个4位二进制加法计数器cnt4e模块和一个七段数码显示的译码器Dec7s模块,然后用模块例化方式将这两种模块组成计数译码器系统电路。

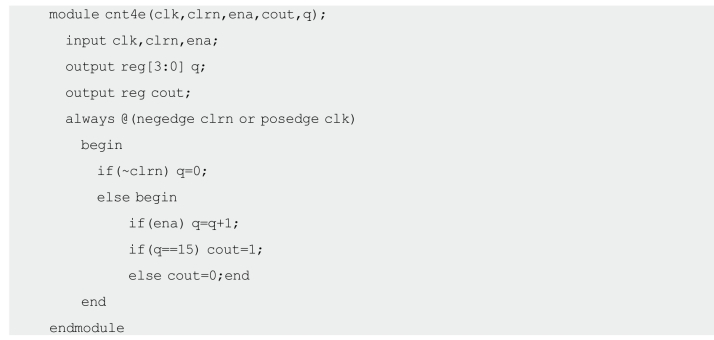

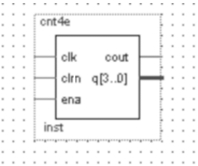

①设计4位二进制加法计数器cnt4e模块。

cnt4e的元件符号如图6-27所示,clk是时钟输入端;clrn是复位控制输入端,当clrn=1时计数器被复位,输出q[3..0]=0000;ena是使能控制输入端,当ena=1时,计数器才能工作;cout是进位输出端,当输出q[3..0]=’b1111时,cout=1。

cnt4e的Verilog HDL源程序cnt4e.v如下:

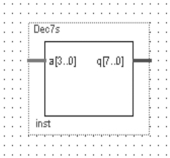

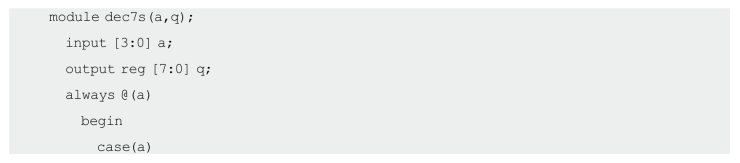

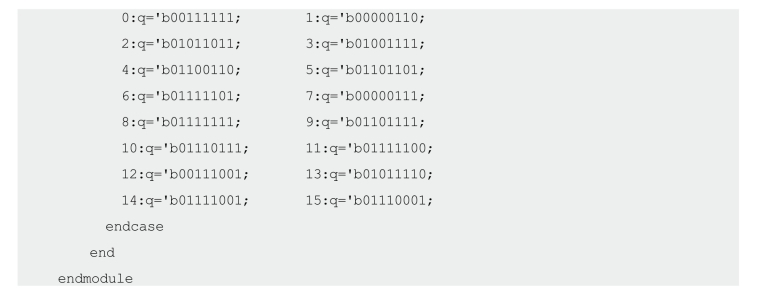

②设计七段数码显示的译码器Dec7s模块。

Dec7s的元件符号如图6-28所示,a[3..0]是4位数据输入端,将接至cnt4e的输出端q[3..0];q[7..0]是译码器的输出端,提供七段数码显示数据。(www.daowen.com)

图6-27 cnt4e的元件符号

图6-28 Dec7s的元件符号

Dec7s的Verilog HDL源程序dec7s.v如下:

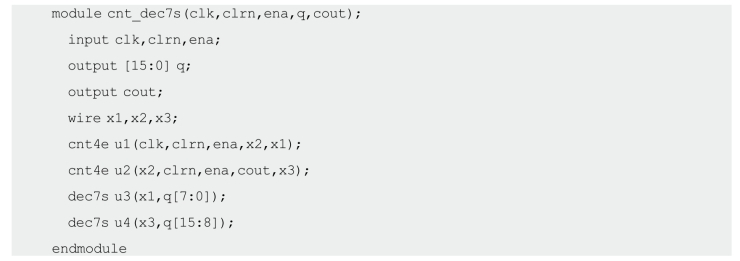

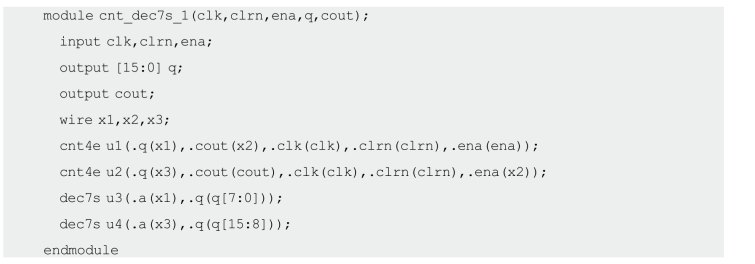

③设计计数译码器系统电路。

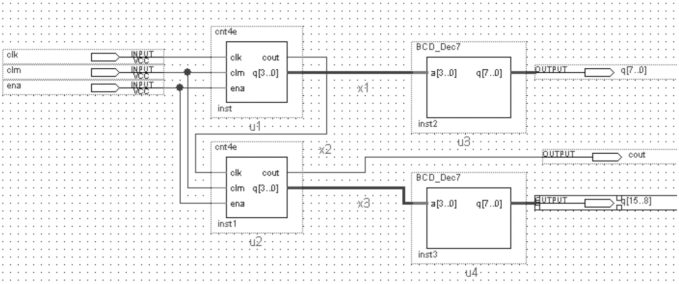

计数译码器系统电路的结构图如图6-29所示,它是用QuartusⅡ的图形编辑方式设计出来的。其中,u1和u2是两个cnt4e元件的例化模块名,相当于cnt4e系统电路板上的插座;u3和u4是Dec7s元件的例化模块名,相当于Dec7s在系统电路板上的插座;x1、x2、x3是电路内部的连线。

图6-29 计数译码器系统电路的结构图

用模块例化方式将cnt4e和Dec7s两种模块组成计数译码器系统电路,用Verilog HDL位置关联法描述的计数译码器电路的顶层源程序文件cnt_dec7s.v如下:

用Verilog HDL名称关联法描述的计数译码器电路的顶层源程序文件cnt_dec7s_1.v如下:

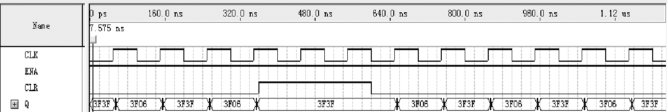

计数译码器系统电路的仿真波形如图6-30所示,其中,数据“3F3F”是电路输出端q[15:0]送给七段数码显示的译码器“00”的数据;“3F06”是显示“01”的数据;依次类推。仿真结果验证了设计的正确性。

图6-30 计数译码器系统电路的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。