Verilog HDL的行为描述是最能体现EDA风格的硬件描述方法,采用它既可以描述简单的逻辑门,也可以描述复杂的数字系统乃至微处理器;既可以描述组合逻辑电路,也可以描述时序逻辑电路。下面再通过几个组合逻辑和时序逻辑电路设计例子,来加深对Verilog HDL行为描述方法的理解。

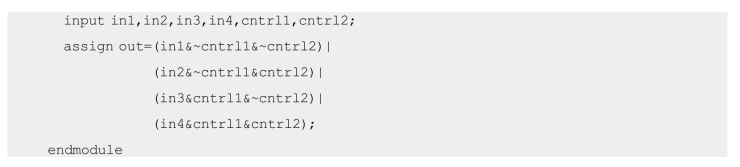

例6-19 逻辑功能描述——算法级:用逻辑表达式描述4选1数据选择器。

module mux4_1(out,in1,in2,in3,in4,cnt r l 1,cnt r l 2);

output out;

注意:

采用算法级描述首先必须根据逻辑功能写出逻辑表达式,再根据表达式进行功能设计。

例6-20 条件运算符描述——算法级:用条件运算符描述4选1数据选择器。用条件运算符描述只需知道输入与输出间的真值表。

module mux4_1(out,in1,in2,in3,in4,cntrl1,cntrl2);

output out;

inputin1,in2,in3,in4,cntrl1,cntr l2;

assign out=cntrl1?(cntrl 2?in4:in3):(cntrl2?in2:in1);

endmodule

注意:

相比调用门级描述,采用逻辑表达式或case语句描述代码更简单,但也更抽象,且耗用器件资源更多。

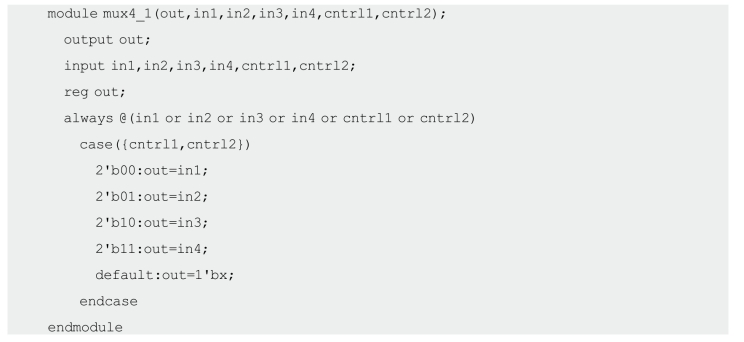

例6-21 case语句描述——系统级:用case语句描述4选1数据选择器。(https://www.daowen.com)

系统级行为描述只需知道输入与输出间的真值表,比调用门级描述和采用逻辑功能描述都简洁。case语句应放在always块内。

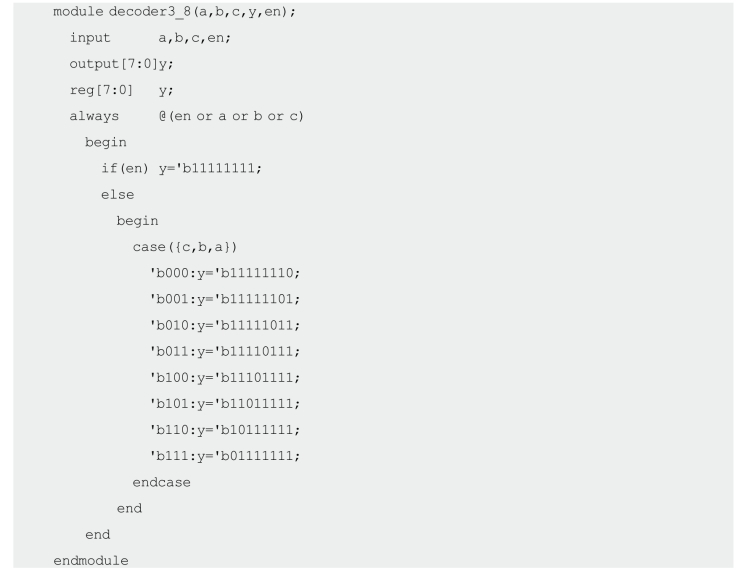

例6-22 if语句描述——系统级:设计3-8译码器。

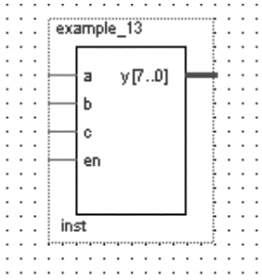

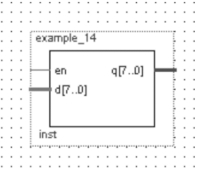

3-8译码器设计电路的元件符号如图6-25所示,en是低电平有效的使能控制输入端,a、b、c是数据输入端,y是8位数据输出端。

图6-25 3-8译码器设计电路的元件符号

3-8译码器设计电路的Verilog HDL源程序decoder3_8.v如下:

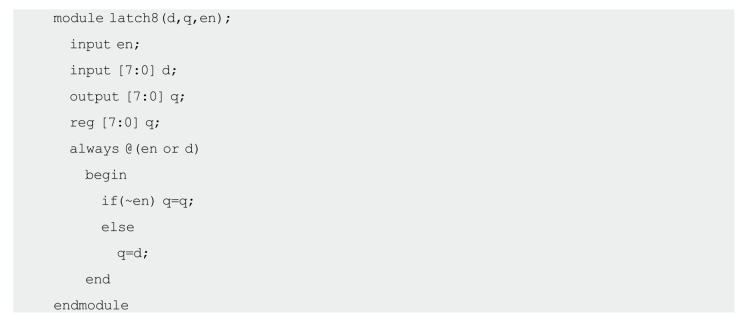

例6-23 if语句描述——系统级:设计8D锁存器。

8D锁存器设计电路的元件符号如图6-26所示,其中d[7..0]是8位数据输入端,q[7..0]是8位数据输出端,en是使能控制输入端。当en=0(无效)时,锁存器的状态不变;当en=1(有效)时,q[7..0]=d[7..0]。

8D锁存器设计电路的Verilog HDL源程序latch8.v如下:

图6-26 8D锁存器设计电路的元件符号

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。