Verilog HDL中有顺序执行语句和并行执行语句之分。Verilog HDL的always块语句与VHDL的process语句类似,always块中的语句是顺序执行语句,按照程序书写的顺序执行。always块本身却是并行执行语句,它与其他always块语句以及assign语句、元件例化语句和initial语句都是同时执行(即并行)的。由于always块语句具有并行行为和顺序行为的双重特性,所以它成为Verilog HDL程序中使用最频繁和最能体现Verilog HDL风格的一种语句。

1.语句的顺序执行

在always块内,逻辑按书写的顺序执行。

always块内的语句是顺序执行语句。

在always块内,若随意颠倒赋值语句的书写顺序,可能导致不同的结果,且应注意,阻塞赋值语句在本语句结束时即完成赋值操作。

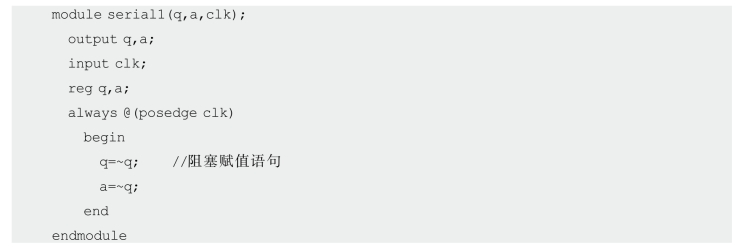

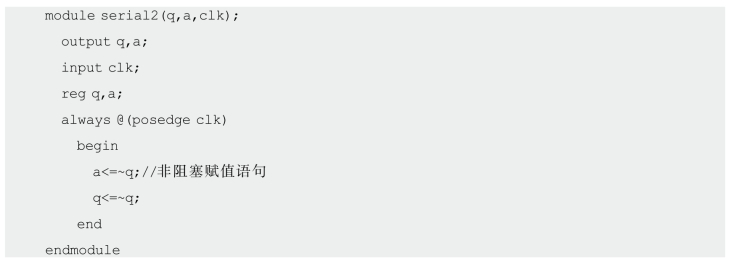

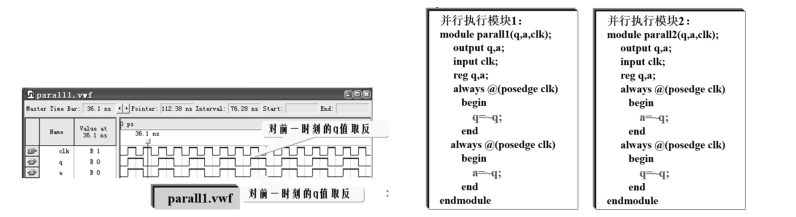

顺序执行模块1:

仿真所得a和q的波形反相,如图6-19所示。

图6-19 模块1仿真图

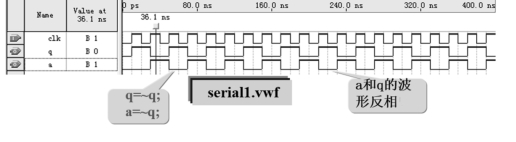

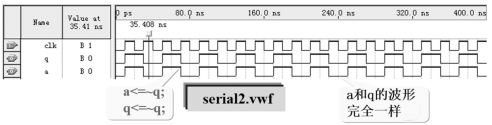

顺序执行模块2:

仿真所得a和q的波形完全相同,如图6-20所示。

图6-20 模块2仿真图

2.语句的并行执行

always块语句、assign语句、元件例化语句都是同时执行(即并行)的,它们在程序中的先后顺序对结果并没有影响。

将两条赋值语句分别放在两个always块中,尽管两个always块顺序相反,但仿真波形完全相同,q和a的波形完全一样,如图6-21所示。

always块语句中有一个敏感变量表,表中列出的任何变量改变,都将启动always块语句,使always块语句内相应的顺序执行语句被执行一次。实际上,用Verilog HDL描述的硬件电路的全部输入变量都是敏感变量,为了使Verilog HDL的软件仿真与综合和硬件仿真对应起来,应当把always块语句中所有输入变量都列入敏感变量表。在时序逻辑电路的编程过程中,时钟变量(clk)和复位变量(clr)是电路变化的主要条件,因此在敏感变量表中,仅列出clk或clr就可以了(其他电平型变量可以不列出)。(https://www.daowen.com)

图6-21 两个always块并行执行

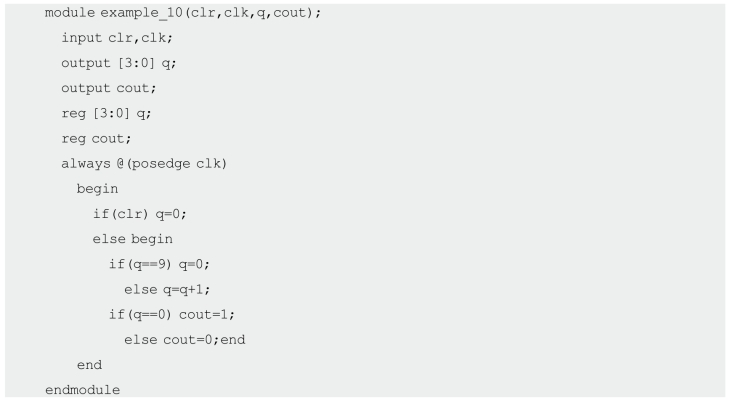

例6-16 描述同步清除十进制加法计数器。

同步清除是指,复位变量有效而且时钟变量的有效边沿到来时,计数器的状态被清零。在本例中,复位变量是clr,高电平有效;时钟变量是clk,上升沿是有效边沿。当clk的上升沿到来时,如果clr有效(为1),则计数器被清零;clr无效时,如果计数器原态是9,计数器回到0态,否则计数器的状态将加1。同步清除十进制加法计数器的Verilog HDL源程序example_10.v如下:

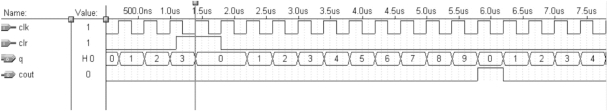

本例设计的计数器的仿真波形如图6-22所示,从仿真结果可以看到,当clk的上升沿到来时,若clr有效(为高电平),计数器被清零。仿真结果验证了设计的正确性。

图6-22 同步清除十进制加法计数器的仿真波形

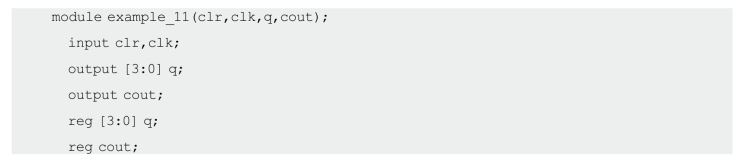

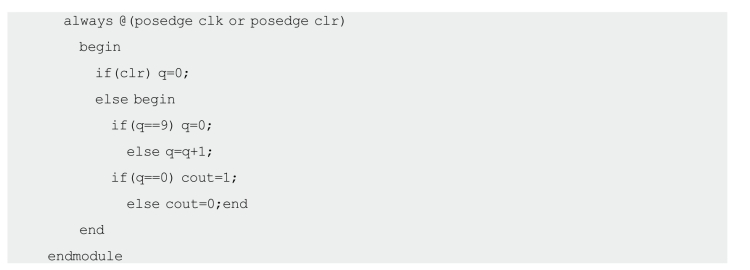

例6-17 描述异步清除十进制加法计数器。

异步清除是指,复位变量有效后计数器的状态立即被清零,与时钟变量无关。在本例中,复位变量是clr,高电平有效;时钟变量是clk,上升沿是有效边沿。当clr=1,计数器被清零;clr无效且clk的上升沿到来时,如果计数器原态是9,计数器回到0态,否则计数器的状态将加1。异步清除十进制加法计数器的Verilog HDL源程序example_11.v如下:

注意:

同步清除十进制加法计数器的源程序(example_10.v)与异步清除十进制加法计数器的源程序(example_11.v)的区别在于:在example_10.v源程序中,复位变量clr不包含在always块的敏感变量表中,因此只有在clk的上升沿到来时,复位语句才能执行,构成同步复位电路;而在example_11.v源程序中,复位信号clr包含在always块的敏感变量表中,因此不受时钟信号的制约,当clr的上升沿到来时电路立即被清除,构成异步复位电路。

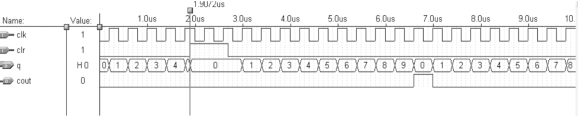

异步清除十进制加法计数器的仿真波形如图6-23所示,可以看出复位信号与时钟信号无关,仿真结果验证了设计的正确性。

图6-23 异步清除十进制加法计数器的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。