编译预处理是Verilog HDL编译系统的一个组成部分。编译预处理语句以符号“‵”开头——注意,不是单引号“’”。

在编译时,编译系统先对编译预处理语句进行预处理,然后将处理结果和源程序一起进行编译。

编译预处理语句主要包括以下几种。

1.‵define语句

‵define语句即宏定义语句——用一个指定的标识符(即宏名)来代表一个字符串(即宏内容)。

格式:

`de f ine标识符(即宏名)字符串(即宏内容)

例如:

`de f ine IN ina+inb+inc+ind

宏展开是指在编译预处理时将宏名替换为字符串的过程。

宏定义的作用:①以一个简单的名字代替一个长的字符串或复杂表达式;②以一个有含义的名字代替没有含义的数字和符号。

宏定义使用说明:

(1)宏名可以用大写字母表示,也可以用小写字母表示;但建议用大写字母,以与变量名相区别。

(2)‵define语句可以写在模块定义的外面或里面。宏名的有效范围为定义命令之后到源文件结束。

(3)在引用已定义的宏名时,必须在其前面加上符号“‵”。

(4)使用宏名代替一个字符串,可简化书写,便于记忆,易于修改。

(5)预处理时只是将程序中的宏名替换为字符串,不管含义是否正确。只有在编译宏展开后的源程序时才可能报错。

(6)宏名和宏内容必须在同一行中进行声明。

(7)宏定义不是Verilog HDL语句,不必在行末加分号。如果加了分号,会连分号一起置换。

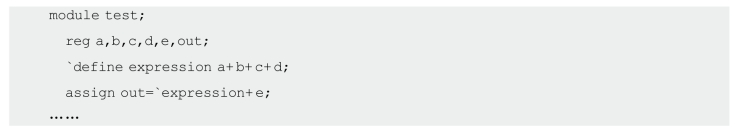

例如:

经过宏展开后,assign语句为

assign out=a+b+c+d;+e; //出现语法错误

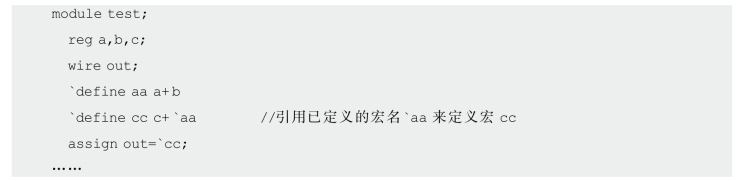

(8)在进行宏定义时,可引用已定义的宏名,实现层层置换。

例如:

经过宏展开后,assign语句为

assign out=c+a+b;

2.‵include语句

‵include语句即文件包含语句——一个源文件可将另一个源文件的全部内容包含进来。格式:

`inc l ude"文件名"

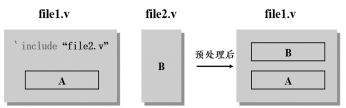

‵include语句实现效果如图6-17所示。预处理后,将file2.v中全部内容复制并插入‵include“file2.v”命令出现的地方。

图6-17 ‵include语句实现效果(https://www.daowen.com)

使用文件包含语句可避免程序设计人员的重复劳动,利用它程序设计人员不必将源代码复制到自己的另一源文件中,使源文件显得简洁。

第一,可以将一些常用的宏定义命令或任务组成一个文件,然后用‵include语句将该文件包含到自己的另一源文件中,相当于将工业上的标准元件拿来使用。

第二,当某几个源文件经常需要被其他源文件调用时,可在其他源文件中用‵include语句将所需源文件包含进来。

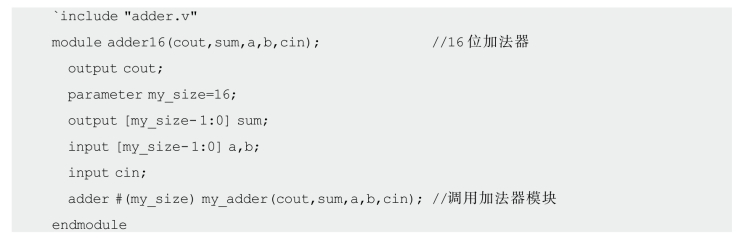

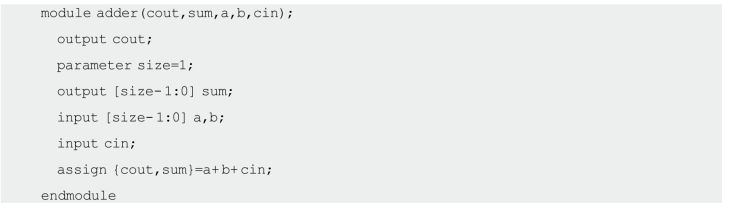

例如,用‵include语句设计16位加法器:

以上语句改变被引用模块adder中的参数size为my_size。被引用的adder模块如下:

关于文件包含语句的说明:

(1)一个‵include语句只能指定一个被包含的文件;若要包含n个文件,需用n个‵include语句。例如:

`include"aaa.v""bbb.v"//非法

`include"aaa.v"

`include"bbb.v"//合法

(2)‵include语句可出现在源程序的任何地方。被包含的文件若与包含文件不在同一子目录下,必须指明其路径。例如:

`include"parts/count.v" //合法

(3)可将多个‵include语句写在一行;在该行中,只可出现空格和注释行。例如:

`include"aaa.v"`include"bbb.v"//合法

(4)文件包含语句允许嵌套。示意图如图6-18所示。

图6-18 文件包含语句嵌套示意图

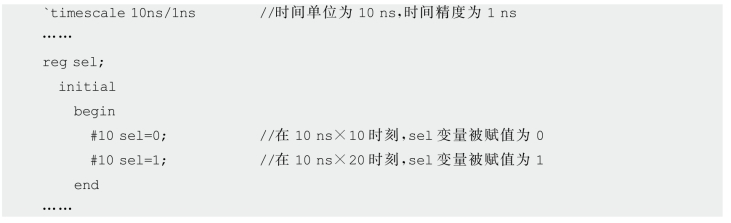

3.‵timescale语句

‵timescale语句即时间尺度语句——用于定义跟在该命令后的模块的时间单位和时间精度。MAX+plusⅡ和QuartusⅡ都不支持该语句,该语句通常用在测试文件中。

格式:

`timescale<时间单位>/<时间精度>

时间单位——用于定义模块中仿真时间和延迟时间的基准单位。

时间精度——用来声明该模块的仿真时间和延迟时间的精确程度。

在同一设计程序里,可以包含采用不同时间单位的模块。此时,用最小的时间精度值决定仿真的时间单位。

时间精度至少要和时间单位一样精确,时间精度值不能大于时间单位值。例如:

`timescale 1ps/1ns //非法

`timescale 1ns/1ps //合法

在‵timescale语句中,用来说明时间单位和时间精度变量值的数字必须是整数。其有效数字为1、10和100。单位为秒(s)、毫秒(ms)、微秒(μs,程序写作us)、纳秒(ns)、皮秒(ps)、毫皮秒(飞秒,fs)。

‵timescale语句应用举例:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。