循环语句包含for语句、repeat语句、while语句和forever语句4种。

for语句通过3个步骤来决定语句的循环执行:

第一步,给控制循环次数的变量赋初值。

第二步,判定循环执行条件,若为假则跳出循环;若为真,则执行指定的语句后,转到下一步。

第三步,修改循环变量的值,返回上一步。

repeat语句:连续执行一条语句n次。

while语句:执行一条语句,直到循环执行条件不满足为止;若一开始条件即不满足,则该语句一次也不能被执行。

forever语句:无限连续地执行语句,可用disable语句中断。

1.for语句

for语句的语法格式为

利用for语句可以使一组语句重复执行,语句中的索引变量、初值、终值和步长值是循环语句定义的参数,这些参数一般属于整型变量或常量。语句重复执行的次数(循环重复次数)由语句中的参数确定,即

循环重复次数=(终值-初值)/步长值

例6-9 设计8位奇偶校验器。

用a表示输入变量,它是一个长度为8位的向量。在程序中,用for语句对a的值逐位进行模2加运算(即异或运算),索引变量n控制模2加的次数。索引变量的初值为0,终值为8,因此,控制循环共执行了8次。8位奇偶校验器的Verilog HDL源程序parity_checker8.v如下:

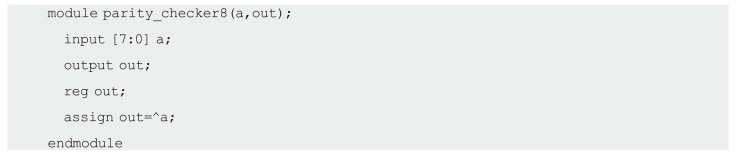

对于一个具体的电路,可以有多种描述方法,例如,8位奇偶校验器可以用缩减异或运算来实现,这种设计非常简单,其源程序parity_checker8.v如下:

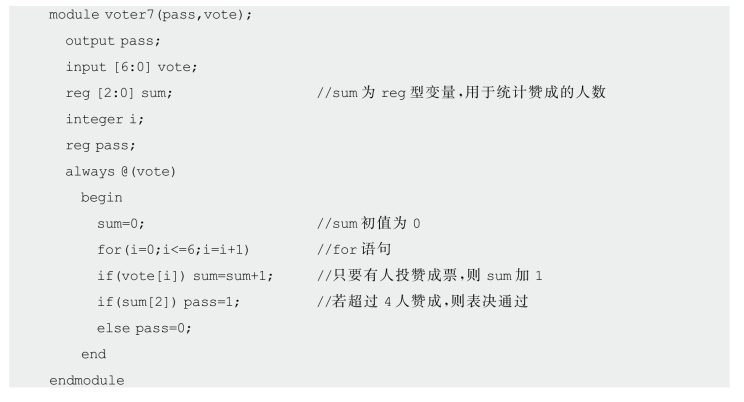

例6-10 设计用for语句描述的7人投票表决器:若超过4人(含4人)投赞成票,则表决通过。

设计的表决器源程序voter.v如下:

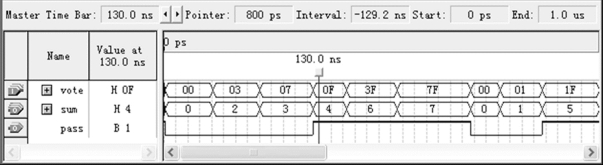

表决器仿真图如图6-16所示。

图6-16 表决器仿真图

2.repeat语句

repeat语句的语法格式为

repeat(循环次数表达式)语句;(https://www.daowen.com)

或

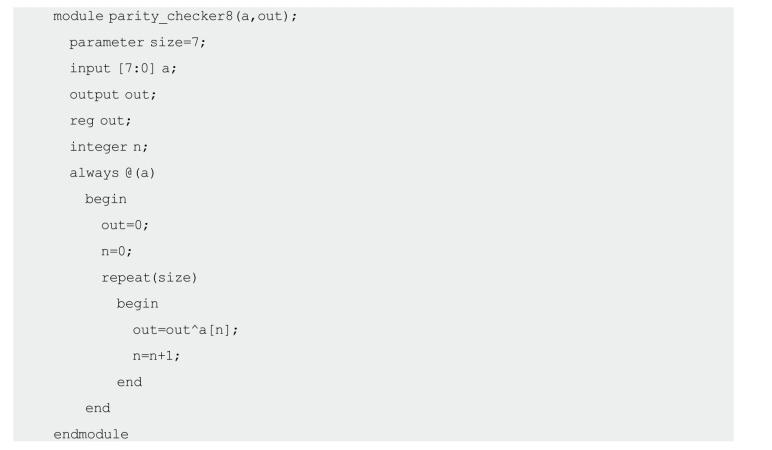

例6-11 用repeat语句实现例6-9(8位奇偶校验器)的描述。

描述如下:

有的EDA工具软件不支持repeat语句,因此将repeat语句视为非法语句。

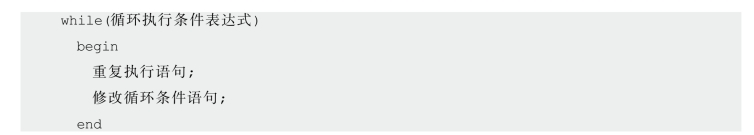

3.while语句

while语句的语法格式为

while语句在执行时,首先判断循环执行条件表达式是否为真。若为真,则执行其后的语句;若为假,则不执行(表示循环结束)。为了使while语句能够结束,在循环执行的语句中必须包含一条能改变循环条件的语句。

注意:

(1)先判断循环执行条件表达式是否为真,若不为真,则其后的语句一次也不被执行。

(2)在执行语句中,必须有一条改变循环执行条件表达式的值的语句。

(3)while语句只有当循环块有事件控制(即@(posedge clock))时才可综合。

例6-12 用while语句对一个8位二进制数中值为1的位进行计数。

思考:

如何用for语句改写此程序?能否找到更简洁的设计方法?

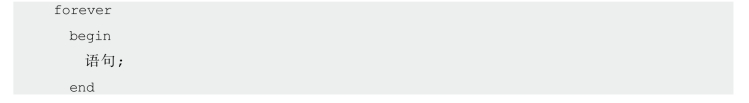

4.forever语句

forever语句的语法格式为

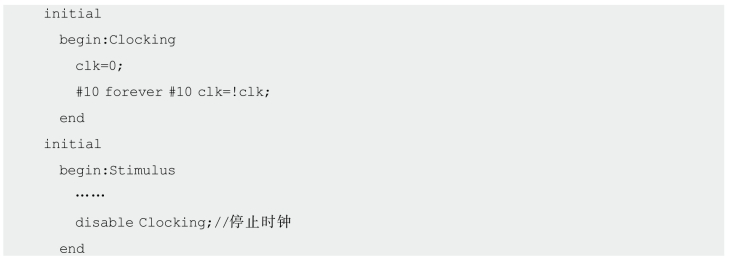

forever是一种无穷循环控制语句,它不断地执行其后的语句或语句块,永远不会结束。一般情况下forever语句是不可综合的,常用在测试文件中。forever语句常用来产生周期性的波形,作为仿真激励变量,常用disable语句跳出循环。

例如,产生的时钟周期为20个延迟单位(纳秒)、占空比为50%的时钟脉冲clk的语句为

注意:

不同于always块语句,forever语句不能独立写在程序中,一般用在initial语句块中。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。