条件语句包含if语句和case语句,它们都是顺序语句,应放在always块或initial块中。

1.if语句

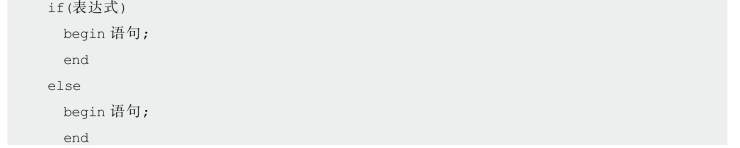

执行if语句时先判定所给条件是否满足,根据判定的结果(真或假)决定执行给出的两种操作之一。完整的Verilog HDL的if语句结构如下:

根据需要,if语句可以写为另外两种变化形式。

第一种:

i f(表达式)

begin语句;

end

第二种:

在if语句中,“表达式”一般为逻辑表达式或关系表达式,也可以是位宽为1位的变量。系统对表达式的值进行判断,若为0、x、z,按“假”处理;若为1,按“真”处理,执行指定的语句。语句可以是多句,为多句时用begin-end语句表述;也可以是单句,为单句时可以省略begin-end语句。对于if语句嵌套,如果不清楚if和else的匹配,最好用begin-end语句表述。

if语句和它的变化形式属于条件语句,在程序中用来改变控制流程。

条件表达式允许采用一定形式的表达式简写方式,如if(expression)等同于if(expression==1),if(!expression)等同于if(expression!=1)。

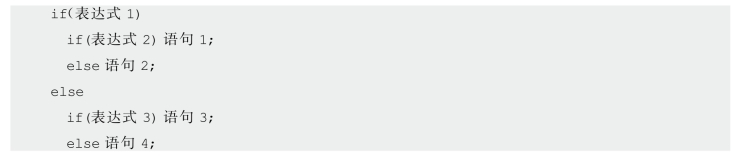

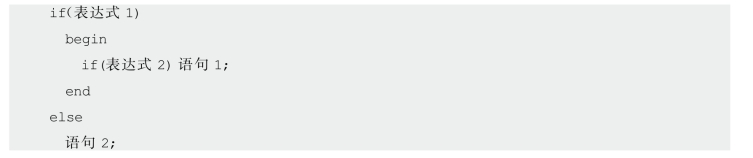

if语句可以嵌套;若if与else的数目不一样,注意用begin-end语句来确定if与else的配对关系。

例如:

又如:

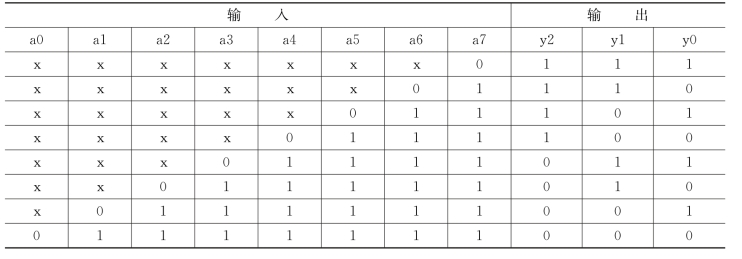

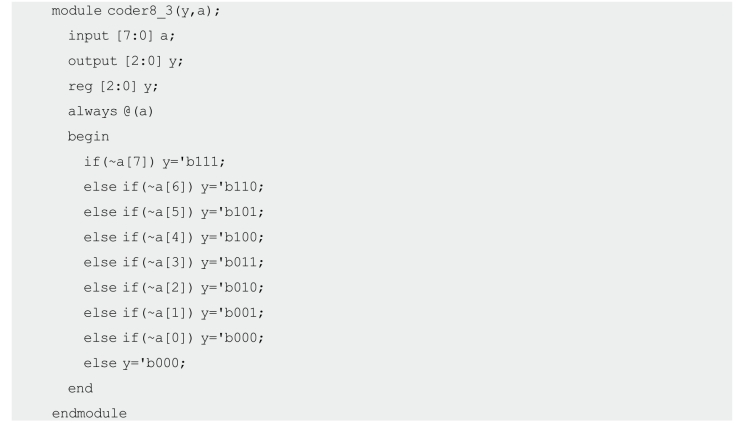

例6-6 设计8-3优先编码器。

8-3优先编码器的功能表如表6-6所示,a0~a7是8个变量输入端,a7的优先级最高,a0的优先级最低。当a7有效时(低电平,为0),其他输入变量无效,编码器输出y2y1y0=111(a7输入的编码);如果a7无效(高电平,为1),而a6有效,则y2y1y0=110(a6输入的编码);依次类推。在传统的电路设计中,优先编码器的设计是一个相对困难的课题,而采用Verilog HDL的if语句,此类难题迎刃而解,这充分体现了硬件描述语言在数字电路设计方面的优越性。

表6-6 8-3优先编码器的功能表

8-3优先编码器设计电路的Verilog HDL源程序coder8_3.v如下:

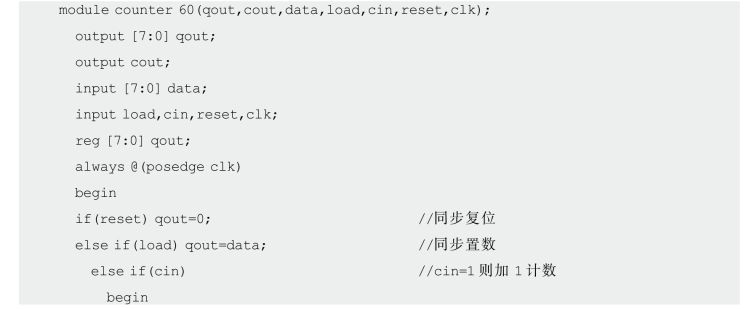

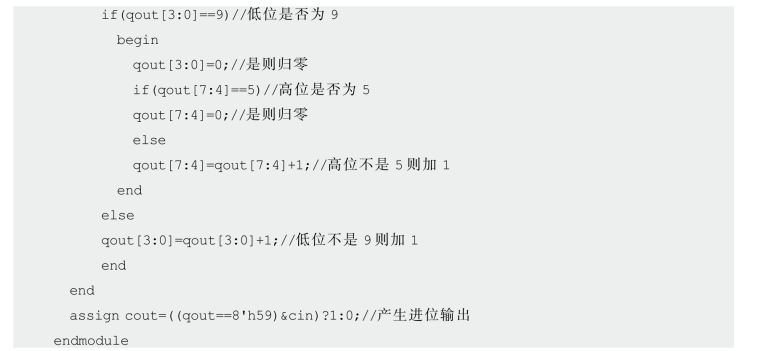

例6-7 编写模为60的BCD码加法计数器源程序counter60.v。

计数器仿真图如图6-12所示,该计数器的置数功能、加计数功能和进位输出功能可通过Quartus软件仿真输出。

图6-12 计数器仿真图

在always块内的语句是顺序执行的,always块语句和assign语句是并行执行的。

注意:

if(reset)qout=0;

else if(load)qout=data;(https://www.daowen.com)

else if(cin)

……

不要写成3个并列的if语句:

if(reset)qout=0;

if(load)qout=data;

if(cin)

……

写成3个并列的if语句是同时对3个信号(reset、load和cin)进行判断,现实中很可能出现三者同时为“1”的情况,即3个条件同时满足,此时会执行它们对应的执行语句,但3条执行语句是对同一个信号qout赋不同的值,显然相互矛盾,故编译时会报错。modu le mux4_1(y,a,b,c,d,s1,s2); input s1,s2;

2.case语句

case语句是一种多分支的条件语句,当敏感表达式取不同的值时,执行不同的语句。

功能:当某个(控制)信号取不同的值时,给另一个(输出)信号赋不同的值。case语句常用于多条件译码电路(如译码器、数据选择器、状态机、微处理器的指令译码)设计。

完整的case语句的格式为

其中“敏感表达式”又称为控制表达式,通常表示为控制信号的某些位。“值1”~“值n”称为分支表达式,用控制信号的具体状态值表示,因此又称为常量表达式。某些case语句中default项可有可无,一个case语句里最多只能有一个default项。

分支表述式必须互不相同,否则矛盾;位宽必须相等,且与控制表达式的位宽相同。

执行case语句时,首先计算表达式的值,然后执行在条件语句中找到的与其值相同的“选择值”对应的语句。当所有的条件语句的“选择值”与表达式的值不同时,执行“default”后的语句。当“选择值”涵盖了表达式的全部结果(如表达式是3位二进制数,而“选择值”有8个)时,default语句可以不要;不满足上述条件时,default语句不可缺省。

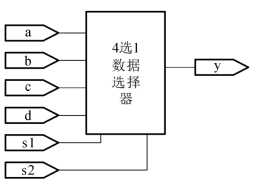

图6-13 4选1数据选择器逻辑符号

例6-8 用case语句描述4选1数据选择器。

4选1数据选择器的逻辑符号如图6-13所示,其功能表如表6-7所示。由表6-7可知,4选1数据选择器的功能是,在控制输入变量s1和s2的条件下,使输入数据变量a、b、c、d中的一个被选中并传送到输出y。s1和s2有4种组合值,可以用case语句实现其功能。

表6-7 4选1数据选择器功能表

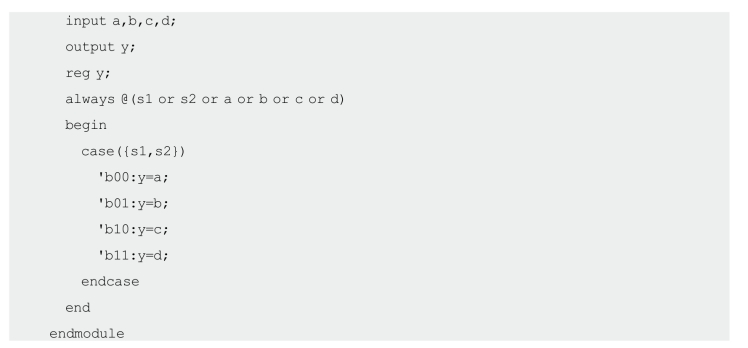

4选1数据选择器Verilog HDL源程序如下:

case语句还有两种变体形式,即casez和casex语句。casez和casex语句与case语句的格式完全相同,它们的区别是:在casez语句中,如果分支表达式某些位的值为高阻z,那么对这些位的比较结果就不予以考虑,只关注其他位的比较结果;在casex语句中,把不予以考虑的位扩展到未知x,即不考虑值为高阻z和未知x的那些位的比较结果,只关注其他位的比较结果。在分支表达式中,可用“?”来标识x或z。用casez语句描述的数据选择器如下:

3.使用条件语句注意事项

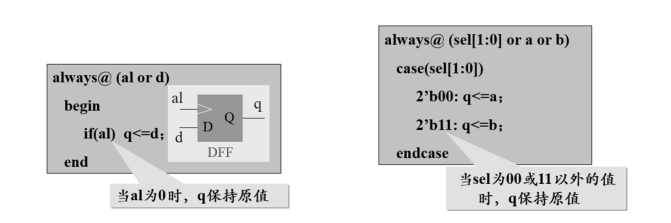

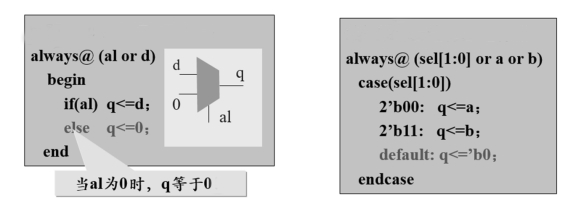

使用条件语句时应注意列出所有条件分支,否则当条件不满足时,编译器会生成一个锁存器保持原值。这一点可用于设计时序电路,如计数器(条件满足时加1,否则保持原值不变)。在组合电路设计中,应避免生成隐含锁存器,有效的方法是在if语句最后写上else项,在case语句最后写上default项。

图6-14所示为生成不想要的锁存器的例子。

图6-14 生成不想要的锁存器的例子

图6-15所示为不会生成锁存器的例子。

图6-15 不会生成锁存器的例子(设计数据选择器)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。