在Verilog HDL中,赋值语句常用于描述硬件设计电路输出与输入之间的信息传送,改变输出结果。Verilog HDL有门基元赋值、连续赋值、过程赋值等赋值方法(即语句),不同的赋值语句使输出产生新值的方法不同。

1.门基元赋值语句

门基元赋值语句也称为元件例化语句,其格式为

基本逻辑门关键字(门输出,门输入1,门输入2,…,门输入n);

其中,基本逻辑门关键字是Verilog HDL预定义的逻辑门,包括and、or、not、xor、nand、nor等;圆括号中的内容是被描述门的输出和输入变量。

例如,具有a、b、c、d四个输入、y为输出的与非门的门基元赋值语句为

nand mynand4(y,a,b,c,d);

//该语句与assign y=~(a&b&c&d);等效

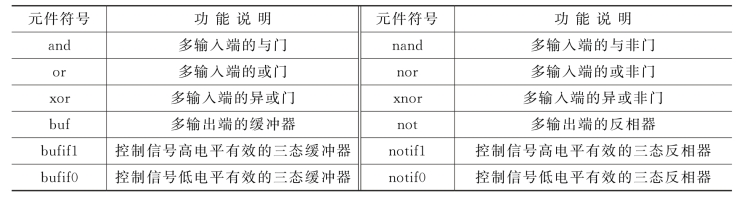

基本门级元件如表6-5所示。

表6-5 基本门级元件

基本门级元件按输入输出方式分类如下:

(1)多输入门:只允许有一个输出,但可以有多个输入。

例如:

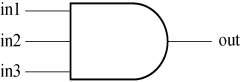

and A1(out,in1,in2,in3);

对应的三输入与门元件模型如图6-8所示。

(2)多输出门:允许有多个输出,但只有一个输入。

例如:

not N1(out1,out2,…,in);

bu f B1(out1,out2,…,in);

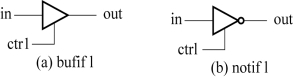

(3)三态门:有一个输出、一个数据输入和一个输入控制。如果输入控制信号无效,则三态门的输出为高阻态z。

例如:

bu f i f1 B1(out,in,c t r l);

not i f1 N1(out,in,c t r l);

相应的三态门元件模型如图6-9所示。

图6-8 三输入与门元件模型

图6-9 三态门元件模型

2.连续赋值语句

连续赋值语句的关键字是assign,赋值符号是“=”,赋值语句的格式为

assign赋值变量=表达式;

例如,具有a、b、c、d四个输入、y为输出的与非门的连续赋值语句为

assign y=~(a&b&c&d);

连续赋值语句的“=”号左边的变量y应该是wire型变量,而右边的变量可以是reg型或者wire型变量。在执行过程中,输出y跟随输入a、b、c、d的变化而变化,反映了信息传送的连续性。连续赋值语句用于逻辑门和组合逻辑电路的描述。

例6-4 编写4输入端与非门的Verilog HDL源程序。

modu leexamp l e_4(y,a,b,c,d);

outputy;

input a,b,c,d;(www.daowen.com)

assigny=~(a&b&c&d);

endmodu l e

3.过程赋值语句

过程赋值语句用于对reg型变量赋值,有两种赋值方式:

第一种,阻塞(blocking)赋值方式。赋值符号为“=”,如:

b=a;

第二种,非阻塞(non-blocking)赋值方式。赋值符号为“<=”,如:

b<=a;

1)阻塞赋值语句

阻塞赋值语句出现在initial块语句和always块语句中,它是顺序语句,语句格式为

赋值变量=表达式;

在阻塞赋值语句中,赋值符号“=”左边的赋值变量必须是reg型(寄存器型)变量,其值在该语句结束即可得到。如果一个块语句中包含若干条阻塞赋值语句,那么这些阻塞赋值语句是按照语句编写的顺序由上至下一条一条地执行的,前面的语句没有完成,后面的语句就不能执行,如同被阻塞了一样。

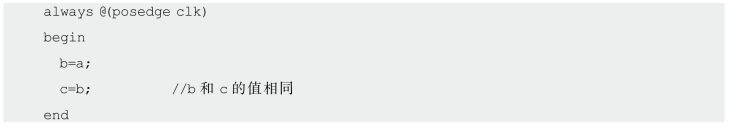

例如:

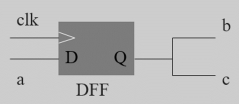

示意图如图6-10所示。

2)非阻塞赋值语句

非阻塞赋值语句也出现在initial块语句和always块语句中,赋值符号是“<=”,语句格式为

赋值变量<=表达式;

在非阻塞赋值语句中,赋值符号“<=”左边的赋值变量也必须是reg型变量,其值不像在阻塞赋值语句中那样在语句结束时即可得到,而是在该块语句结束时才可得到。

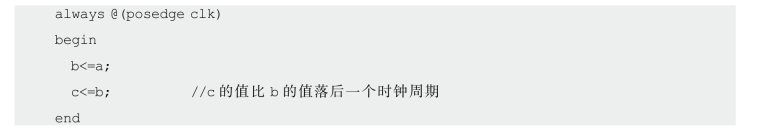

例如:

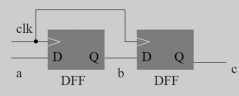

示意图如图6-11所示。

图6-10 阻塞赋值语句示意图

图6-11 非阻塞赋值语句示意图

3)阻塞赋值与非阻塞赋值的主要区别

(1)非阻塞赋值方式(b<=a):

b被赋成新值a的操作并不是立刻完成的,而在块语句结束时才完成;块语句内的多条赋值语句在块语句结束时同时赋值;硬件有对应的电路。

(2)阻塞赋值方式(b=a):

b的值立刻被赋成新值a;完成该赋值语句后才能执行下一句的操作;硬件没有对应的电路,因而综合结果未知。

建议在初学时只使用一种方式,不要混用,建议在可综合风格的模块中使用非阻塞赋值语句。

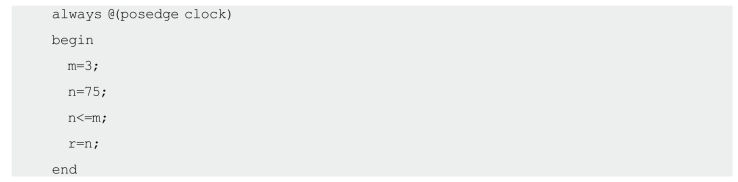

例如,在下面的块语句中包含4条赋值语句,语句执行结束后,r的值是75,而不是3,因为第3行是非阻塞赋值语句“n<=m”,所以要等到本块语句结束时n的值才能改变。块语句中的“@(posedge clock)”是定时控制敏感函数,表示时钟变量clock的上升沿到来的敏感时刻。

阻塞赋值语句和非阻塞赋值语句都是在initial块语句和always块语句中使用的,因此都称为过程赋值语句,只是赋值方式不同。过程赋值语句常用于数字系统的触发器、移位寄存器、计数器等时序逻辑电路的描述,也可用于组合逻辑电路的描述。

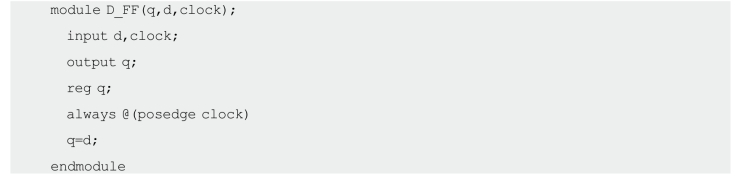

例6-5 编写上升沿触发的D触发器的Verilog HDL源程序。

在源程序中,q是触发器的输出,属于reg型变量;d和clock是输入,属于wire型变量(由隐含规则定义)。在always块语句中,“posedge clock”是敏感变量,只有clock的正边沿(上升沿)到来,D触发器的输出q才等于d,否则触发器的状态不变(处于保持状态)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。