Verilog HDL数据对象是指用来存放各种类型数据的容器,包括常量和变量。

1.常量

常量是一个恒定不变的值,一般在程序前部定义。常量定义格式为

parameter常量名1=表达式,常量名2=表达式,…,常量名n=表达式;

其中,parameter是常量定义关键字,常量名是用户定义的标识符,表达式是为常量赋的值。例如:

parameter Vcc=5,f bus=8'b11010001;

上述语句定义了常量Vcc的值为十进制数5,常量fbus的值为二进制数8’b11010001。

每个赋值语句的等号右边必须为常数表达式,即只能包含数字或先前定义过的符号常量。

parameter add rwid th=16; //合法格式

parameter addrwidth=datawidth*2;//非法格式

常用参数来定义延迟时间和变量宽度。

可用字符串表示的任何地方,都可以用定义的参数来代替。

参数是本地的,其定义只在本模块内有效。

在引用模块或实例时,可通过参数传递改变在被引用模块或实例中已定义的参数。

2.变量

变量是在程序运行时其值可以改变的量。在Verilog HDL中,变量分为网络型(nets type)和寄存器型(register type)两种。

1)网络型变量

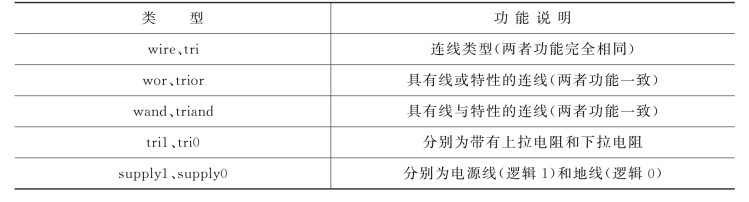

网络型变量又称nets型变量,是输出值始终根据输入变化而更新的变量,它一般被用来定义硬件电路中的各种物理连线。Verilog HDL提供了多种nets型变量,如表6-3所列。

表6-3 常用的nets型变量及说明

在nets型变量中,wire型变量是最常用的一种。wire型变量常用来表示以assign语句赋值的组合逻辑变量。Verilog HDL模块中的输入/输出变量类型缺省时将被自动定义为wire型。wire型变量可以作为任何方程式的输入,也可以作为assign语句和元件例化的输出。综合而言,wire型变量的取值可以是0、1、x和z。

wire型变量的定义格式如下:

![]()

例如:

wi re a,b,c; //定义了3个wi re型变量,位宽均为1位

wi re[7:0]databus;//定义了1个wi re型数据总线,位宽为8位

wi re[15:0]add rbus;//定义了1个wi re型地址总线,位宽为16位

2)寄存器型变量

寄存器型变量又称register型变量,对应具有状态保持作用的电路元件(如触发器、寄存器等),常用来表示过程块语句(如initial、always、task、function)内的指定信号。它作为一种数值容器,不仅可以容纳当前值,也可以保持历史值,这一属性与触发器或寄存器的记忆功能有很好的对应关系。register型变量也是一种连接线,可以作为设计模块中各器件间的信息传送通道。

register型变量与wire型变量的根本区别在于register型变量需要被明确地赋值,并且在被重新赋值前一直保持原值。wire型变量在assign语句中和元件例化时赋值,而register型变量在always、initial等过程语句中赋值。register型变量必须通过过程赋值语句赋值,不能通过assign语句赋值,在过程块内被赋值的每个信号必须定义成寄存器型。

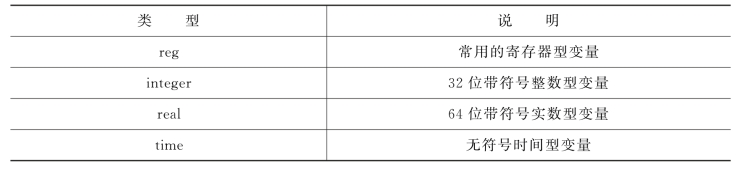

Verilog HDL中常用的register型变量有4种,如表6-4所列。

表6-4 常用的register型变量及说明

integer、real和time 3种寄存器型变量都是纯数学的抽象描述(不可综合),不对应任何具体的硬件电路,但它们可以描述与模拟有关的计算。例如,可以利用time型变量控制经过特定的时间关闭显示等。

reg型变量是可综合的数字系统中存储设备的抽象,常用于具体的硬件描述,因此是最常用的寄存器型变量。下面重点介绍reg型变量。

reg型变量定义的关键字是reg,定义格式如下:

reg[位宽]变量1,变量2,…,变量n;

用reg定义的变量有一个范围选项(即位宽),默认的位宽是1位。位宽为1位的变量称为标量,位宽超过1位的变量称为向量。标量的定义不需要加位宽选项,例如:(https://www.daowen.com)

reg a,b; //定义两个reg型标量a,b

定义向量时需要加位宽选项,例如:

reg[7:0]data; //定义1个8位reg型变量,最高有效位是7,最低有效位是0

reg[0:7]data; //定义1个8位reg型变量,最高有效位是0,最低有效位是7

向量定义后可以有多种使用形式(即赋值):

①为整个向量赋值的形式为

data=8'b00000000;

②为向量的部分位赋值的形式为

data[5:3]=3'b111; //将data的第3~5位赋值为“111”

③为向量的某一位赋值的形式为

data[7]=1'b1;

在过程块中被赋值的reg信号,往往代表触发器,但不一定就是触发器(也可以是组合逻辑信号)。利用reg型变量既可生成触发器,也可生成组合逻辑;利用wire型变量只能生成组合逻辑。

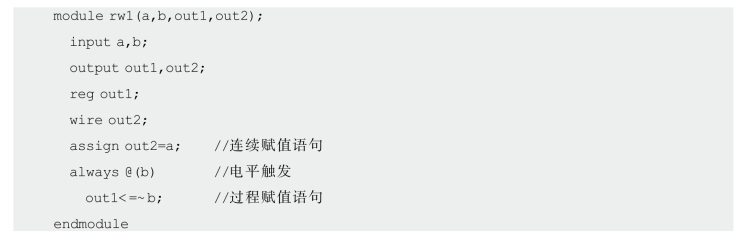

用reg型变量生成组合逻辑举例:

其示意图如图6-6所示。

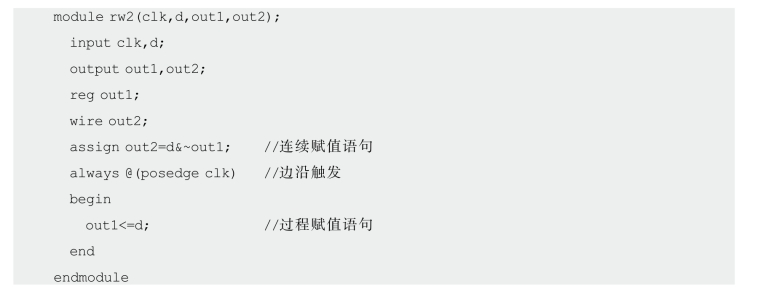

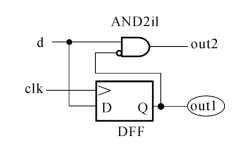

用reg型变量生成触发器举例:

其示意图如图6-7所示。

图6-6 用reg型变量生成组合逻辑示意图

图6-7 用reg型变量生成触发器示意图

3)存储器型变量

若干个相同宽度的向量构成数组。在数字系统中,reg型数组变量即为存储器型变量。存储器型变量可以用如下语句定义:

reg[7:0]mymemory[511:0];

上述语句定义了一个512字存储器型变量mymemory,每个字的字长为8位。可以用下面的语句来使用该存储器型变量:

mymemory[7]=75; //存储器型变量mymemory的第7个字被赋值75

存储器型变量又称memory型变量,与reg型变量的区别在于,一个n位的寄存器可用一条赋值语句赋值,一个完整的存储器则不行。若要对某存储器中的存储单元进行读写操作,必须指明该单元在存储器中的地址。

例如:

reg[n-1:0]rega; //一个n位的寄存器

reg mema[n-1:0]; //由n个1位寄存器组成的存储器

又如:

rega=0; //合法赋值语句

mema=0; //非法赋值语句

mema[8]=1; //合法赋值语句

mema[1023:0]=0; //合法赋值语句,必须指明存储单元的地址

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。