操作符也称为运算符,是Verilog HDL预定义的函数名字,这些函数对被操作的对象(即操作数)进行规定的运算,得到一个结果。操作符通常由1~3个字符组成,例如,“+”表示加操作,“==”(两个=字符)表示逻辑等操作,“===”(3个=字符)表示全等操作。有些操作符的操作数只有1个,称为单目操作;有些操作符的操作数有2个,称为双目操作;有些操作符的操作数有3个,称为三目操作。

Verilog HDL的操作符分为算术操作符、逻辑操作符、位运算操作符、关系操作符、等值操作符、缩减操作符、转移操作符、条件操作符和并接操作符9类。

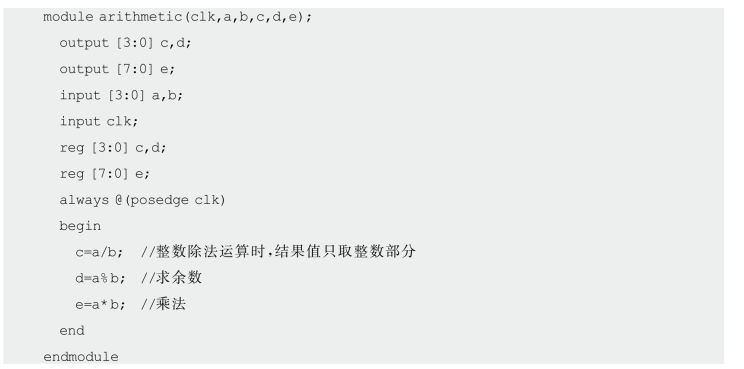

1.算术操作符(arithmetic operators)

常用的算术操作符有+(加)、-(减)、*(乘)、/(除)、%(求余)和**(乘方)6种。其中%是求余操作符,在两个整数相除的基础上,取出其余数。例如:5%6的值为5;13%5的值是3。整除(/)和求余(%)运算符可以方便电路的设计,如将二进制数转换为十进制数,但这两种运算符在综合过程中会占用很多逻辑单元,所以一般电路设计最好不要使用。算术操作符的示例如下:

2.逻辑操作符(logical operators)

逻辑操作符包括&&(逻辑与)、||(逻辑或)和!(逻辑非)。例如,A&&B表示A和B进行逻辑与运算;A||B表示A和B进行逻辑或运算;!A表示对A进行逻辑非运算。该类操作符常用于条件语句的判断条件中,示例如下:

always@(a or b)

begin

if(a&&b)c=1;

else c=0;

end

3.位运算操作符(bitwise operators)

位运算是将两个操作数按对应位进行逻辑操作。位运算操作符包括~(按位取反)、&(按位与)、|(按位或)、(按位异或)、~或~(按位同或)。例如,设A=’b11010001,B=’b00011001,则相关位运行结果如下:

~A='b00101110

A&B='b00010001

A|B='b11011001

A^B='b11001000

A^~B='b00110111

在进行位运算时,两个操作数的位宽不同,计算机会自动将两个操作数按右端对齐,位数少的操作数会在高位用0补齐。

位运算与逻辑操作符运算的结果是相同的,因此,逻辑操作运算可以直接用位运算替代,例如,A&&B可以写成A&B。

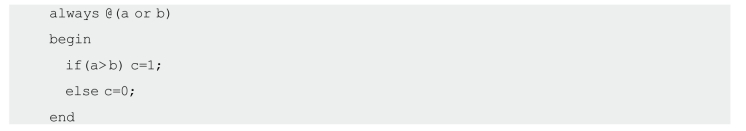

4.关系操作符(relational operators)

关系操作符用来对两个操作数进行比较。关系操作符有<(小于)、<=(小于等于)、>(大于)和>=(大于等于)。其中,<=也是赋值运算的赋值符号。

关系运算的结果是1位逻辑值。在进行关系运算时,如果关系是真,则计算结果为1;如果关系是假,则计算结果为0;如果某个操作数的值不定,则计算结果不定(为未知值x),表示结果是模糊的。该类操作符常用于条件语句的判断条件中。例如:

5.等值操作符(equality operators)

等值操作符包括==(相等)、!=(不等于)、===(全等)、!==(不全等)4种。

等值运算的结果也是1位逻辑值:当运算结果为真时,返回值1;为假则返回值0。相等操作符(==)与全等操作符(===)的区别是:进行相等运算时,两个操作数必须逐位相等,其比较结果的值才为1(真),如果某些位是不定或高阻状态,其相等比较的结果就会是不定值;而进行全等运算时,对不定或高阻状态位也进行比较,两个操作数完全一致时,其结果的值才为1(真),否则结果的值为0(假)。

例如,设A=’b1101xx01,B=’b1101xx01,则A==B运算的结果为x(未知),A===B运算的结果为1(真)。

该操作符常用于条件语句的判断条件中,例如:

6.缩减操作符(reduction operators)

缩减操作符包括&(与)、~&(与非)、|(或)、~|(或非)、(异或)、~或~(同或)。缩减操作运算法则与逻辑运算操作相同,但运算对象只有一个。在进行缩减操作运算时,对操作数进行与、与非、或、或非、异或、同或等缩减操作运算,运算结果是1位——“1”或“0”。例如,设A=’b11010001,则&A=0(在与缩减运算中,只有A中的数字全为1时,结果才为1);|A=1(在或缩减运算中,只有A中的数字全为0时,结果才为0)。缩减操作相当于一个逻辑门,与缩减运算相当于一个与门,只有与门的全部输入为“1”时,输出(1位)才为“1”,否则输出为“0”。

缩减操作符是对单个操作数进行递推运算,即先将操作数的最低位与第二位进行与、或、非运算,再将运算结果与第三位进行相同的运算,依次类推,直至最高位。运算结果缩减为1位二进制数。例如:

reg[3:0]a;

b=|a; //等效于b=((a[0]|a[1])|a[2])|a[3]

7.转移操作符(shift operators)

转移操作符包括>>(右移)和<<(左移)。其使用方法为

操作数>>n; //将操作数的内容右移n位,同时从左边开始用0来填补移出的位数

操作数<<n; //将操作数的内容左移n位,同时从右边开始用0来填补移出的位数(https://www.daowen.com)

例如,设A=’b11010001,则A>>4的结果是A=’b00001101,而A<<4的结果是A=’b00010000。

8.条件操作符(conditional operators)

条件操作符为?:。

条件操作符的操作数有3个,其使用格式为

操作数=条件?表达式1:表达式2;

即当条件为真(条件结果值为1)时,操作数=表达式1;为假(条件结果值为0)时,操作数=表达式2。

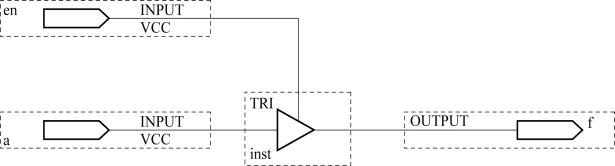

例6-3 用Verilog HDL的条件操作符设计三态输出电路。

三态输出电路如图6-4所示,其中a是1位数据输入端,f是1位数据输出端,en是使能控制输入端,高电平有效。当en=1时,电路工作,输出f=a;当en=0时,电路不工作,输出为高阻态(f=’bz)。

图6-4 三态输出电路(例6-3的硬件实现电路)

用Verilog HDL的条件操作符设计三态输出电路的源程序如下:

module tri_v(f,a,en);

input a,en;

out put f;

assign f=en?a:'bz;

endmodule

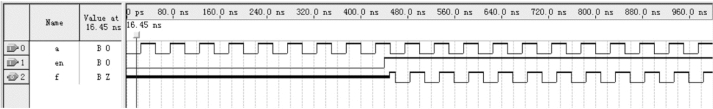

在例6-3中用了一个含有“?:”条件操作符的“assign f=en?a:’bz;”语句来描述三态输出电路,assign语句的条件是变量en,其值只有0和1两种。当en为1(真)时y=a,为0(假)时则y=’bz(高阻态)。三态输出电路的仿真波形如图6-5所示。在波形图中,当en=0时输出f为高阻态(高阻态以在高、低电平中部的粗线表示);当en=1时,输出f与输入a的波形相同。

图6-5 三态输出电路的仿真波形

9.并接操作符(concatenationoperators)

并接操作符为{}。并接操作符的使用格式为

{操作数1的某些位,操作数2的某些位,…,操作数n的某些位};

即将操作数1的某些位、操作数2的某些位直至操作数n的某些位并接在一起,构成一个由这些数组成的多位数,当作一个整体信号。

例如,将1位全加器进位cout与求和sum并接在一起使用,它们的结果由两个加数a、b及低位进位cin相加决定,表达式为

assign{cout,sum}=a+b+cin;

又如,{a,b[3:0],w,3’b101}等同于{a,b[3],b[2],b[1],b[0],w,1’b1,1’b0,1’b1}。

可用重复法简化表达式,如{4{w}}等同于{w,w,w,w}。

还可用嵌套方式简化书写,如{b,{3{a,b}}}等同于{b,{a,b},{a,b},{a,b}},也等同于{b,a,b,a,b,a,b}。

在位并接表达式中,不允许存在没有指明位数的信号,必须指明信号的位数;若未指明,则默认为32位的二进制数。例如,{1,0}等同于64’h00000001_00000000。

注意:

{1,0}不等于2’b10。

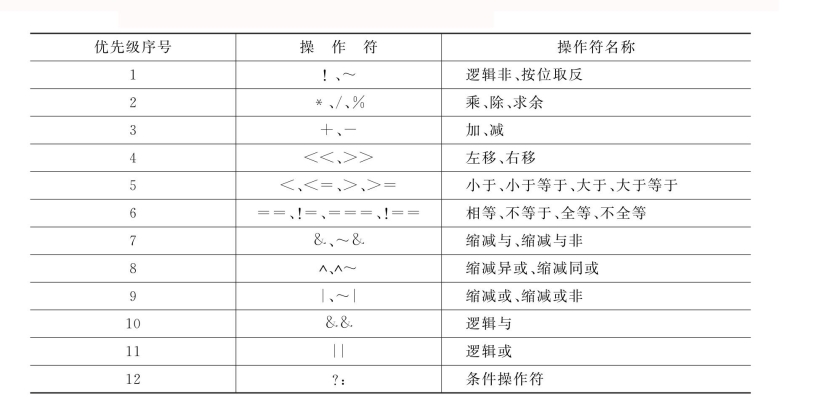

10.操作符的优先级

操作符的优先级如表6-2所示,表中顶部的操作符优先级最高,底部的最低,列在同一行的操作符的优先级相同。几乎所有的操作符(?:除外)在表达式中都是从左向右结合的。圆括号可以用来改变优先级,并使运算顺序更清晰,对操作符的优先级不能确定时,最好使用圆括号来确定表达式的优先顺序,既可以避免出错,也可以增加程序的可读性。例如:

(a>b)&&(b>c);

(a==b)||(x==y);

(!a)||(a>b);

表6-2 操作符的优先级

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。