模块内容包括模块的I/O声明、变量类型声明和功能描述。

1.模块的I/O声明

模块的I/O声明用来声明模块端口定义中各端口数据流动方向,包括输入(input)、输出(output)和双向(inout)。I/O声明格式如下:

input端口1,端口2,端口3,…; //声明输入端口

out put端口1,端口2,端口3,…;//声明输出端口

例如,1位全加器的I/O声明为

input a,b,cin;

out put sum,cout;

2.变量类型声明

变量类型声明用来声明设计电路的功能描述中所用的变量的数据类型和函数。变量的类型主要有连线(wire)、寄存器(reg)、整型(integer)、实型(real)和时间(time)等。例如:

wire a,b,cin; //声明a,b,cin是wire型变量

reg cout; //声明cout是reg型变量

reg[7:0]q; //声明q是8位reg型变量

在Verilog HDL的2001年版本或以上版本,允许将I/O声明和变量类型声明放在一条语句中,例如:

output reg[7:0]q;//声明q是8位reg型输出变量

变量声明部分内容将在后续的章节中详细介绍。

3.功能描述

功能描述是Verilog HDL程序设计中最主要的部分,用来描述设计模块的内部结构和模块端口间的逻辑关系,在电路上相当于实现器件的功能或定义内部电路结构。功能描述可以用assign语句、元件例化、always块语句、initial块语句等方法来实现,通常把确定这些设计模块功能描述的方法称为建模。

1)用assign语句建模

用assign语句建模很简单,只需要在“assign”后面加一个表达式即可。assign语句一般适合用于对组合逻辑进行赋值,此赋值方式称为连续赋值方式。

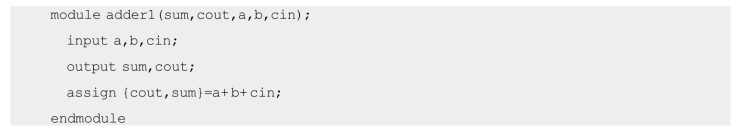

例6-1 设计1位全加器。

1位全加器的逻辑符号如图6-2所示,其中sum是全加器的求和输出端,cout是进位输出端,a和b是两个加数输入端,cin是低位进位输入端。

图6-2 1位全加器的逻辑符号

全加器设计电路的Verilog HDL源程序adder1.v如下:

在例6-1中,用语句“assign{cout,sum}=a+b+cin;”实现1位全加器的进位输入cout与和输出sum的建模。在语句表达式中,用并接运算符“{}”将cout、sum这两个1位操作数并接为一个2位操作数,位于左边的操作数的权值高,位于右边的操作数的权值低。

2)用元件例化方式建模

用元件例化方式建模是利用Verilog HDL提供的元件库实现的。例如,用与门例化元件定义一个3输入端与门可以写为

and myand3(y,a,b,c);

其中:and是Verilog HDL元件库中“与门”元件名,属于关键字;myand3是可选的自定义例化名(可以忽略);y是与门的输出端,a、b和c是输入端。

注意:(https://www.daowen.com)

(1)元件例化就是调用Verilog HDL提供的元件。

(2)元件例化包括门元件例化和模块元件例化。

(3)每个实例元件的名字必须唯一,以避免与其他调用元件的实例相混淆。

(4)例化元件名也可以省略。

3)用always块语句建模

always块语句可以用于设计组合逻辑和时序逻辑;时序逻辑必须用always块语句来建模。一个程序设计模块中可以包含一个或多个always块语句。程序运行过程中,某种条件每满足一次,就执行一遍always结构中的语句。

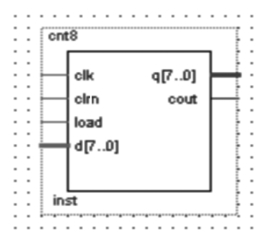

图6-3 8位二进制加法计数器的逻辑符号

例6-2 设计8位二进制加法计数器。

用Verilog HDL设计的8位二进制加法计数器的元件符号如图6-3所示,其中:q是8位二进制计数器的输出端(8位向量);cout是进位输出端(1位);d是并行数据输入端(8位向量);clk是时钟控制输入端,上升沿为有效边沿;clrn是同步复位输入端,低电平有效,当clk的上升沿到来且clrn=0时,计数器被复位,q=0;load是计数器的预置控制输入端,当clk的上升沿到来时,若load=1(有效),q=d。

8位二进制加法计数器的Verilog HDL源程序cnt8.v如下:

在例6-2的源程序中,用always块语句来实现8位二进制加法计数器的建模。

@(posedge clk)是时间控制敏感函数,表示clk上升沿到来的敏感时刻。每当clk的上升沿到来时,always块中的全部语句就执行一遍。另外,在程序的最后用“cout=&q”语句产生进位输出,在语句中“&q”是与缩减运算,只有q中的数字全为1时,结果cout才为1。

注意:

(1)always块语句常用于描述时序逻辑,也可描述组合逻辑。

(2)always块可用多种手段来表达逻辑关系,如用if-else语句或case语句。

(3)always块语句与assign语句是并发执行的,assign语句一定要放在always块语句之外。

4)用initial块语句建模

initial块语句与always块语句类似,不过在程序中它只执行1次就结束了。initial块语句常用于设计电路的初始化操作和仿真。

从例6-1和例6-2可以看出Verilog HDL程序设计模块的基本结构:

①Verilog HDL程序是由模块构成的。每个模块的内容都是嵌在module和endmodule两语句之间的,每个模块实现特定的功能,模块是可以进行层次嵌套的。

②每个模块首先要进行端口定义,并声明输入(input)、输出(output)或双向(inout)端口,然后对模块的功能进行逻辑描述。

③Verilog HDL程序的书写格式自由,一行可以写一条或多条语句,一条语句也可以分为多行写。

④除了end或以end开头的关键字(如endmodule)语句外,每条语句后必须要有分号。程序中的关键字全部用小写字母书写,标点符号全部用半角符号。

⑤可以用/*……*/或//对Verilog HDL程序的任何部分做注释。一个完整的源程序应当加上需要的注释,以加强程序的可读性。

⑥每个Verilog HDL源文件中只准有一个顶层模块,其他为子模块。

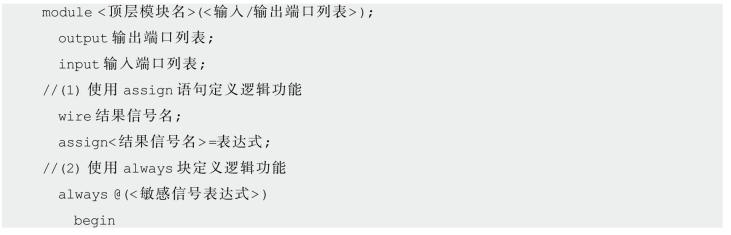

Verilog HDL模块的模板(仅考虑用于逻辑可综合的部分)如下:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。