1.FPGA主芯片

核心板上的FPGA芯片采用的是Altera公司CycloneⅡ系列的EP2C5T144C8,此芯片资源丰富,价格适中,非常适合FPGA入门学习使用。CycloneⅡ系列资源图如图5-5所示。

图5-5 CycloneⅡ系列资源图

CycloneⅡFPGA系列简介:

Altera公司CycloneⅡ采用全铜层、低K值、1.2 V SRAM工艺设计,裸片尺寸被优化得尽可能小。采用300 mm晶圆,以TSMC成功的90 nm工艺技术为基础,CycloneⅡ器件提供了4608到68 416个逻辑单元(logic element,LE),并具有一整套最佳的功能,包括嵌入式18 b×18 b乘法器、专用外部存储器接口电路、4 Kb嵌入式存储器块、锁相环和高速差分I/O能力。

CycloneⅡ器件扩展了FPGA在成本敏感性、大批量应用领域的影响力,延续了第一代Cyclone器件系列的成功。EP2C5T144C8:“2”——CycloneⅡ系列;“5”——逻辑单元4608个;“T”——封装类型;“144”——管脚数量;“8”——速度等级为8。

通常,芯片的逻辑单元和RAM的数量是重要的参考指标,EP2C5T144C8已经足够初学者使用了。FPGA主芯片原理图如图5-6所示,把芯片的可用I/O口都引出利用。

图5-6 FPGA主芯片原理图

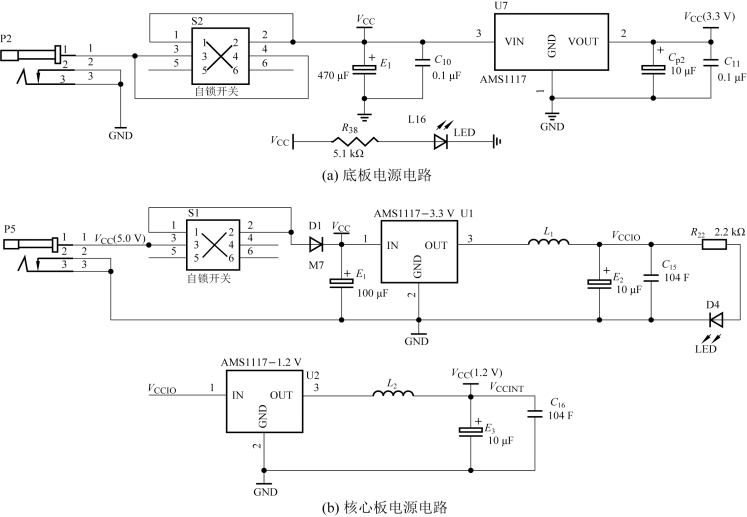

2.电源电路

电源是保证整个开发系统正常工作最重要的部分。电源电路分两部分,一部分是底板电源,一部分是核心板电压。开发板底板外部输入5 V电源,经过AMS1117-3.3 V稳压芯片后输出3.3 V电压,给底板上的器件供电。核心板上也通过稳压芯片输出3.3 V电压,主要用于给FPGA所有I/O口、核心板存储器电路、串行配置器件、复位电路和LED等供电;3.3 V电压再经过AMS1117-1.2 V稳压芯片输出1.2 V电压,给FPGA的内核和锁相环供电。同时,各电源输入及输出部分设计了高质量钽电容,用作电源滤波处理,提高系统电源稳定性。电源电路如图5-7所示。

图5-7 底板和核心板电源电路

3.核心板独立按键及LED电路

核心板上有4个由I/O口控制的LED,位于核心板的下方,在单独使用核心板时,可以用来做流水灯等实验项目。核心板上有5个独立按键,K1~K4可以作为操作按键,K5作为系统复位按键,因为K5接Pin88引脚(系统时钟专用输入引脚),作为系统复位输入比较合适。每个独立按键都配有上拉电阻,保证没有按键按下时输入信号是高电平的。LED和按键的电路如图5-8所示。

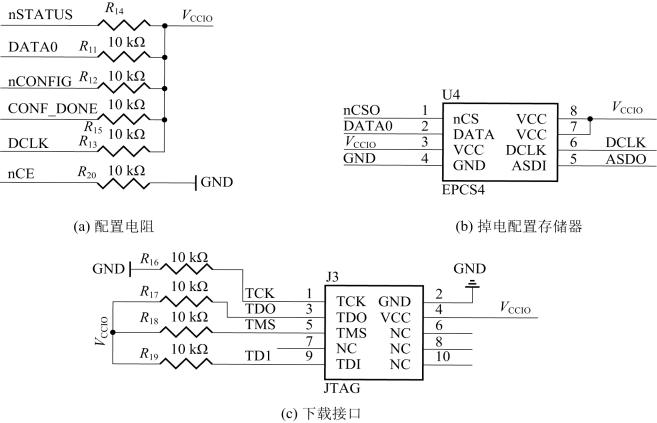

4.JTAG下载和存储配置电路

电路包括JTAG下载接口及EPCS4存储配置芯片。利用JTAG接口可以下载SOF文件到FPGA,但是掉电数据会丢失;将SOF文件转换为JIC文件格式后可通过JTAG接口下载到EPCS4存储配置芯片中,掉电程序数据不会丢失,上电后数据可从EPCS4恢复到FPGA中。下载和存储配置相关电路如图5-9所示。(www.daowen.com)

5.系统时钟电路

FPGA开发板采用50 MHz有源贴片晶振为FPGA提供运行时钟,时钟部分电路电源经过滤波处理,工作更加稳定可靠。时钟电路如图5-10所示,开发板中对FPGA时钟引脚处理如下:

图5-8 LED和按键的电路

图5-9 下载和存储配置电路

图5-10 时钟电路

(1)CLK0用作系统工作时钟,直接接入50 MHz晶振;

(2)CLK7用作系统复位引脚,用户可以通过编程实现复位功能;

(3)CLK1、CLK2、CLK3、CLK4为用户输入引脚,引出到扩展座,供用户使用;

(4)CLK5、CLK6未引出。

6.核心板扩展I/O口电路

FPGA开发板采用核心板与接口板分离的形式,用户可以通过核心板外接其他电路,既保证了通用性,又保证了实用性。核心板上的FPGA I/O口通过P1A、P1B两个双排插针引出。插针设置了V CC(5 V)、V CC(3.3 V)、GND电源接口,方便核心板与其他电路连接。扩展接口的原理图如图5-11所示。

图5-11 扩展接口原理图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。