QuartusⅡ9.0及以前版本集成了仿真功能,但是后面版本未集成仿真功能,因此需要掌握ModelSim软件仿真技巧。

QuartusⅡ9.0版本自带的Simulation仿真与ModelSim仿真的优缺点比较如下:

第一,QuartusⅡ自带的Simulation比较适合初学者使用,纯粹的图形用户界面(graphics user interface,GUI),用鼠标设置即可进行仿真,非常简洁明了。但是对于比较大的工程和比较复杂的项目,QuartusⅡ纯粹的手工、死板的设置,或许会让设计者束手无策,这个时候要使用ModelSim仿真。

第二,相对QuartusⅡ自带的Simulation而言,ModelSim Simulation也能简单地进行GUI设置激励,其更强大之处在于使用testbench测试语言来对逻辑设计进行仿真测试。对于规模大的项目,往往测试就占去了大部分时间,如若还用QuartusⅡ自带的Simulation,往往得不到满意的结果。ModelSim适合仿真复杂的项目,能熟练运用ModelSim必然会给FPGA开发带来事半功倍的效果。

1.Modelsim_Altera_ase软件安装

ModelSim软件一般分两个版本:ase是Altera Start Edition,即入门版,免费使用;ae是Altera Edition,需要付费,支持更多功能。

对于一般设计,ase已经足够了,装上就能使用。

如想安装ae,请参考相关教程,网页地址如下:

http://www.cnblogs.com/crazybingo/archive/2011/02/21/1959893.html。

此处以安装11.0_Altera_Modelsim_ase_windows.exe为例介绍安装步骤,其他版本的操作基本一样。具体步骤如下:

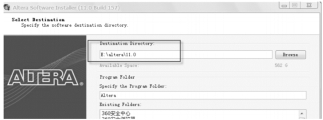

(1)打开安装目录下的setup文件,依次点击界面上的“Next”按钮,直到选择路径的时候,选择与QuartusⅡ安装目录相同的路径,如图4-23所示。

(2)再点击“Next”按钮,等待安装完毕。

(3)安装完毕,出现图4-24所示的界面。

图4-23 选择安装路径

图4-24 完成安装出现的界面

(4)点击“OK”按钮。

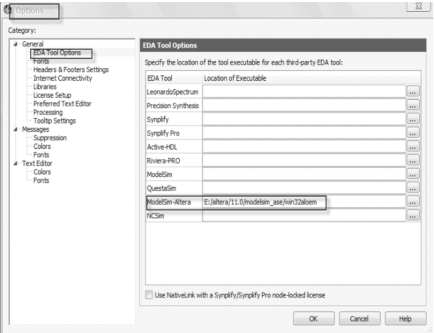

(5)打 开QuartusⅡ,点 击 菜 单“Tool”→“Options”,在EDA Tool Options的ModelSim-Altera中,选择MoldelSim-Altera应用程序的根目录,配置ModelSim-Altera应用程序第三方软件路径,如图4-25所示,在ModelSim-Altera一项指定安装路径为E:/altera/11.0/modelsim_ase/win32aloem(其中E:/altera/11.0/modelsim_ase/为计算机中ModelSim-Altera 6.5e的安装路径)。

图4-25 配置第三方软件路径

至此,ModelSim-Altera_ase版本安装完毕。

2.testbench的编写

在用ModelSim进行功能仿真时,需要编写testbench测试文件。由于篇幅的限制,这里只做简要的介绍。

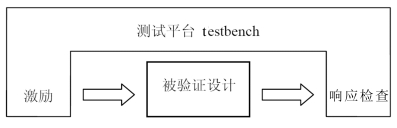

testbench就是测试平台的意思。testbench的一般结构如图4-26所示。

testbench的编写一般使用行为级语法,因为它不需要被综合。一般使用元件例化的方法将被验证设计例化至testbench文件中。下面结合直接数字合成(direct digital synthesis,DDS)正弦波发生器的设计举一个testbench的实例。

图4-26 testbench的一般结构

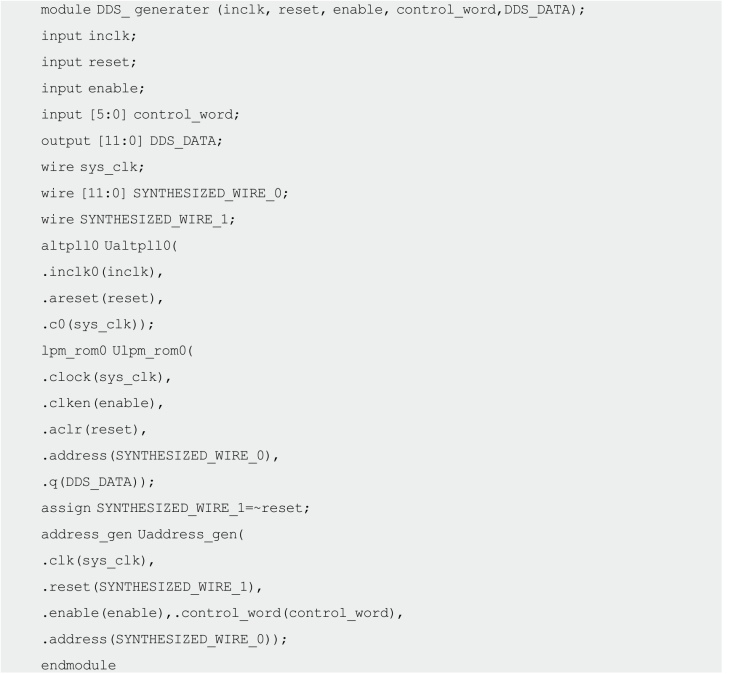

首先,要得到“被验证设计”文件。如果设计的DDS正弦波发生器的顶层文件是一个用原理图方式描述的文件(格式为.bdf),则可以点击“File”→“Create/Update”→“Create HDL Design File for Current File”,得到Verilog描述方式的顶层文件,因为testbench只支持Verilog描述设计。代码如下:

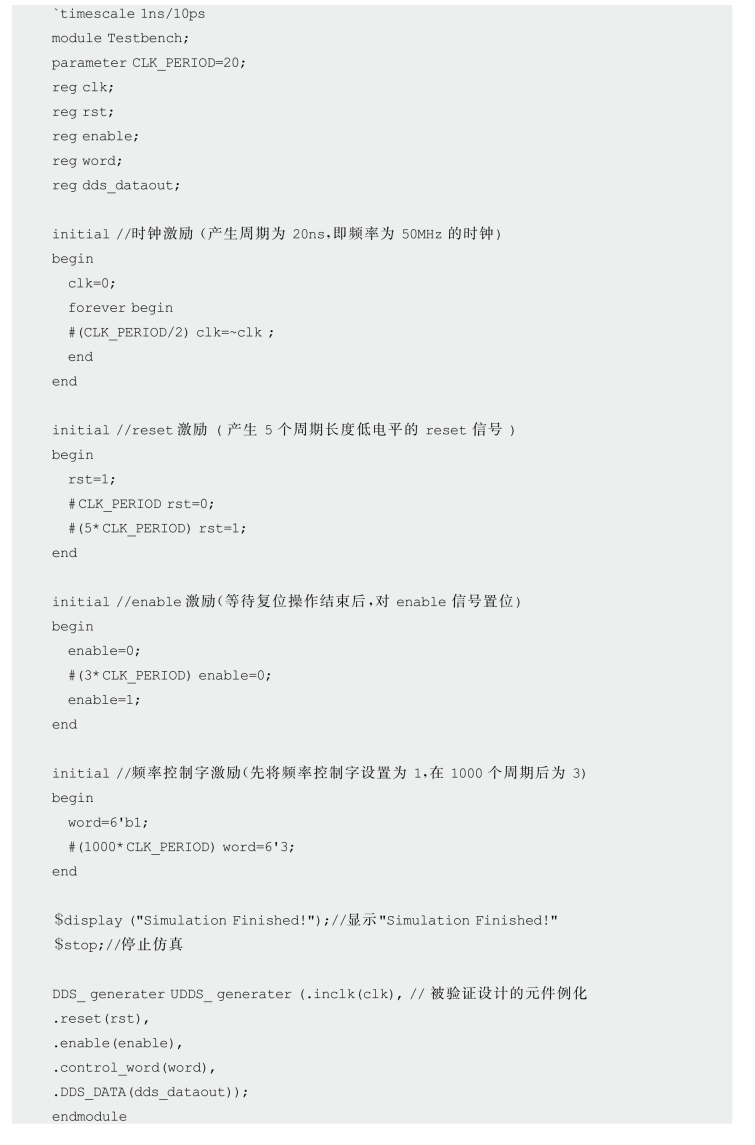

然后,设计testbench。testbench包括两部分,一是激励,二是被验证设计的元件例化。对于DDS正弦波发生器,我们共需要时钟“inclk”、复位“reset”、使能“enable”和频率控制字“control_word”这四个激励源。具体的testbench设计如下:

完成后就可以将这两个文件DDS_generater和testbench添加至ModelSim中进行功能仿真。

3.在QuartusⅡ中调用ModelSim-Altera(https://www.daowen.com)

下面以一个简单的实例来描述整个调用过程:

(1)打开QuartusⅡ,点击菜单“File”→“New”,新建一个工程。

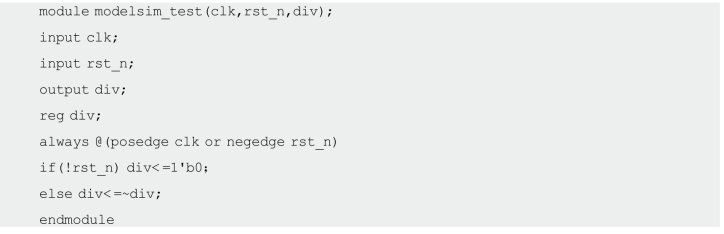

(2)新建一个Verilog HDL File,代码如下:

这是很简单的一段代码,能实现二分频电路。下面将对这个电路进行ModelSim仿真。

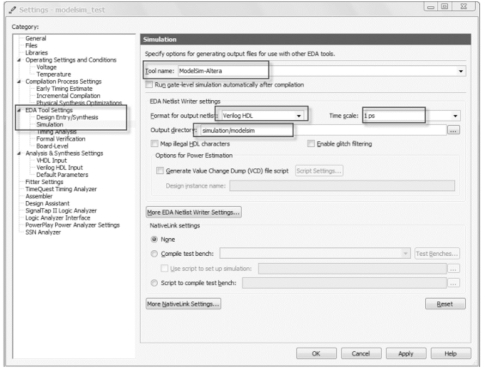

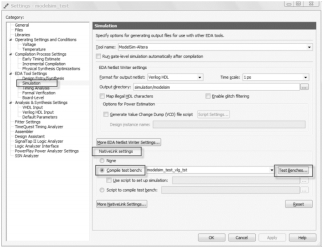

(3)设置仿真相关选项(见图4-27):在QuartusⅡ界面菜单栏中选择“Assignments”→“Settings”,在弹出的对话框的EDA Tool Settings中选择Simulation项;Tool name处选择ModelSim-Altera;Format for output netlist处选择开发语言的类型Verilog HDL或者VHDL等;Time scale处指定时间单位精度级别;Output directory处指定测试文件模板的输出路径(该路径是工程文件的相对路径)。

图4-27 设置仿真选项

(4)生成仿真测试文件。

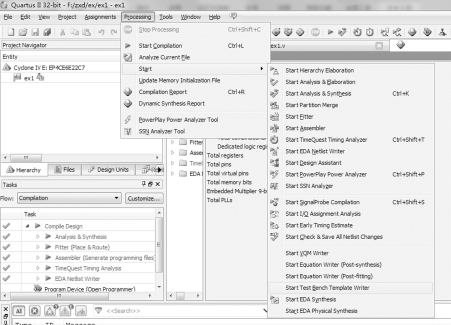

点击QuartusⅡ开发界面菜单栏“Processing”→“Start”→“Start Test Bench Template Writer”(见图4-28),提示生成成功。

图4-28 选择“Start Test Bench Template Writer”

生成仿真测试文件(modelsim_test工程文件中的modelsim目录下找到后缀名为.vt的文件),可以根据需要进行编辑修改。图4-29所示是生成的文件原样,还没修改。

图4-29 仿真测试文件原样

注意:

QuartusⅡ中testbench文件的后缀是.vt,产生的模板文件只包含端口映射和端口声明等,具体的功能还需要设计者自己编写设计。

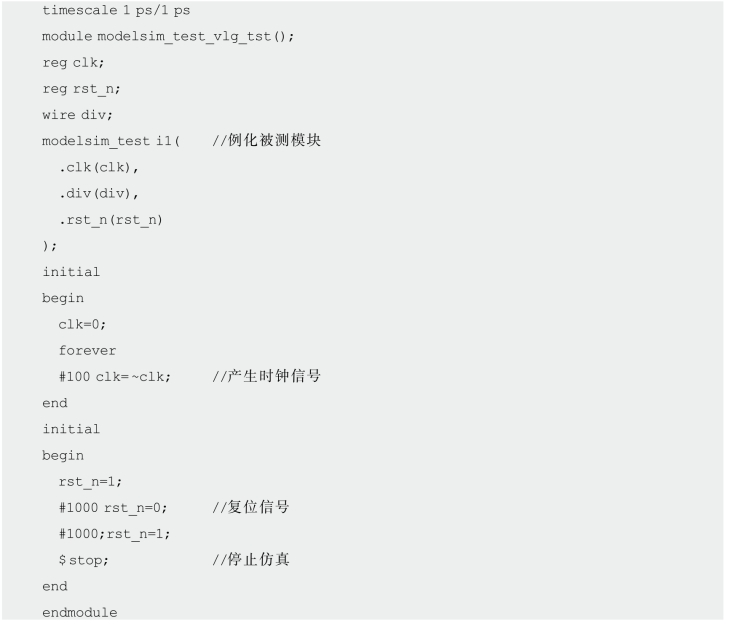

下面我们在模板上修改,修改编写分频器的testbench,代码如下:

测试代码产生时钟信号、复位信号,例化被测模块。

(5)设置测试文件的链接关系。在QuartusⅡ界面菜单栏中选择“Assignments”→“Settings”,在弹出的对话框中选中EDA Tool Settings的Simulation项;在NativeLink settings中选择Compile test bench,并点击后面的“Test Benches”按钮,如图4-30所示。

图4-30 设置测试文件的链接关系

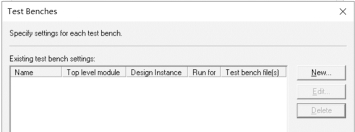

然后在“Test Benches”对话框中点击“New”按钮,如图4-31所示。

图4-31 “Test Benches”对话框

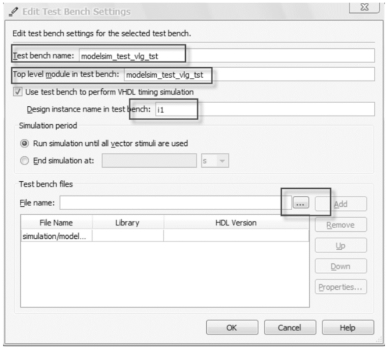

在弹出的对话框中的“Test bench name”栏处填写刚刚创建的testbench文件的实体名,即modelsim_test_vlg_tst;在“Top level module in test bench”处也填写modelsim_test_vlg_tst;在“Design instance name in test bench”处填写i1,即被测模块例化名称(该名称可以从testbench的文件里直接复制过来,避免手误写错);可设置仿真结束时间(“End simulation at”)。在Test bench files选项中浏览、添加testbench文件,最后点击“Add”按钮,一步一步进行即可完成测试平台参数设置,如图4-32所示。

图4-32 测试平台参数设置

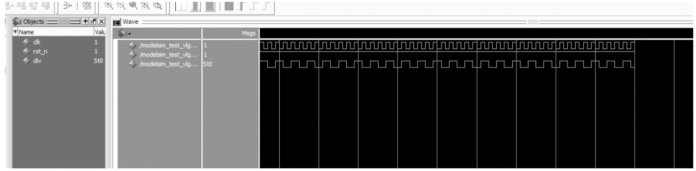

(6)一切准备就绪,在QuartusⅡ界面菜单栏中选择“Tools”→“Run EDA Simulation Tool”→“EDA RTL Simulation”进行行为级仿真,可以看到弹出ModelSim-Altera 6.5e的运行界面,放大观察仿真波形,如图4-33所示,可以看到div信号是clk的二分频。

图4-33 ModelSim仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。