QuartusⅡ9.0版本软件自带仿真功能,仿真的目的就是,在软件环境下验证电路的行为和设想中的是否一致。FPGA/CPLD中的仿真分为功能仿真和时序仿真。功能仿真着重考察电路在理想环境下的行为和设计构想的一致性,时序仿真则在电路已经映射到特定的工艺环境后,考察器件在延时情况下对布局布线网表文件进行的一种仿真。

仿真一般需要建立波形文件、输入信号节点、编辑输入信号、保存波形文件和运行仿真器等过程。

1.建立波形文件

波形文件用来为设计产生输入激励信号。利用QuartusⅡ波形编辑器可以创建矢量波形文件(.vwf)。创建一个新的矢量波形文件的步骤如下:

(1)选择QuartusⅡ主界面“File”菜单下的“New”命令,弹出新建对话框。

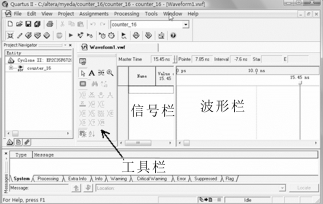

(2)在新建对话框中选择“Verification/Debugging Files”下的“Vector Waveform File”,点击“OK”按钮,打开一个空的波形编辑器窗口,该窗口主要分为信号栏、工具栏和波形栏,如图4-17所示。

(3)添加仿真测试信号,设置输入信号和仿真参数。

2.输入信号节点

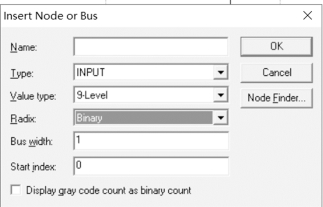

(1)在波形编辑方式下,执行“Edit”菜单中的“Insert Node or Bus”命令,或者在波形编辑器左边Name列的空白处点击鼠标右键,弹出“Insert Node or Bus”对话框,或者在波形编辑器左边Name列的空白处双击左键,也会弹出“Insert Node or Bus”对话框,如图4-18所示。

图4-17 波形编辑器窗口

图4-18 “Insert Node or Bus”对话框

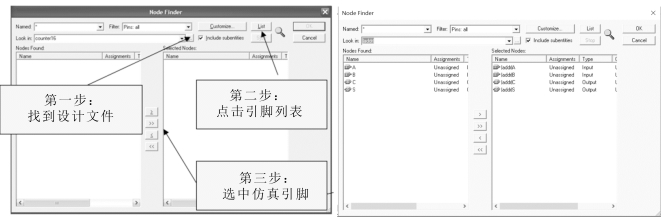

(2)点击“Insert Node or Bus”对话框中的“Node Finder”按钮,弹出“Node Finder”对话框,在此对话框中添加信号节点,如图4-19所示。

图4-19 在“Node Finder”对话框中添加信号节点

3.编辑输入信号

编辑输入信号是指在波形编辑器中指定输入节点的逻辑电平变化,编辑输入节点的波形。

在仿真编辑窗口的工具栏中列出了各种功能选择按钮,主要用于绘制、编辑波形,给输入信号赋值。具体按钮及其功能如下:

:在波形文件中添加注释。

:在波形文件中添加注释。

:修改信号的波形值,把选定区域的波形更改成原值的相反值。

:修改信号的波形值,把选定区域的波形更改成原值的相反值。

:全屏显示波形文件。

:全屏显示波形文件。

:放大、缩小波形。(www.daowen.com)

:放大、缩小波形。(www.daowen.com)

:在波形文件信号栏中查找信号名,可以快捷地找到待观察信号。

:在波形文件信号栏中查找信号名,可以快捷地找到待观察信号。

:将某个波形替换为另一个波形。

:将某个波形替换为另一个波形。

:给选定信号赋原值的反值。

:给选定信号赋原值的反值。

:输入任意固定的值。

:输入任意固定的值。

:输入随机值。

:输入随机值。

:“U”表示给选定的信号赋值,“X”表示不定态,“0”表示赋0,“1”表示赋1,“Z”表示高阻态,“W”表示弱信号,“L”表示低电平,“H”表示高电平,“DC”表示不赋值。

:“U”表示给选定的信号赋值,“X”表示不定态,“0”表示赋0,“1”表示赋1,“Z”表示高阻态,“W”表示弱信号,“L”表示低电平,“H”表示高电平,“DC”表示不赋值。

:设置时钟信号的波形参数,先选中需要赋值的信号,然后鼠标右键点击此图标,弹出“Clock”对话框,在此对话框中可以设置输入时钟信号的起始时间(“Start time”)、结束时间(“End time”)、时钟脉冲周期(“Period”)、相位偏置(“Offset”)以及占空比。

:设置时钟信号的波形参数,先选中需要赋值的信号,然后鼠标右键点击此图标,弹出“Clock”对话框,在此对话框中可以设置输入时钟信号的起始时间(“Start time”)、结束时间(“End time”)、时钟脉冲周期(“Period”)、相位偏置(“Offset”)以及占空比。

:给信号赋计数值,先选中需要赋值的信号,然后鼠标右键点击此图标,弹出“Count Value”对话框,然后赋值。

:给信号赋计数值,先选中需要赋值的信号,然后鼠标右键点击此图标,弹出“Count Value”对话框,然后赋值。

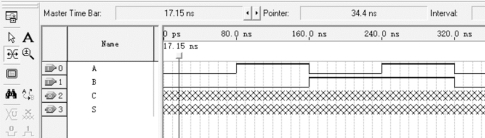

设计的半加器仿真输入信号波形设置如图4-20所示,用波形编辑工具 设置输入信号。

设置输入信号。

图4-20 半加器仿真输入信号波形设置

4.运行仿真器

QuartusⅡ软件中默认的是时序仿真,如果进行功能仿真则需要先对仿真进行设置,步骤如下:

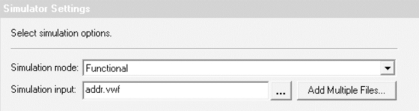

(1)选择QuartusⅡ主窗口“Assignments”菜单下的“Settings”命令,可以进入参数设置页面,然后单击“Simulation Settings”,在弹出的对话框中的“Simulation mode”栏中选择“Functional”,如图4-21所示。

图4-21 在“Simulation mode”栏中选择“Functional”

(2)选择QuartusⅡ主窗口“Processing”菜单下的“Generate Functional Simulation Netlist”命令,生成功能仿真网表文件。

(3)选择QuartusⅡ主窗口“Processing”菜单下的“Start Simulation”进行功能仿真。

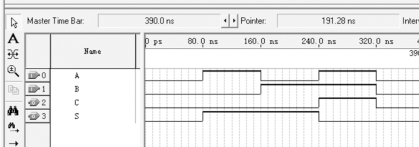

功能仿真满足要求后,还要对设计进行时序仿真。时序仿真可以在编译后直接进行,但是要 将 图4-21中 的“Simulation mode”设 置 为“Timing”,设 置 以 后 直 接 点 击“Start Simulation”,执行时序仿真。图4-22所示为半加器仿真结果。

图4-22 半加器仿真结果

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。