QuartusⅡ编译器的主要任务是对设计项目进行检查并完成逻辑综合,同时将项目最终设计结果生成器件的下载文件。编译开始前,可以对工程的参数进行设置。

QuartusⅡ软件中的编译类型有全编译和分步编译两种。

选择QuartusⅡ主窗口“Processing”菜单下的“Start Compilation”命令,或者在主窗口的工具栏上直接点击图标 可以进行全编译。

可以进行全编译。

全编译 的 过 程 包 括 分 析 与 综 合(“Analysis & Synthesis”)、适 配(“Fitter”)、编 程(“Assembler”)、时序分析(“Classic Timing Analyzer”)这4个环节,而这4个环节各自对应相应的菜单命令,可以单独分步执行,也就是分步编译。

分步编译就是使用对应命令分步执行对应的编译环节,每完成一个编译环节,生成一个对应的编译报告。分步编译跟全编译一样分为四步:

(1)分析与综合(“Analysis&Synthesis”):对设计文件进行分析和检查输入文件是否有错误,对应的菜单命令是QuartusⅡ主窗口“Processing”菜单下的“Start”→“Start Analysis&Synthesis”,对应的快捷图标是主窗口工具栏上的 。

。

(2)适配(“Fitter”):在适配过程中,完成设计逻辑器件中的布局布线,选择适当的内部互连路径、引脚分配、逻辑元件分配等,对应的菜单命令是QuartusⅡ主窗口“Processing”菜单下的“Start”→“Start Fitter”。

注意:

两种编译方式的引脚分配有所区别。

(3)编程(“Assembler”):产生多种形式的器件编程映像文件,通过软件下载到目标器件当中,菜单命令是QuartusⅡ主窗口“Processing”菜单下的“Start”→“Start Assembler”。(www.daowen.com)

(4)时序分析(“Classic Timing Analyzer”):计算给定设计与器件上的延时,完成设计分析中的时序分析和所有逻辑的性能分析,菜单命令是QuartusⅡ主窗口“Processing”菜单下的“Start”→“Start Classic Timing Analyzer”,对应的快捷图标是主窗口工具栏上的 。

。

编译完成后,编译报告窗口“Compilation Report”会报告工程文件编译的相关信息,如编译的顶层文件名、目标芯片的信号、引脚的数目等。

全编译操作简单,适合简单的设计。对于复杂的设计,选择分步编译可以及时发现问题,提高设计纠错的效率,从而提高设计效率。

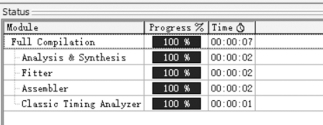

执行QuartusⅡ主窗口“Processing”菜单的“Start Compilation”命令,或者在主窗口上直接用鼠标单击“开始编译”命令按钮,开始对addr.bdf文件进行编译。编译工具的编译进程可以在如图4-15所示的状态(“Status”)窗口中看到。编译过程包括分析与综合、适配、编程和时序分析4个环节,都是由软件自动完成的。

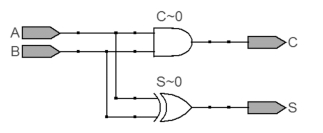

在设计输入完成后,可以通过选择菜单“Processing”→“Start”→“Start Analysis&Elaboration”选项,对输入进行分析,如果存在错误,信息窗口将出现错误信息。分析完成后,可通过菜单“Tools”→“Netlist Viewer”→“RTL Viewer”查看设计对应的寄存器传输级视图,即RTL视图(见图4-16)。

图4-15 QuartusⅡ编译状态窗口

图4-16 RTL视图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。