下面以建立一个完整的工程为例来介绍Vivado软件的使用方法。

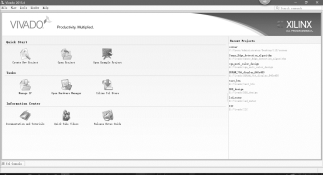

打开软件,弹出主菜单界面(见图2-38),点击“Create New Project”,弹出介绍界面(见图2-39),然后点击“Next”按钮进入下一步。

图2-38 主菜单界面

图2-39 介绍界面

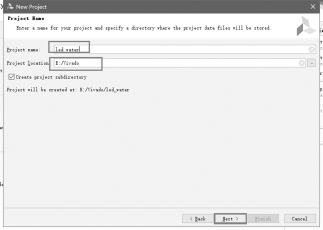

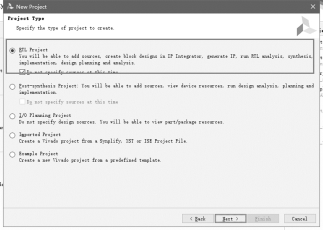

设置好工程名称和工程文件存放位置,然后点击“Next”按钮进入下一步,如图2-40所示。工程类型选择“RTL Project”,点击“Next”按钮进入下一步,如图2-41所示。

图2-40 设置工程名称和存放位置

图2-41 选择“RTL Project”

选择板卡型号,这里使用的是Artix-7系列的cpg236,如图2-42所示。用户根据自己的板卡型号自行定义。然后点击“Next”按钮,进入新工程设置总结界面“New Project Summary”,点击“Finish”按钮,如图2-43所示。

图2-42 选择板卡型号

图2-43 新工程设置总结界面

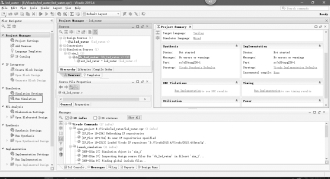

图2-44所示界面左边是工程管理面板。点击“Add Source”以添加Verilog HDL文件。

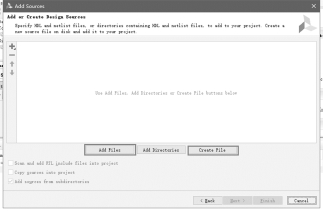

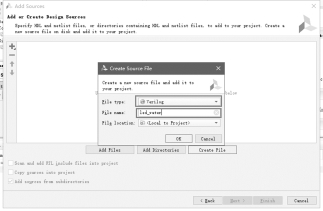

在“Add Sources”对话框中选择“Add or create design sources”选项(见图2-45),然后点击“Next”按钮。在弹出的对话框中点击“Add Files”按钮是添加已有的文件,点击“Create Files”按钮是新建一个Verilog HDL文件,如图2-46所示。如果没有现成的文件,就选择新建一个文件,然后点击“Next”按钮。

图2-44 工程管理面板

图2-45 选择“Add or create design sources”选项

图2-46 添加已有文件或新建Verilog HDL文件

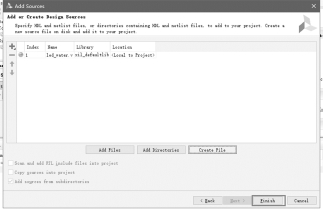

弹出新建文件设置对话框,如图2-47所示,选择文件类型为Verilog,接着设置文件名,一般根据功能来命名,这里设计的是流水灯,文件名为led_water。创建文件成功,如图2-48所示,点击“Finish”按钮。

图2-47 新建文件设置对话框

图2-48 完成文件创建

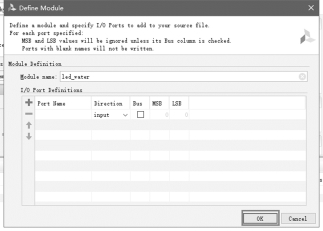

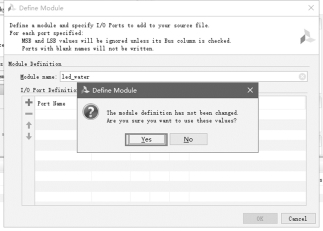

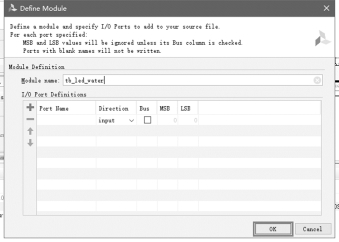

在弹出的如图2-49所示的“Define Module”对话框中点击“OK”按钮,然后在确认对话框中点击“Yes”按钮,如图2-50所示。

图2-49 “Define Module”对话框

图2-50 点击“Yes”按钮确认

双击led_water这个文件(见图2-51),打开编写程序,这是一个流水灯设计工程。编写完成后,点击如图2-52所示的编译文件,也可查看工程的RTL图。

图2-51 双击led_water文件

图2-52 点击编译文件

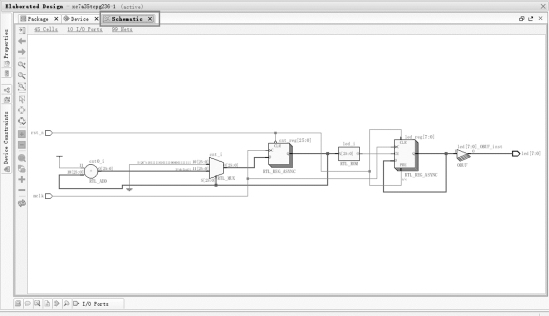

图2-53所示是生成的RTL图。双击该图可以将窗口放大。

图2-53 生成的RTL图

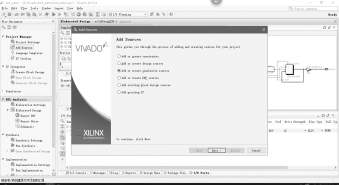

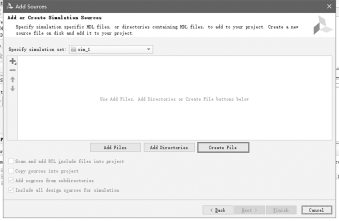

RTL图能绘制出来,说明该工程没有语法错误。再次执行“Add Sources”,选择“Add or create simulation sources”(见图2-54),添加测试文件。如图2-55所示,选择新建一个文件。

图2-54 选择“Add or create simulation sources”

(https://www.daowen.com)

(https://www.daowen.com)

图2-55 选择新建一个文件

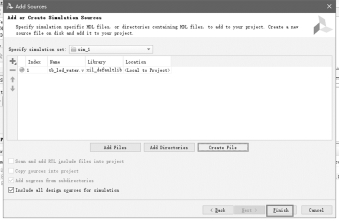

命名文件并确认完成后单击“Finish”按钮,如图2-56和图2-57所示。

图2-56 新建文件设置对话框中命名文件

图2-57 点击“Finish”按钮

在弹出的如图2-58所示的“Define Module”对话框中点击“OK”按钮,然后在弹出的确认对话框中点击“Yes”确认,如图2-59所示。

图2-58 “Define Module”对话框

图2-59 点击“Yes”按钮确认

找到tb_led_water文件(见图2-60),双击打开,编写测试文件。

点击“Run Simulation”,进行仿真,如图2-61所示。

图2-60 双击tb_led_water文件

图2-61 点击“Run Simulation”进行仿真

reg[25:0]cnt;//设定一个26位的计数器

parameter TIME=26'd50000000;//parameter TIME=26'd500;//j us t tes t

注意:

仿真前把测试文件计数值改小一点,如“TIME=26’d500;”,不然运行得太慢。

点击“Run All”按钮,让流水灯测试起来,如图2-62所示。

如图2-63所示,流水灯的数值在变化,说明设置正确。

图2-62 点击“Run All”让流水灯测试起来

图2-63 数值在变化

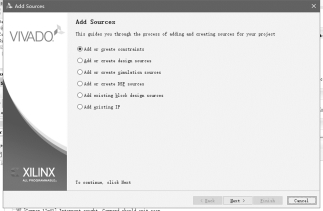

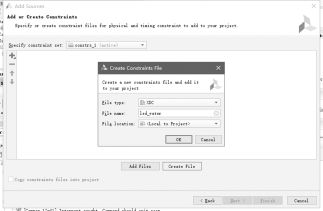

点击“Add Sources”,添加约束文件,选择“Add or create constraints”(见图2-64),新建一个引脚约束文件,然后选择文件类型,为文件命名,点击“OK”按钮,如图2-65所示。

图2-64 选择“Add or create constraints”

图2-65 新建引脚约束文件

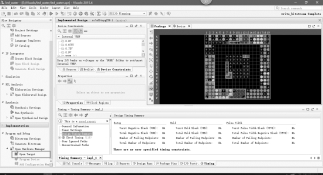

点击新建好的文件(见图2-66),将约束文件内容复制进去。然后点击“Generate Bitstream”,如图2-67所示,对工程进行综合,综合完成后就可以下载板子了。(下载板子的时候要把测试时改的代码改回来。)

图2-66 点击新建好的文件

图2-67 点击“Generate Bitstream”

点击“Open Target”→“Auto Connect”(见图2-68),会自动连接设备,或者直接选择设备,点击“Program device”(见图2-69)。

图2-68 点击“Open Target”

图2-69 点击“Program device”

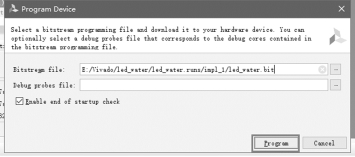

选择下载文件,点击“Program”按钮,即可成功下载,如图2-70所示。

图2-70 点击“Program”按钮

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。