GPIO端口的每一个管脚可以有不同的功能。依据数据手册中列出的每个I/O端口的特定硬件特征,GPIO端口的每个位可以由软件分别配置成多种工作模式。

①输入浮空:用于不确定高低电平的输入。

②输入上拉:用于默认为上拉至高电平的输入。

③输入下拉:用于默认为下拉至低电平的输入。

④模拟输入:用于模拟量的输入。

⑤开漏输出:用于实现电平转换和线与功能的输出。

⑥推挽式输出:用于较大功率驱动的输出,电平为0和3.3V的场合。

⑦推挽式复用功能:复用功能下的推挽式输出。

⑧开漏复用功能:复用功能下的开漏输出。

STM32F103复位期间和刚复位后,复用功能为开启,I/O端口被配置成浮空输入模式,可通过端口配置程序设置所用I/O口的工作模式。

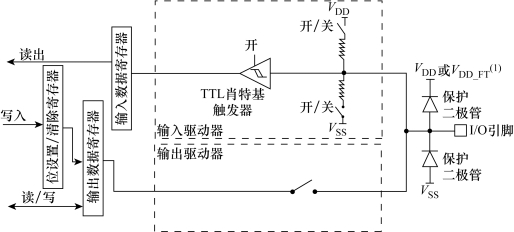

1.输入配置

当I/O端口配置为输入时:

①输出缓冲器被禁止。

②施密特触发输入被激活。

③根据输入配置(浮空、上拉和下拉)的不同,弱上拉和下拉电阻被连接。

④出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器。

⑤对输入数据寄存器的读访问可得到I/O状态。

图4.2给出了I/O端口位的输入配置。

图4.2 输入浮空/上拉/下拉配置

注意事项:VDD_FT对5V容忍I/O脚是特殊的,它与VDD不同

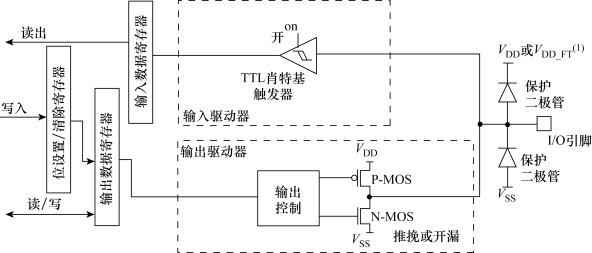

2.输出配置

当I/O端口被配置为输出时:

①输出缓冲器被激活。

②开漏模式,输出寄存器上的“0”激活N-MOS,而输出寄存器上的“1”将端口置于高阻状态(P-MOS从不被激活)。

③推挽模式,输出寄存器上的“0”激活N-MOS,而输出寄存器上的“1”将激活P-MOS。

④施密特触发输入被激活。

⑤弱上拉和下拉电阻被禁止。

⑥出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器。(https://www.daowen.com)

⑦在开漏模式时,对输入数据寄存器的读访问可得到I/O状态。

⑧在推挽式模式时,对输出数据寄存器的读访问得到最后一次写的值。

I/O端口位的输出配置原理如图4.3所示。

图4.3 I/O端口位的输出配置原理

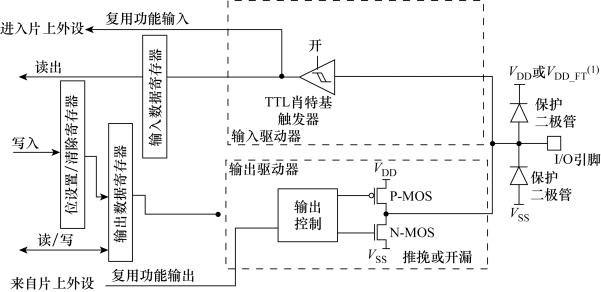

3.复用功能配置

当I/O端口被配置为复用功能时:

①在开漏或推挽式配置中,输出缓冲器被打开。

②内置外设的信号驱动输出缓冲器(复用功能输出)。

③施密特触发输入被激活。

④弱上拉和下拉电阻被禁止。

⑤在每个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器。

⑥开漏模式时,读输入数据寄存器时可得到I/O口状态。

⑦在推挽模式时,读输出数据寄存器时可得到最后一次写的值。

复用功能配置原理如图4.4所示。

图4.4 复用功能配置原理

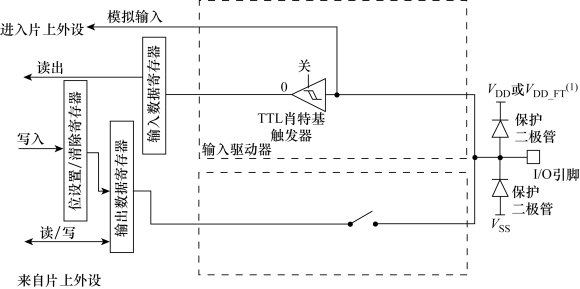

4.模拟输入配置

当I/O端口被配置为模拟输入配置时:

①输出缓冲器被禁止。

②禁止施密特触发输入,实现了每个模拟I/O引脚上为“0”。

③弱上拉和下拉电阻被禁止。

④读取输入数据寄存器时数值为“0”。

I/O端口位的高阻抗模拟输入配置原理如图4.5所示。

5.外设的GPIO配置和复用功能I/O重映射

外设的GPIO配置和复用功能I/O重映射内容较多并涉及后续章节,对初学者来说所涉不多,感兴趣的读者可通过STM32中文网站https://www.stmcu.co m.cn/下载《RM0008_STM32F101xx,STM32F102xx,STM32F103xx,STM32F105xx and STM32F107xx单片机参考手册》学习通用和复用功能I/O章节。

图4.5 I/O端口位的高阻抗模拟输入配置原理

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。