在ARMv7架构时代,ARM公司取消了使用数字加后缀的命名方法,ARM公司将ARMv7架构的处理器命名为“Cortex”。Cortex处理器内核是ARM公司最新一代嵌入式处理器的核心。Cortex处理器具有一个完整的处理核心,为用户提供了一个完整的“心脏”。Cortex处理器具有三个分支,“Cortex”单词后面接的字母表示了各个分支的具体类型,具体包括:A系列,主要面向复杂的高端应用程序,用于运行开放式的复杂操作系统;R系列,主要针对实时系统;M系列,主要为成本控制和微处理器应用提供优化。

Cortex-M3处理器基于ARMv7架构,支持Thumb-2指令集。关于Cortex-M3的描述可以参考《Cortex-M3技术参考手册》和《ARMv7架构参考手册》,还可以从ARM官网www.arm.com下载得到。

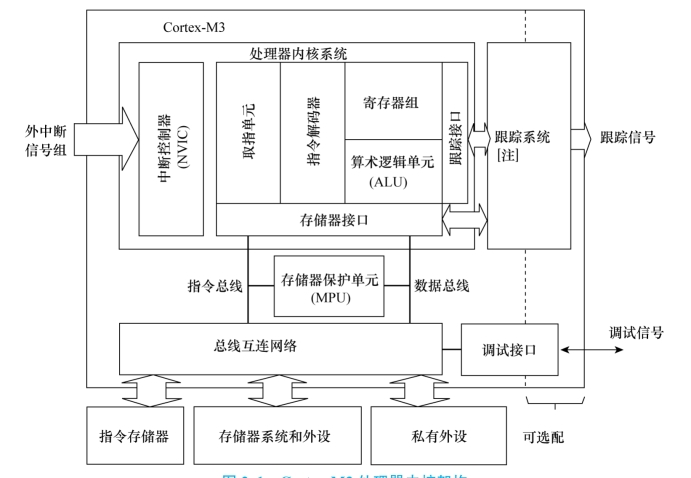

Cortex-M3处理器带有一个分级结构,其集成了名为CM3Core的中央处理器内核和先进的系统外设,并集成了嵌套中断向量控制器、内存保护、系统调试和跟踪等功能。Cortex-M3处理器内核架构如图2.1所示。

图2.1 Cortex-M 3处理器内核架构

ARM7处理器使用冯·诺依曼架构,指令和数据共用信号总线传输。而如图所示,Cortex-M3内核基于哈弗架构,指令和数据各使用一条总线传输;Cortex-M3处理器对多个操作可以并行执行,加快了应用程序执行的速度。(www.daowen.com)

ARM7和ARM9处理器都支持两种指令集(32位ARM指令集和16位Thumb指令集),而Cortex-M3系列处理器支持新型的ARM Thumb-2指令集。由于ARM Thumb-2指令集融合了ARM指令集和Thumb指令集,使在32位指令集的性能和16位指令集的代码密度之间取得了平衡。Cortex-M3处理器是一个32位处理器,带有32位宽的数据路径、寄存器库和内存接口,其中有13个通用寄存器、两个堆栈指针、一个链接寄存器、一个程序计数器和一系列包含编程状态寄存器的特殊功能寄存器。

Cortex-M3处理器提出标准化的微控制核心,在CPU基础上提供了整个微控制器的核心部分。Cortex-M3处理器内部具有4GB线性地址空间,该地址空间被分为Code区、SRAM区、外部设备区和系统设备区。与早期ARM架构不同的是,Cortex-M3处理器允许数据非对齐存取,以确保内部的SRAM得到充分利用。Cortex-M3处理器还可以使用一种称为“位带”的技术,利用两个32MB大小的“虚拟”内存空间实现对两个1MB大小的物理内存空间进行“位”的置位和清除操作。

嵌套中断向量控制器(NVIC)是Cortex-M3处理器中的一个比较关键的组件。NVIC是基于Cortex-M3内核的微控制器提供了标准的中断架构和优秀的中断响应能力,为超过240个中断源提供专门的中断入口,而且可以赋予每个中断源单独的优先级。

Cortex-M3处理器支持两种工作模式(即线程和处理器)及两个等级的代码访问(即有特权和无特权),能够在不牺牲应用程序安全的前提下执行复杂的开放式系统。无特权代码执行限制或拒绝对某些资源的访问,如某个指令或制定的内存位置。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。