IA-32结构的处理器都提供了浮点处理单元(FPU)。在i486之前的处理器中,FPU是独立于主处理器而存在的,通常称为“协处理器”。在i486之后,由于主处理器运算性能的提高,FPU也被集成到了主处理器中。不过,这对于程序员似乎是透明的。事实上,直到今天,从应用的角度来说,FPU仍然是以一个逻辑整体的形式存在的。由于8086没有FPU,因此,关于FPU的原理及其应用,国内汇编语言教材很少涉及。在此,笔者有必要稍作详解。

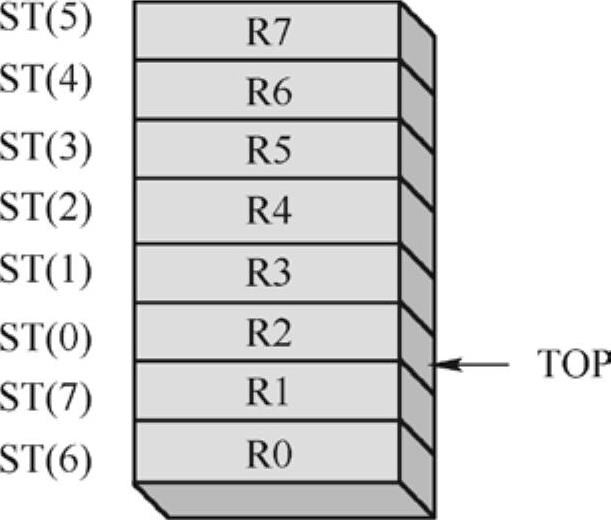

FPU共有8个80位的浮点数据寄存器,分别命名为RO、Rl、…、R7。不过,从程序员的角度来看,这8个寄存器的逻辑标识为ST(O)、ST(1)、ST(2)、ST(3)、ST(4)、ST(5)、ST(6)、ST(7)。两种命名没有必然的联系,这是非常奇怪的,笔者稍后解释。当然,FPU还拥寄存有器独、立状的态指寄令存指器针。、数据指针、标记寄存器、控制

图9-2 FPU寄存器堆栈

1.浮点数据寄存器

在i386处理器结构中,FPU是一个模拟的栈式机。与通用寄存器不同,浮点数据寄存器是以循环堆栈的形式组织的,如图9-2所示。图中TOP指向的是栈顶寄存器,它占用了状态寄存器中的3位。由于TOP栈顶可能是任意的,因此,要直接访问TOP指向的物理寄存器就必须经过变址寻址,同时,还要考虑偏移的取模处理。为了便于程序员访问,处理器将根据TOP的当前位置,为每个寄存器分配一个别名。将TOP指向的栈顶寄存器命名为ST(O),然后,沿栈顶向栈底的方向,依次标识为ST(1)-ST(7)。随着TOP的变化,处理器将自动改变寄存器的别名。

2.浮点运算的过程

众所周知,浮点数通常是依据IEEE 754格式存储的。关于IEEE 754格式的规范,笔者就不再详述了。浮点运算的过程大致分为三步:

1)将操作数装入浮点数据寄存器堆栈。

2)执行浮点运算指令。根据指令所需的操作数个数,从堆栈获取操作数,并将运算结果再次压入堆栈。

3)将运算结果存储至目标单元。

值得注意的是,在IA-32结构中,FPU与主CPU之间的操作数传递只能借助内存进行,而不能直接从主CPU的寄存器传递给FPU。

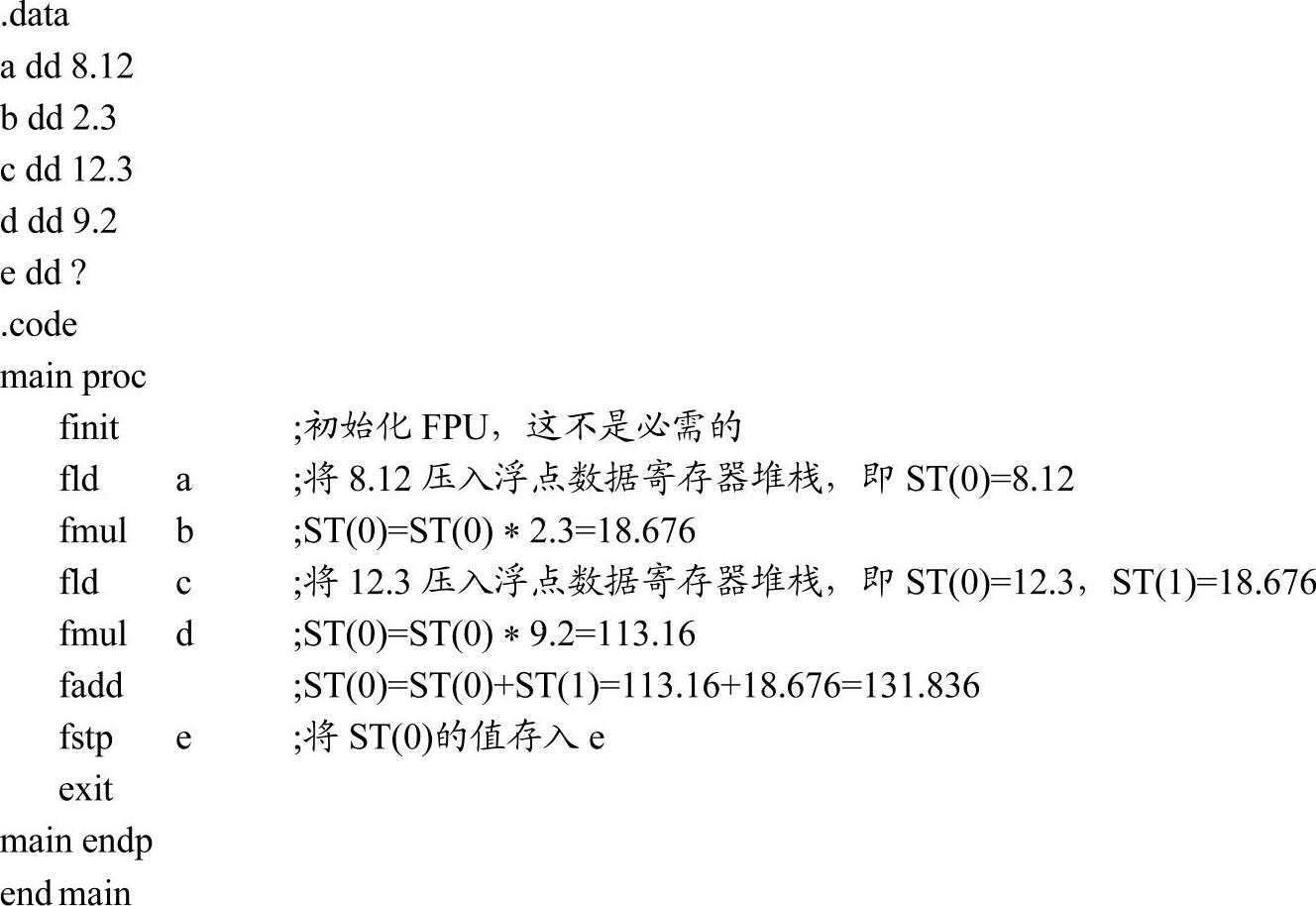

例9-2浮点运算实例,编程实现计算表达式(8.12×2.3)+(12.3×9.2)。

3.FPU指令集

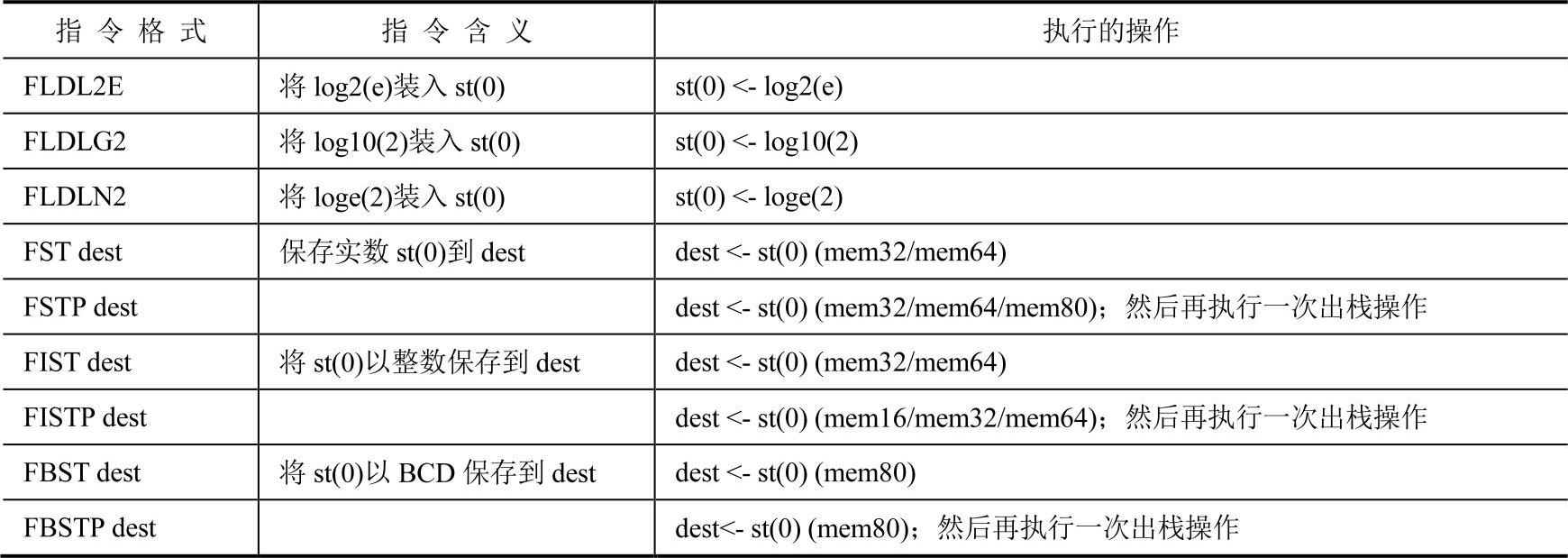

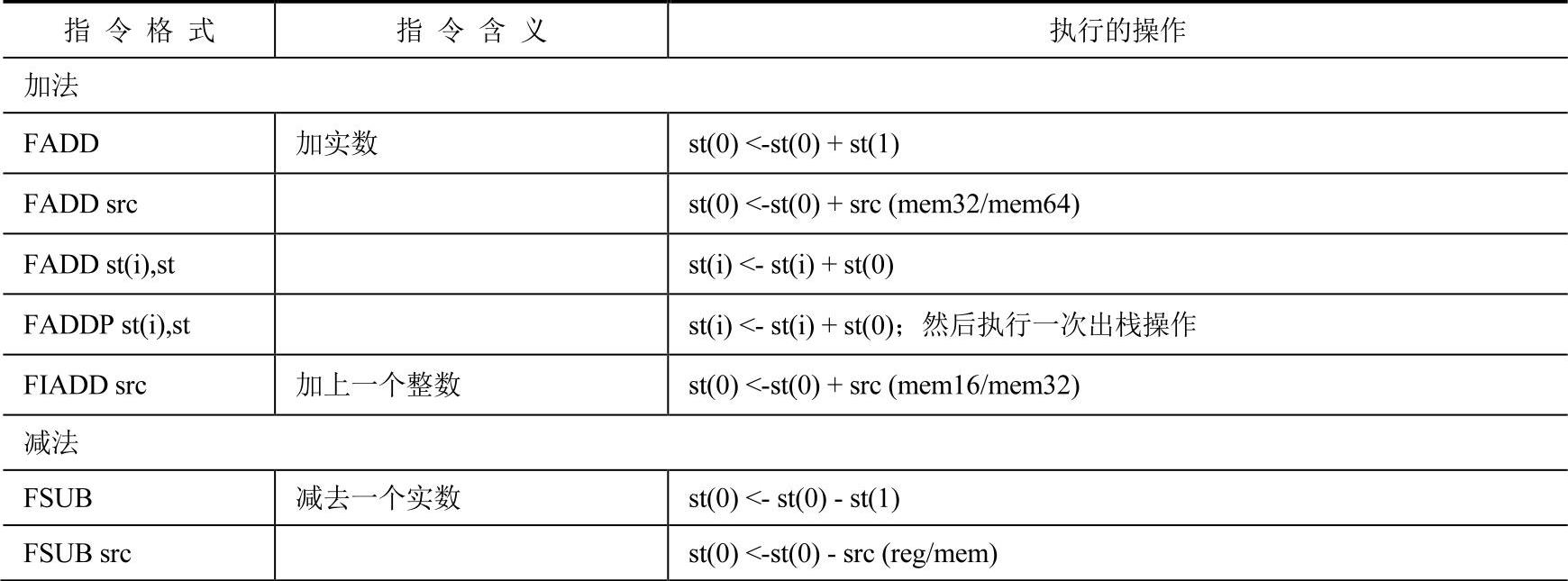

表9-1是数据传递操作指令列表。(https://www.daowen.com)

表9-1 数据传递操作指令列表

(续)

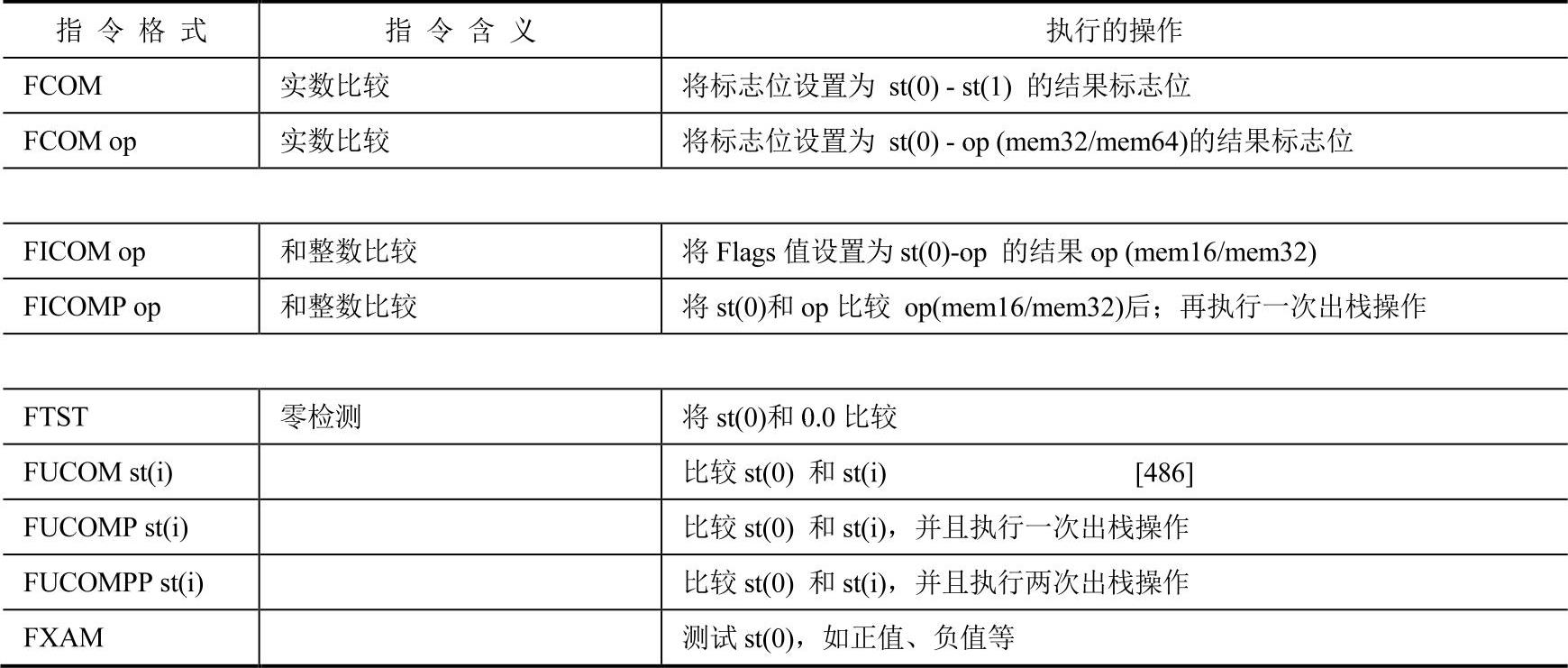

表9-2是数据比较指令列表。

表9-2 数据比较指令列表

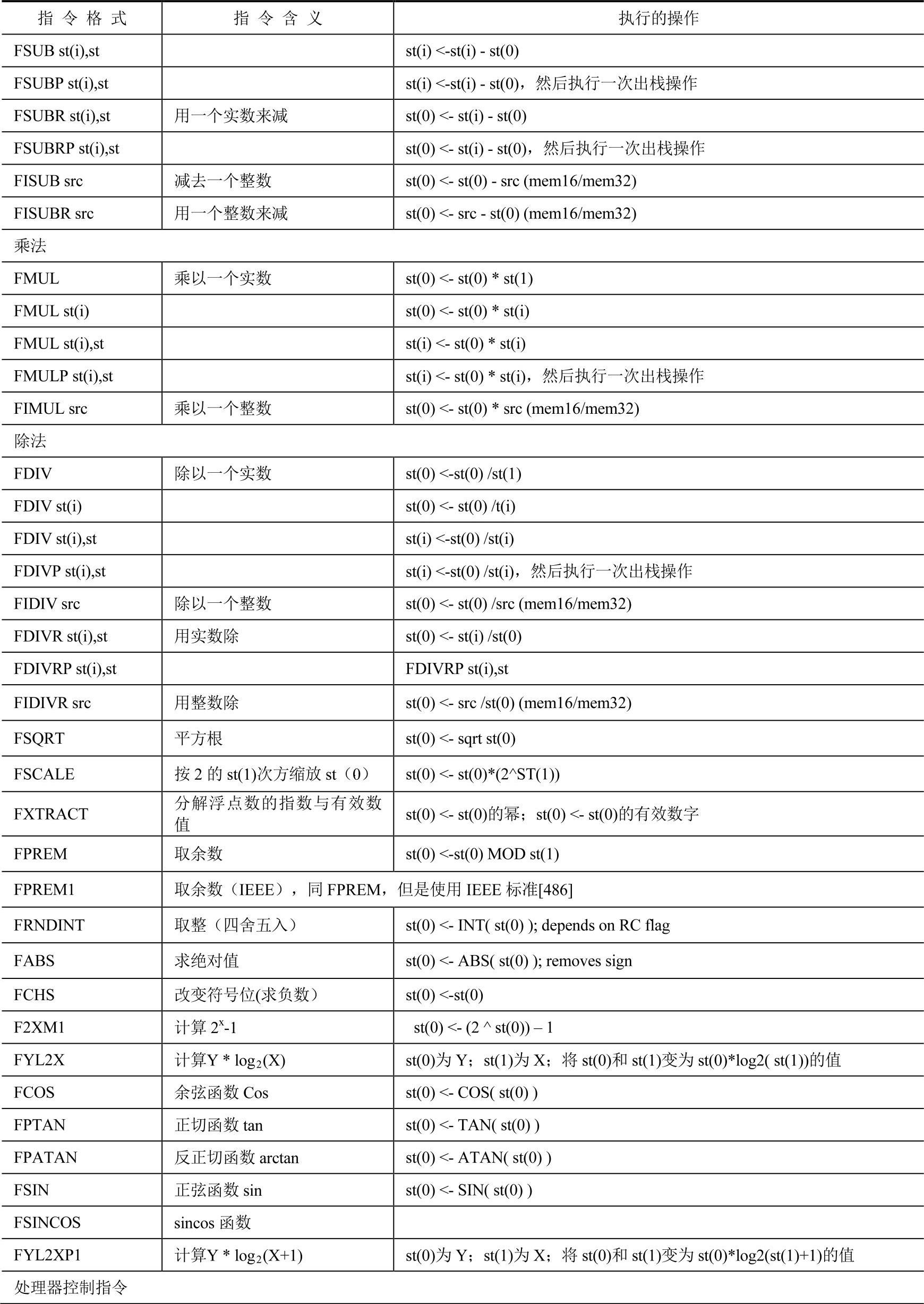

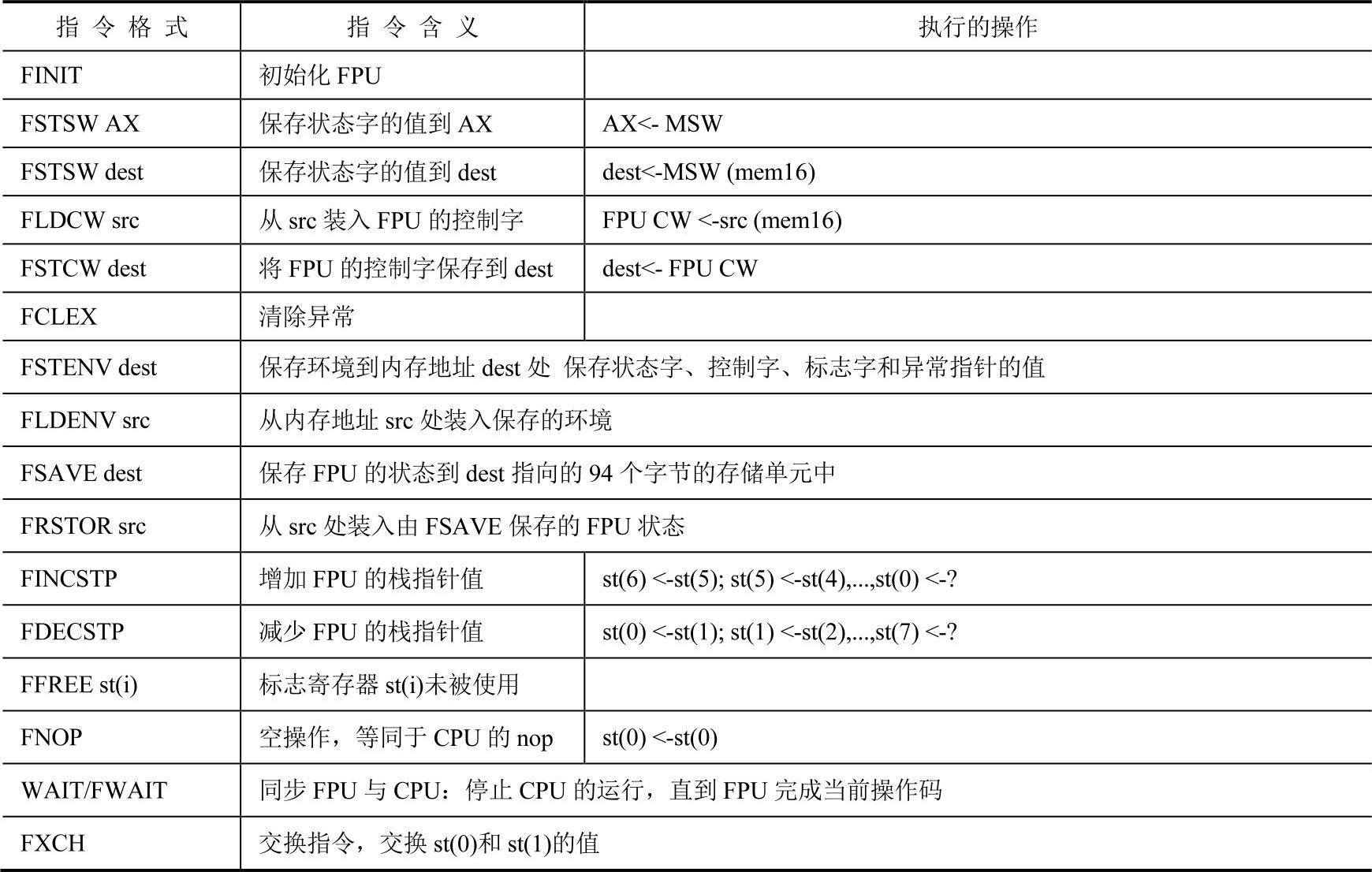

表9-3是数据运算指令列表。

表9-3 数据运算指令列表

(续)

(续)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。