1.什么是I/O接口?I/O接口在系统中起何作用?

解

I/O接口就是连接外设和总线的逻辑电路的总称,它实际上是总线主设备与外设之间的桥梁。

I/O接口的作用是解决CPU与外设连接时由于速度、信号电平、信号格式及时序等的不匹配而存在的矛盾。

2.I/O接口有哪些重要功能?

解

I/O接口应具有数据缓冲、设备选择、信号转换、对外设进行监测和控制、中断请求与管理、可编程等主要功能。但不是要求每种接口都具备上述全部功能,有的只需具有其中某几个功能。

3.什么是I/O端口?它与I/O接口有何关系?

解

I/O端口是指I/O接口电路中能被CPU直接访问的寄存器或某些特定器件(如触发器或锁存器等)。一个I/O接口电路中可能有一个或若干个端口,如命令口、状态口、数据口等;而I/O端口都有确切的地址(或编号)。

4.I/O端口编址方式有哪两种?各适用于什么场合?各有什么优缺点?

解

I/O端口编址方式有两种:与存储器统一编址和I/O单独编址。若CPU没有设置专门的I/O指令,则必须采用与存储器统一编址方式;若CPU设置了专门的I/O指令,则两种方式都可采用。

与存储器统一编址的好处是:首先可以使用访问内存的所有指令访问I/O,这样访问I/O的指令类型多,功能齐全,不仅可以对端口进行数据传送,还可以对端口进行算术、逻辑运算及移位等操作;其次是端口有较大的编址空间。其缺点是:占用了部分内存空间;端口指令的长度增加,执行时间变长;在程序中不易分清访问内存还是访问I/O;端口地址译码器复杂度增加。

I/O单独编址的好处是:端口地址译码器简单;端口指令短,执行速度快;程序中易分清是访问内存还是访问I/O。其缺点是:端口指令类别少,CPU需专门设置I/O指令,且增加了CPU对外的信号线(因为要分出内存读/写与I/O读/写两组信号)。

5.CPU与I/O之间数据传送的方式有哪几种?各有什么特点?

解

CPU与I/O之间数据传送的方式有4种,即无条件传送、程序查询传送、中断传送与DMA传送。有的书中把前两种合在一起称为程序查询传送。

第一种的特点是:接口电路简单,传送时总认为外设处于准备好状态;传送速度不快,效率低。

第二种的特点是:接口电路中需增加握手信号,因为CPU在传送数据前要查询I/O的状态,当I/O准备就绪时才进行数据传送。CPU的大部分时间用于查询等待中,传送效率低。

第三种的特点是:接口电路中需有中断逻辑,当I/O需要与CPU交换数据时,向CPU申请中断,CPU收到中断请求信号后即中断当前任务的执行,根据中断源的向量号转入相应的服务程序,以实现对I/O的数据交换及管理。该方式大大地提高了CPU的利用率,实现了I/O与CPU并行工作。

第四种的特点是:在外设与存储器之间开辟了一条高速数据通道,使外设与内存之间直接交换数据。这一数据通道是通过DMA(Direct Memory Access)控制器来实现的。在DMA方式中,不需要CPU的任何干预,而是由DMA控制器控制系统总线,在其控制下完成数据传送任务。该方式实际上是把外设与内存交换信息的操作和控制交给了DMA控制器,简化了CPU对输入输出的控制,但电路结构复杂,硬件开销大,硬件成本增加。

6.简述DMA传送的过程及该方式有何特点。

解

参看本书对应教材《微机原理与接口技术(第3版)》“7.1.4 CPU与I/O接口之间传送信息的方式”中关于DMA传送方式的阐述。

7.I/O端口地址译码电路在接口电路中的作用是什么?

解

I/O端口地址译码电路的作用是把地址信号和控制信号进行逻辑组合,从而产生对接口芯片的选择信号。

8.I/O端口地址译码电路一般有哪几种结构形式?

解

I/O端口地址译码电路的结构形式一般可分为固定式译码和可选式(用开关和比较器)译码。若按译码电路采用的元器件来分,可分为门电路地址译码和译码器地址译码。另外还可用GAL芯片进行地址译码。

9.I/O地址线用作端口寻址时,高位地址线和低位地址线各有何用途?如何决定低位地址线的条数?

解

一般把I/O地址线分为两部分,一部分是高位地址线,与CPU的控制信号进行组合,经译码电路产生I/O接口芯片的片选![]() 信号,实现系统中的片间寻址;另一部分是低位地址不参加译码,直接连接到I/O芯片,进行I/O接口芯片的片内端口寻址,即寄存器寻址。低位地址线又称为I/O接口中的寄存器寻址线。从系统角度考虑,低位地址线的条数由系统中含有寄存器数目最多的接口芯片来决定。

信号,实现系统中的片间寻址;另一部分是低位地址不参加译码,直接连接到I/O芯片,进行I/O接口芯片的片内端口寻址,即寄存器寻址。低位地址线又称为I/O接口中的寄存器寻址线。从系统角度考虑,低位地址线的条数由系统中含有寄存器数目最多的接口芯片来决定。

10.何谓全译码电路?何谓部分译码电路?

解

I/O电路中所有地址线都参加了译码,该电路称为全译码电路。全译码电路中译出的地址是唯一的,不会产生地址重叠。

I/O电路中只有部分地址信号参加译码,该电路称为部分译码电路。部分译码电路简单,使用地址线少,但译出的地址有重叠。

11.计算本书对应教材《微机原理与接口技术(第3版)》图7.10所示的开关式可选择译码电路的地址范围是多少?

解

根据本书对应教材的图7.10可知,所给译码电路的地址范围是200H~2FFH。因为A9=1是固定的,A3~A8是随开关变化的,可从000000B~111111B变化,A2~A0是随译码器变化的,可从000~111变化,于是地址变化范围是200H~2FFH。上面的译码器LS138译出的I/O口地址只允许读,下面的译码器LS138译出的I/O口地址只允许写。

12.试说明中断过程包括哪些步骤,每步实现哪些基本功能。

解

中断过程包括中断请求、中断判优、中断响应、中断处理和中断返回5个步骤。

·中断请求是需要服务的外设(中断源)向CPU发出的请求信号,该信号分为边沿请求和电平请求。

·中断判优是指当系统中出现两个或两个以上的中断时,而CPU任一时刻只能响应并处理一个中断,所以要解决中断事件优先级的顺序问题,这就要进行中断判优。中断判优就是CPU优先响应几个同时申请的中断源中级别最高的中断源的请求。

·中断响应是CPU中断现正进行的处理任务,转向中断请求相对应的处理程序的过程。在中断响应过程中,要保护断点和现场,关中断,根据向量号转入中断请求所对应的处理程序。

·中断处理就是执行中断服务程序,以完成中断源提出的处理要求。中断服务程序是

根据外设的要求进行的软件编程问题。

·中断返回就是CPU控制权由中断服务程序转移到被中断程序的过程。返回时要部分或全部恢复CPU的现场(包括断点地址)。

13.说明8086/8088响应NMI的过程。说明CPU响应软件中断INT n、NMI和INTR的异同。

解

NMI是不可屏蔽中断请求信号,它不受中断_标志位IF的控制。CPU在响应NMI的请求时,不向NMI的中断源发中断响应周期![]() ,也不用外设接口给出中断矢量号,CPU会自动生成NMI的矢量号2,然后根据2×4和2×4+2查找向量表地址,取出相对应的中断处理程序的入口地址,转入相应的服务程序。

,也不用外设接口给出中断矢量号,CPU会自动生成NMI的矢量号2,然后根据2×4和2×4+2查找向量表地址,取出相对应的中断处理程序的入口地址,转入相应的服务程序。

软件中断INT n、NMI、INTR 3种中断的相同点:

·都使CPU中断当前的程序,转向它们请求相对应的处理程序;

·中断响应过程应解决的问题是一样的(如保护断点和现场,关中断,根据矢量号查找向量表等)。

软件中断INT n、NMI、INTR 3种中断的不同点:

·软件中断不向CPU发中断请求信号,而NMI、INTR请求中断须向CPU发中断请求信号;

·INTR的请求受IF标志位的控制,而NMI和INT n的中断不受IF标志位的控制;

·软件中断INT n和NMI在中断响应期间CPU不发送中断响应周期![]() ,而INTR在响应期间,CPU需向中断控制器8259A发送两个中断响应周期

,而INTR在响应期间,CPU需向中断控制器8259A发送两个中断响应周期![]() ;

;

·软件中断INT n和NMI的矢量号是指令或CPU自动提供的,而INTR的矢量号是中断控制器提供的。

14.说明8259A在单级方式和级联方式下响应中断时,是如何提供中断矢量号的?

解

8259A在单级方式下,8086 CPU在响应中断时向8259A发送两个中断响应周期![]() 在第二个

在第二个![]() 周期把请求中断的中断源的向量号通过数据总线D7~D0送给CPU,CPU可由此获得该中断源的服务程序的入口地址。

周期把请求中断的中断源的向量号通过数据总线D7~D0送给CPU,CPU可由此获得该中断源的服务程序的入口地址。

8259A在级联方式下,中断系统中有主片,又有从片。在中断响应期间,若主片判定所响应的是从某一从片来的中断请求,则它在级联线上发出该从片的识别号,并由该从8258A接收。从片把自己的号与该级联线上的号进行比较,若一致的话,它应在第二个![]() 周期,把自己片内中断源的向量号通过D7~D0送给CPU,以便把控制引导到中断服务程序的入口地址。若检查不是从片发出的中断请求,则一定是主片自己发出的,主片在第二个

周期,把自己片内中断源的向量号通过D7~D0送给CPU,以便把控制引导到中断服务程序的入口地址。若检查不是从片发出的中断请求,则一定是主片自己发出的,主片在第二个![]() 周期把自己的片内中断源的向量号通过D7~D0送给CPU。

周期把自己的片内中断源的向量号通过D7~D0送给CPU。

15.8259A的中断请求寄存器何时置位?何时清零?

解

8259A内部有一个8位中断请求寄存器IRR,存放外部输入的中断请求信号IR0~IR7,当某个IR端有中断请求时,IRR相应的某位置1。可以允许8个中断请求信号同时进入,此时IRR寄存器被置成全1。当中断请求被响应时,IRR的相应位复位。

16.8259A的在服务寄存器(ISR)何时置位,何时清零?IS寄存器有什么作用?

解

8259A内部有一个8位在服务寄存器ISR,对应着8个中断源被服务的状态。当某一中断源的请求被响应时,它对应的在服务寄存器ISR位置1。因为8259A允许中断嵌套,所以在服务寄存器中可能不止一个ISRi置1。在服务寄存器ISR是利用“中断结束”(EOI)命令进行复位的,8259A有3种EOI命令,所以ISR复位有3种情况:一般EOI命令,使当前优先级最高的ISR复位;指定EOI命令(SEOI),使指定的ISR复位;自动EOI命令(AEOI),使刚置1的ISR在中断响应结束时自动复位。

在服务寄存器ISR的作用是:在中断响应时,判优电路把当前最优先的请求与ISR已置1的优先级进行比较,若高于已置1的优先级,则中断已置1的中断服务,而响应当前的中断;若低于已置1的优先级,则阻止响应当前的中断请求。所以ISR是实现中断嵌套的一种有效方法。

17.8259A有哪几种优先方式?各是怎样工作的?

解

8259A提供了两种优先方式,即固定优先和循环优先。

在固定优先方式下,所有的IRQ都有固定的优先级别,并且这种优先级别不随中断事件的出现和处理而改变。8259A加电后就处于这种方式,且IR0优先级最高,IR7优先级最低。对于这种优先顺序,用户可以根据自己的需要通过程序来改变它,使它处于另外一种固定优先顺序。只要设定一次就无须再改变它,它就保持这种优先顺序。

在循环优先方式下,中断源的优先顺序是变化的。这种方式使各中断源处于同等地位,被处理的机会均等。在此方式下,当某一中断源的服务被处理后,该中断源应变为最低优先级,以便其他中断请求有被处理的机会。

18.8259A的判优电路只在中断请求、中断响应或中断返回时起作用。试说明在正常全嵌套方式下:

①若某一IS寄存器已置位,该PIC再次发出中断请求的条件是什么?

②在中断响应时,某一IS寄存器置位的条件是什么?

③若一PIC中有多个IS寄存器置1,在该PIC收到非特指EOI命令时,哪个IS被复位?

解

在正常全嵌套方式下:

①若某一IS寄存器已置位,该8259A再次发出中断请求的条件一定是某个中断源的优先级别比已置位的中断源的级别高;

②在中断响应时,某一IS寄存器置位的条件是它的级别比CPU正在处理的中断事件的级别高;(https://www.daowen.com)

③若一PIC中有多个IS寄存器置1,在该PIC收到非特指EOI命令时,一定是正被CPU处理的(优先级最高)那个中断源的IS被复位。

19.在PIC收到![]() 信号时,单级PIC如何决定发出哪个中断源的类型号?多个PIC级联时,主PIC如何决定是自己发出矢量号还是从PIC发出矢量号?从PIC怎么知道应该由自己发出矢量号?

信号时,单级PIC如何决定发出哪个中断源的类型号?多个PIC级联时,主PIC如何决定是自己发出矢量号还是从PIC发出矢量号?从PIC怎么知道应该由自己发出矢量号?

解

在PIC单级方式下,若某一时刻只有一个中断源请求中断,在CPU响应中断时由PIC发出该中断源所对应的中断类型号。若某一时刻有若干个中断源同时请求中断,在CPU响应中断时由PIC发出当前优先级最高的中断源(由判优电路决定)所对应的中断类型号。

在PIC级联方式下,若某一时刻只有一个中断源请求中断,在CPU响应时由主PIC或者从PIC发出该中断源所对应的中断类型号。若某一时刻有若干个中断源同时请求中断,首先由判优电路判断其级别,找出当前请求的中断源中级别最高的,若级别最高的是主PIC的中断源,则在CPU响应时由主PIC发出该中断源对应的中断类型号;若级别最高的是从PIC的中断源,则在CPU响应时由该从PIC发出该中断源对应的中断类型号。

从PIC是通过下面的方法发出自己的类型号的。在中断响应期间,若主PIC判定所响应的是从某一从PIC来的中断请求,则主PIC在级联线上发出该从PIC的识别号,并由从PIC接收。从PIC将自己的号与该级联线上的号相比较,若一致的话,它应在此后的![]() 响应周期,把自己片内的中断源的类型号通过D7~D0发送给CPU。

响应周期,把自己片内的中断源的类型号通过D7~D0发送给CPU。

20.为什么主PIC在既接从PIC又接直接输入的请求时,不用IR0接从PIC?其根本原因是什么?对于8259A的这一问题,你能提出什么改进建议吗?

解

主PIC的中断输入端在既接从PIC又接直接输入的请求时,不用主片的IR0接从PIC的原因是:在非级联的IR有效时,主PIC在级联线CAS2~CAS0上的驱动信号为000,就好像让IR0上的从PIC响应一样。若此时真有一个从PIC接到主PIC的IR0输入,它响应![]() 周期而发出的类型号将与主片非级联IR发出的类型号在总线上冲突而产生错误。所以,只有当主片的IR1~IR7全接上从片时,主片的IR0才能够接从PIC。

周期而发出的类型号将与主片非级联IR发出的类型号在总线上冲突而产生错误。所以,只有当主片的IR1~IR7全接上从片时,主片的IR0才能够接从PIC。

要克服这一问题,可以在非级联的IR有效时,主PIC在级联线之外,用另一条线接到所有从PIC,以指示级联线上的信号是否有效。

21.当某一请求正在服务时,若要允许比它优先级低的设备中断它,8259A应进入什么方式?如何进入这种方式?在此方式下,该用哪种EOI命令使它复位?为什么?

解

当某一请求正在服务时,若要允许比它优先级低的设备中断它,8259A应进入特殊屏蔽方式(SMM)。进入该方式的步骤是:首先屏蔽该服务级(假如该级为IR5,则使IMR的IM5置1),然后用操作命令字OCW3可进入特殊屏蔽方式(该字的D6 D5=11,进入SMM方式)。

在这种方式下,由于它打乱了正常的全嵌套结构,被处理的程序不见得是当前最优先的事件,所以不能用非指定EOI命令来使它的ISR位复位,应使用指定的EOI命令使它的ISR复位。

22.在8259A的自动循环优先中,进入AEOI循环方式后,优先级在什么时候改变?怎样改变?

解

在AEOI循环方式下,如同AEOI方式一样,在中断响应结束时将相应的IS复位,同时将其优先级变为最低(优先级的“底”)。

23.8259A的AEOI方式有什么优点?又有什么缺点?有什么办法可克服这些缺点?

解

AEOI的优点是服务结束时,没必要向PIC发出任何EOI命令;缺点是无法实现中断嵌套(优先级中断或优先级排队),若想实现优先中断,则有“过嵌套”的危险,容易造成“堆栈溢出”,而使系统崩溃。防止的方法是,使所有的中断服务都不允许嵌套(即在中断处理中,保持IF=0)。

24.在本书所对应教材《微机原理与接口技术(第3版)》图7.19所示的PC-AT中断结构中,IRQ8~IRQl5的各中断源有哪几级屏蔽?

解

对PC-AT计算机,其INTR中断源包括如图7.4所示的屏蔽。

图7.4 中断多级屏蔽框图

从图7.4可以看出:对IRQ8~IRQ15,除了相应的I/O设备本身的中断屏蔽(若有的话)外,经过从PIC(对IRQ15来说是M7)、主PIC(M2)两级屏蔽,再到达CPU,经过CPU内的又一级IF屏蔽,IRQ8~IRQ15才能被响应和处理。这样不考虑I/O设备本身的屏蔽,从PIC的IRQ到CPU共经过三级屏蔽。25.试给AT计算机写出一段并行打印机的中断驱动程序,中断请求为IRQ7。

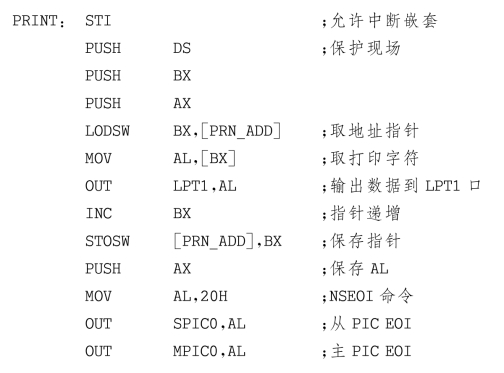

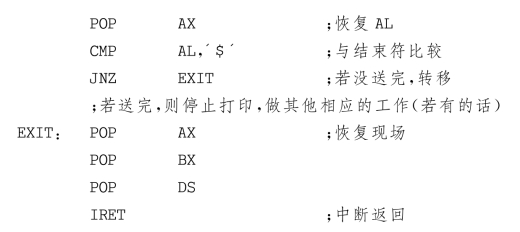

解

打印机的中断处理程序要考虑如下因素:

·打印数据的存放位置(开始地址)和排列顺序(地址生成是递减或递增);

·打印字符数或者结束符,它决定了打印的结束条件。

在这个例子中,不考虑打印机的打印格式控制问题。

这里只给出该中断处理程序的结构,并假定:

①下一个打印字符的地址指针存放在内存的PRN_ADD内;

②数据按递增排列;

③结束符是ASCII字符′$′;

④打印中断处理程序入口是′PRINT′。

26.若在对8259A的中断处理中,没有以某种方式执行EOI命令,会出现什么现象?

解

若在中断处理中没有执行EOI命令,则该中断相应的ISR会一直是“1”,将屏蔽该级及其以下的所有中断源。将会直接看到该中断只被响应一次,再也不会产生中断。

27.在8259A OCW2中有几种EOI命令?它们各将哪个ISRi复位?

解

在8259A的OCW2中,凡EOI=1的命令都是EOI命令,有以下4种。

·非指定EOI(NSEOI)。将ISR中等于“1”的ISRi位中优先级最高者复位。

·指定EOI(SEOI)。将ISR中指定的ISRi复位。

·NSEOI循环。将ISR中等于“1”的ISRi位中优先级最高者复位,并将它变为最低级。

·SEOI循环。将ISR中指定的ISRi复位,并将它变为最低级。

28.若读8259A的在服务寄存器ISR=01001100B,说明哪几个中断源已被服务?若8259A工作在正常全嵌套、固定优先方式(IR0优先级最高,IR7优先级最低),问CPU现正在为哪个中断源服务?

解

由于在服务寄存器ISR=01001100B,凡是ISRi位为“1”的说明其中断源已被服务过,所以,IRQ2、IRQ3、IRQ6中断源都被服务过。

如果8259A工作在正常全嵌套、固定优先级方式,CPU正在为IRQ2服务。因为在被服务的3个中断源中它的级别最高。

29.假若某PIC中没有提供IS(在服务)寄存器,有没有其他办法防止比其优先级低的请求中断它?试说明你的办法的基本原理。

解

因为PIC中的在服务寄存器ISR相当于中断源优先级别的一个标志,判优电路根据其级别来判优,所以可以采用两种办法来实现判优,即采用硬件或者软件的办法。若PIC中没有ISR,用硬件把各个中断源的输入信号通过优先权编码器编码,防止低优先级的中断请求被允许申请。用软件实现的话,可以在内存中设置一个或几个单元作为中断源的优先级别的标志,每次中断响应后通过程序来判断其中断源的优先级别,然后CPU决定是否为其中断服务。

30.8259A在什么场合提供了利用“查询命令”来了解中断源的方法?若用这种方法来扩充中断源的数目到64个以上,试画出本书对应教材《微机原理与接口技术(第3版)》图7.27的IR73的中断处理程序中,使相应IS复位的详细流程图,并作简要说明。

解

请参看本书对应教材《微机原理与接口技术(第3版)》“7.4.2 8259A的工作原理”中关于中断状态及多级级联查询方式的阐述。

说明:IR73的中断处理程序和其他中断处理程序一样,也必须在中断服务结束时,向IR73的PIC发出适当的EOI命令,以使其IS73位清零。但向其发EOI命令时要注意IR73所在PIC的端口地址。如果发到别的PIC中就不起作用了。IS73复位的流程图从略。

31.什么是中断响应周期?在中断响应周期中CPU和8259A一般要完成哪些工作?

解

32.可编程中断控制器8259A协助CPU处理哪些中断事务?

解

8259A协助CPU处理以下中断事务:

·可进行优先级排队管理,把多个中断源汇接在一起,进行判优后把当前级别高的中断源的请求信号发给CPU,使CPU可以处理多级中断源;

·可以进行中断请求的屏蔽和开放,可灵活地在8259A内部单独屏蔽某一级中断(CPU内部的IF具有屏蔽或开放所有的INTR中断源的功能);

·在其内部设置在服务标志位ISRi,可以实现中断嵌套(使CPU优先服务级别高的中断源);

·在中断响应期间可以向CPU提供中断向量号。

33.8259A具有哪些工作方式和中断操作功能?指出与这些功能相对应的命令字(ICW/OCW)的内容。

解

8259A通过编程可选择多种工作方式,主要有:

·中断请求触发方式,包括边沿触发方式、电平触发方式;

·中断源屏蔽方式,包括正常屏蔽方式、特殊屏蔽方式;

·优先级排队方式,包括正常全嵌套方式、特殊全嵌套方式、固定优先方式、循环优先方式;

·中断结束处理方式,包括自动中断结束方式(AEOI命令)、非自动中断结束方式(指定EOI命令和非指定EOI命令)。

8259A内部有4个初始化命令字和3个操作命令字,由这7个命令字来设置其工作方式和中断操作的功能。其工作方式和中断操作功能以及这些功能相对应的命令字如下:

·中断请求触发方式的设置,单片PIC或级联方式的选择(ICW1);

·中断向量号的设置(ICW2);

·中断级联方式的设置,即主片和从片方式字分别写(ICW3);

·中断嵌套、中断结束等方式的设置,包括正常全嵌套和特殊全嵌套方式、正常结束和自动结束中断方式、缓冲和非缓冲方式(ICW4);

·中断屏蔽操作方式的设置(OCW1);

·非自动中断结束方式、中断排队方式等操作的选择,包括指定EOI和非指定EOI方式选择、固定优先和循环优先方式选择(OCW2);

·进入/退出特殊屏蔽操作方式,即读寄存器(IRR和ISR)状态的操作选择(OCW3)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。