例6.1 设计一种应用于独立请求方式的总线仲裁器,进行固定优先级判决。

解

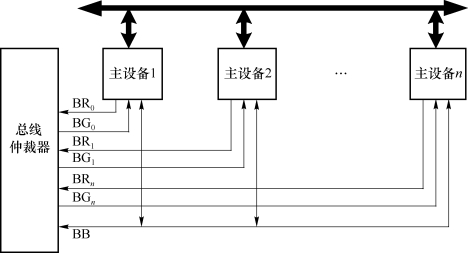

独立请求方式的总线仲裁器如图6.1所示。

图6.1 独立请求方式的总线仲裁器

在独立请求方式中,总线仲裁器要接收n个请求信号,并产生n个应答信号。题目要求按照固定优先级仲裁,就是将总线控制权给予优先级最高的一个申请者。对于优先级的判决,可以使用优先级编码器实现,产生的优先级信号经过译码器就可以产生应答信号。在设计中,需要注意,一旦应答产生,需要屏蔽新的申请信号,以防止更高优先级的申请打断已经授权的总线操作周期。

以8个设备仲裁为例,设计框图如图6.2所示。

图6.2 8个设备仲裁设计框图

8个申请输入经优先级编码后,产生3 bit优先级编码信号,经译码后产生应答。忙判决电路实际上是一个全与门或者全或门(视输出信号的有效电平而定)。当产生优先级判断后,通过选择器,选出被授权的申请信号,作为锁存控制信号,锁定当前的输入,保证在申请者没有放弃总线之前,不会产生新的判决。该电路要求,申请信号应在总线使用周期内持续有效。

应该注意,这个选择/锁存结构不是必需的。根据总线操作的要求,各总线设备在总线忙信号有效时,不能提出新的申请。在这种情况下,不需要这部分电路。

例6.2 在全互锁和半互锁方式中,如果访问一个不存在的设备,可能发生什么问题?设计一种电路,避免这个问题的发生。

解

在全互锁和半互锁方式中,如果访问一个不存在的设备,因为没有设备能够发出应答的ACK信号,主设备会认为被访问的设备一直不能收到数据,从而持续等待ACK信号,导致总线操作不能继续下去,形成死锁。

要避免这一问题,可以设计电路,在某设备不存在时,将访问该设备的READY信号作为ACK信号送回主设备,从而结束当前的操作,电路如图6.3所示。

图6.3 例6.2图

在该电路中,要求总线设备或插槽提供一个设备存在的指示信号。如果设备存在,选择器就将设备的ACK信号作为应答信号送出;如果设备不存在,选择器就将访问该设备的READY信号作为应答信号送回,保证访问该设备的操作正常结束,不会死锁。

例6.3 在有若干插槽的PCI母板上,要求由一个特定的ID寄存器对各插槽进行配置操作的选择,设计相关电路。

解

PCI设备的配置操作的选择是由IDSEL信号决定的。每个插槽均有独立的IDSEL信号,互不连接。由ID寄存器进行选择时,只需要对该ID寄存器进行译码即可。电路示意如图6.4所示。

图6.4 例6.3图

例6.4 两个一般的USB设备连接在一起,是否能进行通信?为什么?两个USB主机设备连接在一起,是否能进行通信?为什么?(https://www.daowen.com)

解

两个一般的USB设备连接在一起,不能进行通信。因为USB总线的通信是由USB主机控制的,如果总线上没有USB主机,就不能工作。

两个USB主机设备连接在一起,一般也不能进行通信。因为一个USB总线上只能由一个USB主机进行控制。但如果在其中一个USB主机上安装特定的软件,禁止其主机功能,同时提供一般的USB设备功能,将其转化为一般的USB设备,则有可能进行通信。

例6.5 在ISA总线上,设计一个简单8位并行输出接口。

解

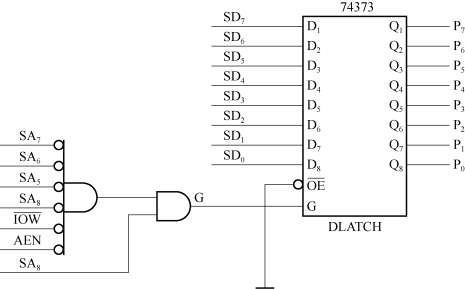

先选定该输出接口的口地址,不要与原先存在的其他接口地址发生冲突。假定口地址是100H。图6.5就是一个简单8位并行输出接口电路。

图6.5 简单8位并行输出接口电路

对输出接口,输出寄存器(或锁存器)是必需的。这里使用8D锁存器74373。G是锁存器的门控信号,高电平有效。

注意:这里的I/O译码采用了部分译码,只用了I/O地址线的低10位信号线中的5条,其他线为任意。所以,它的地址不是唯一的。

加AEN信号,就是在DMA传输(AEN=1)时禁止I/O译码,因为在单地址DMA传输时,地址线上传送的是“存储器”地址,而不是I/O地址。

加入了![]() 信号,只在写I/O时,才产生对锁存器写入的G命令。

信号,只在写I/O时,才产生对锁存器写入的G命令。

在该例中,SA9~SA0=01000×××××。

并行接口的输入数据直接连数据线SD7~SD0。

并行接口的输出是锁存器的Q输出,即P7~P0。

对于简单接口,没必要一定要用通用I/O接口芯片,用一般电路搭建往往更节省空间和成本。只有在设计选通接口时,通用芯片才能显示其优越性。

例6.6 描述![]() 信号的用法。

信号的用法。

解

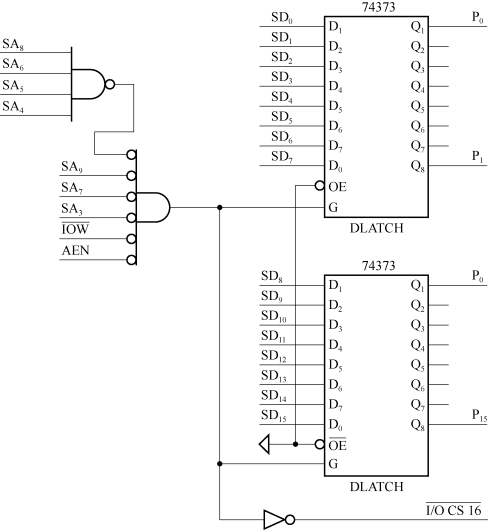

ISA总线有一个“16位到8位”变换器,还有8位I/O接口,只要与ISA数据低位SD7~SD0相接,其I/O地址就可以连续安排,以便于和使用8088 CPU的IBM-PC/XT相兼容。当使用ISA总线实现16位I/O接口时,该接口应向总线返回一个![]() 信号,以使该变换电路不起作用,使8086 CPU的D7~D0和SD7~SD0、D15~D8和SD15~SD8直接相连,见图6.6。

信号,以使该变换电路不起作用,使8086 CPU的D7~D0和SD7~SD0、D15~D8和SD15~SD8直接相连,见图6.6。

图6.6  信号的用法电路图

信号的用法电路图

因为后面的其他习题都是以ISA总线为基础设计的,所以,这里就不再多举例了。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。