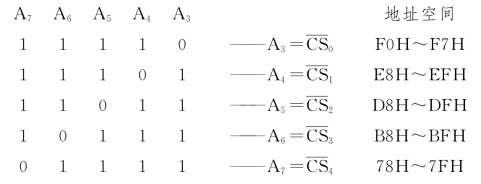

例5.1 某系统有地址线8条A7~A0,地址空间为0~255。若使用的芯片内最多有8字节单元,则地址线A2~A0用于片内单元选择,而A7~A3用于形成片选信号,设计该译码电路。

解

显然,这是8位数据总线的系统,有3种方案可供选择。

(1)全译码

对A7~A3 5条信号进行全译码,有32种可能的安排。每种安排选择了全部空间的1/32,即8字节空间。若某些空间暂时不用,以后必要时仍可利用。其每一芯片都有唯一的地址空间。

(2)部分译码

若系统没必要使用全部256字节的空间,如只需使用其中的80字节空间就足够了,可以采用部分译码,如只对A6~A3译码,或者只对A7~A4(4条线)译码。这样译码地址不是唯一的,它占用了几乎全部256字节的地址空间。人们习惯上使用其选中的低地址空间,这样每一译码输出(即每一芯片实际占用了8字节空间的两倍,即16字节空间)占整个空间的1/16。

若某些未利用空间以后要用,注意,应让高位地址线是“任意”的,不参与译码,而不要让低位地址线是任意的。高位地址线任意所占用或留下的空间是地址连续的。

(3)线选译码

在这种情况下,直接用A7,A6~A3等5线作为片选信号,无须译码。这样可以选中5个芯片,如:

这种“五中取一”的方法只有5种可能,它的每个芯片占用全部空间的1/5(而不是每个芯片占用整个逻辑系统空间的1/2,因为其他线的电平不是“任意”的,所以必须为“1”),不能使用的空间为整个空间的4/5,它占用的逻辑空间也是唯一的。如上面所示。

例5.2 用6264 SRAM在ISA总线上扩充128 KB。

解

首先决定基地址,因为片内单元数是N=8 KB,数据总线宽度M=2 B,所以

![]()

因此,可选择的基地址应是16 KB的倍数,如000000H、008000H、010000H、018000H等。所以应对SA14~SA23等地址线译码,扩充128 KB需8片6264。

在选定了基地址之后,用译码_器译出两块连续的基地址来安排该扩充的存储器。译码生成4个片选信号,再与A0和![]() 形成8个片选信号,分别接8个6264芯片的

形成8个片选信号,分别接8个6264芯片的![]() 。图5.4是基地址为000000H时的译码逻辑。

。图5.4是基地址为000000H时的译码逻辑。

图5.4 例5.2的地址译码电路

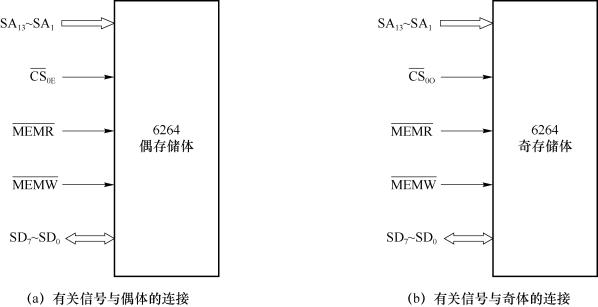

片选信号![]() 选择偶存储体,而

选择偶存储体,而![]() 选择奇存储体芯片。这样,利用ISA总线的

选择奇存储体芯片。这样,利用ISA总线的![]() 和

和![]() 可分别与存储器的

可分别与存储器的![]() 和

和![]() 直接连接,而SA13~SA1与存储器的地址线A12~A0相连,如图5.5所示。

直接连接,而SA13~SA1与存储器的地址线A12~A0相连,如图5.5所示。

图5.5 有关信号与6264的连接图

这里没有考虑存储器的存取速度和总线周期是否匹配的问题,即没有考虑存储器接口的“等待逻辑”的设计问题。

例5.3 若某Cache的存取时间是20 ns,主存储器的存取时间是120 ns,某段时间内访问内存5 000次,其中,访问Cache 4 820次。求Cache的命中率、Cache的效率、主存储器的平均速度各是多少?

解

命中率:

![]()

平均存取速度:

![]()

Cache的效率:

![]()

例5.4 某8位CPU的总线接口信号是:

·A15~A0为地址总线,可直接寻址64 KB的空间;

·D7~D0为数据总线;

·![]() 分别为读命令和写命令。

分别为读命令和写命令。

若用一片6264作为存储器,问:

①该片可安排在哪些空间?

②片内存储单元用哪些地址线来选择?(https://www.daowen.com)

③片选信号用哪些信号来选择?

解

6264是8 KB×8位存储芯片,片内选择需要13条地址线,为A12~A0,这样片选信号要用A15~A13来形成。因此:

①A15~A13 3条线有8种组合,可安排在8个空间之一:0000H~1FFFH、2000H~3FFFH、4000H~5FFFH等;

②A12~A0;

③A15~A13。

读者可以画出完整的电路图,不考虑存取速度。

例5.5 若用6264 SRAM在8086 CPU系统中扩充存储器,其可能的地址有几种?

解

8086有20条地址线A19~A0,有16位数据线D15~D0。其中,A13~A1作为片内选择,剩下的A19~A14共6条线形成片选信号,共有64种可能。〔6264为8 K×8位RAM芯片,在16位总线上扩充内存时,必需两片两片地向上累加。每两片组成16 KB的存储容量,其起始地址必须是16 KB的整数倍。因此,1 MB等于220 B的存储空间,按16 KB(214)的块来划分,共有220/214=26=64块。〕

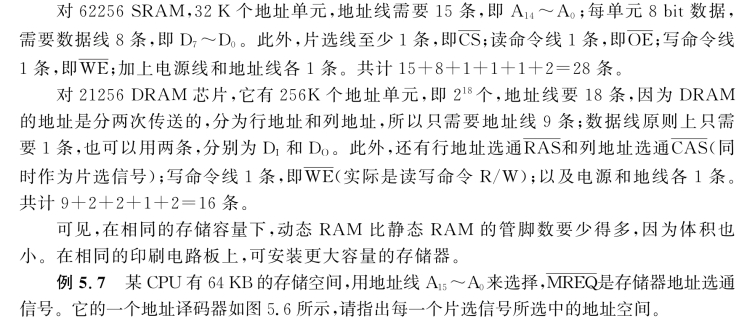

例5.6 对相同容量的存储器芯片,如62256 SRAM(32 K×8位)和21256 DRAM(256 K×1位),其管脚数各是多少?

解

解

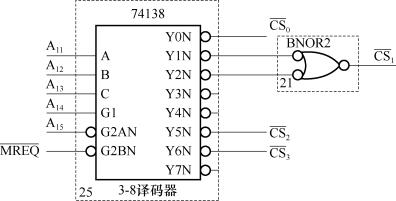

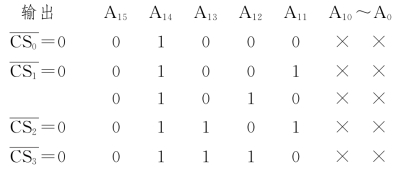

从图5.6中可以看出:为使译码器生效,必须使![]() =L,A15=L,A14=H,即

=L,A15=L,A14=H,即

图5.6 74318译码器

所以,它们选中的地址空间分别是:

①![]() ,4000H~47FFH,2 KB;

,4000H~47FFH,2 KB;

②![]() ,4800H~57FFH,2 KB;

,4800H~57FFH,2 KB;

③![]() ,6800H~6FFFH,2 KB;

,6800H~6FFFH,2 KB;

④![]() ,7000H~77FFH,2 KB。

,7000H~77FFH,2 KB。

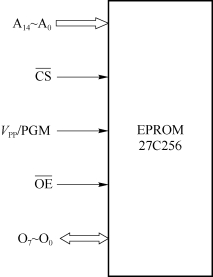

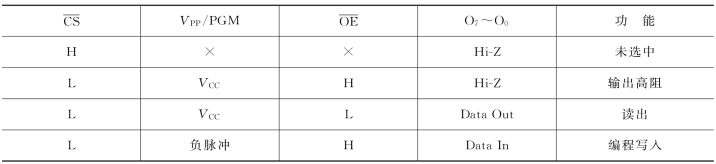

例5.8 有EPROM芯片27C256,存储容量为32 K×8位,管脚图及真值表分别如图5.7和表5.6所示。试设计它与某CPU的逻辑连接,假定该CPU的总线信号是:

图5.7 27C256引脚图

表5.6 27C256真值表

·A15~A0为地址总线;

·D7~D0为数据总线;

·![]() 为读命令及写命令。

为读命令及写命令。

只考虑该EPROM正常工作的逻辑,而不考虑它的编程写入操作。

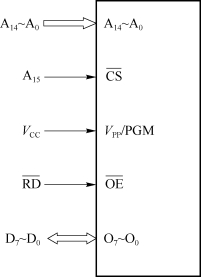

解

从题意可知,这是8位数据总线(D7~D0)。CPU直接寻址空间是64 KB。

EPROM(32 K×8位)的容量是整个空间的一半。因此,没必要用地址译码器,只用地址的最高位A15作为片选信号就可以了。这有两种选择:ROM放在地址空间的上半部分或下半部分。下面以安排在一半部分为例来设计,如图5.8所示。

图5.8 接口信号与27C56的连接图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。