UART0包含11个8位寄存器,UART1包含13个8位寄存器,分别介绍如下(其中x表示0或1)。

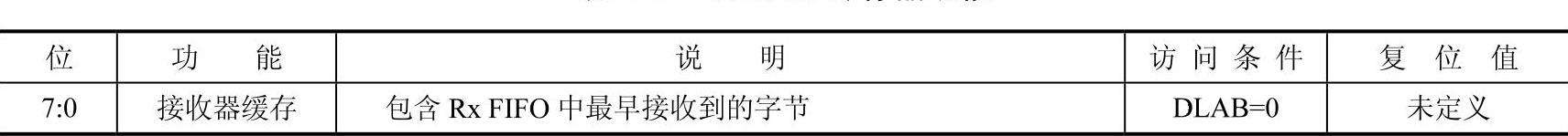

1.UART接收缓存寄存器UxRBR

UxRBR是UART Rx FIFO的最高字节。它包含了最早接收到的字符,可通过总线接口读出。接收数据低位在先,即LSB(bit0)为最先接收到的数据位。如果接收到的字符小于8位,则未使用的高位数据MSB以0填充。

如果要访问UxRBR,UxLCR寄存器的除数锁存访问位(DLAB)必须为0。

UxRBR为只读寄存器,其功能如表4-5所列。

表4-5 UxRBR寄存器功能

由于PE、FE和BI位与RBR FIFO顶端的字节相对应(即下次读RBR时读出的字节),因此,将接收的字节及其状态位成对读出的正确方法是先读UxLSR,再读UxRBR。

2.UART发送保持寄存器UxTHR

UxTHR是UART Tx FIFO的最高字节,它包含了Tx FIFO中最新的字符,可通过总线接口写入。发送数据低位在先,即LSB(bit0)代表最先发送的位。

如果要访问UxTHR,UxLCR寄存器的除数锁存访问位(DLAB)必须为0。

UxTHR为只写寄存器,其功能如表4-6所列。

表4-6 UxTHR寄存器功能

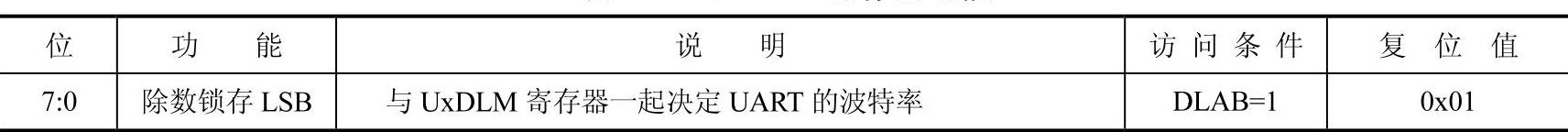

3.UART除数锁存LSB寄存器UxDLL

UxDLL寄存器与UxDLM寄存器一起决定UART的波特率。如果要访问UxDLL,UxLCR寄存器的除数锁存访问位(DLAB)必须为1。UxDLL为读/写寄存器,其功能如表4-7所列。

表4-7 UxDLL寄存器功能

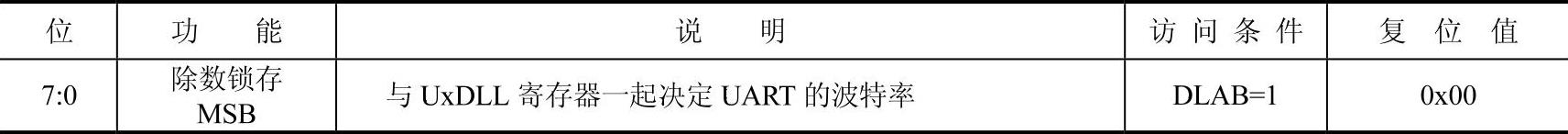

4.UART除数锁存MSB寄存器UxDLM

UxDLM寄存器与UxDLL寄存器一起决定UART的波特率。

除数锁存是波特率发生器的一部分,它保存了用于产生波特率时钟的VPB时钟(Fpclk)分频值,UxDLL和UxDLM寄存器一起构成一个16位除数,UxDLL包含除数的低8位,UxDLM包含除数的高8位。由于除数不允许为0,因此值0x0000被看作是0x0001。

波特率时钟必须是波特率(baud)的16倍,计算公式如下:

16×baud=Fpclk/(UxDLM,UxDLL)

如果要访问UxDLM,UxLCR寄存器的除数锁存访问位(DLAB)必须为1。

UxDLM为读/写寄存器,其功能如表4-8所列。

表4-8 UxDLM寄存器功能

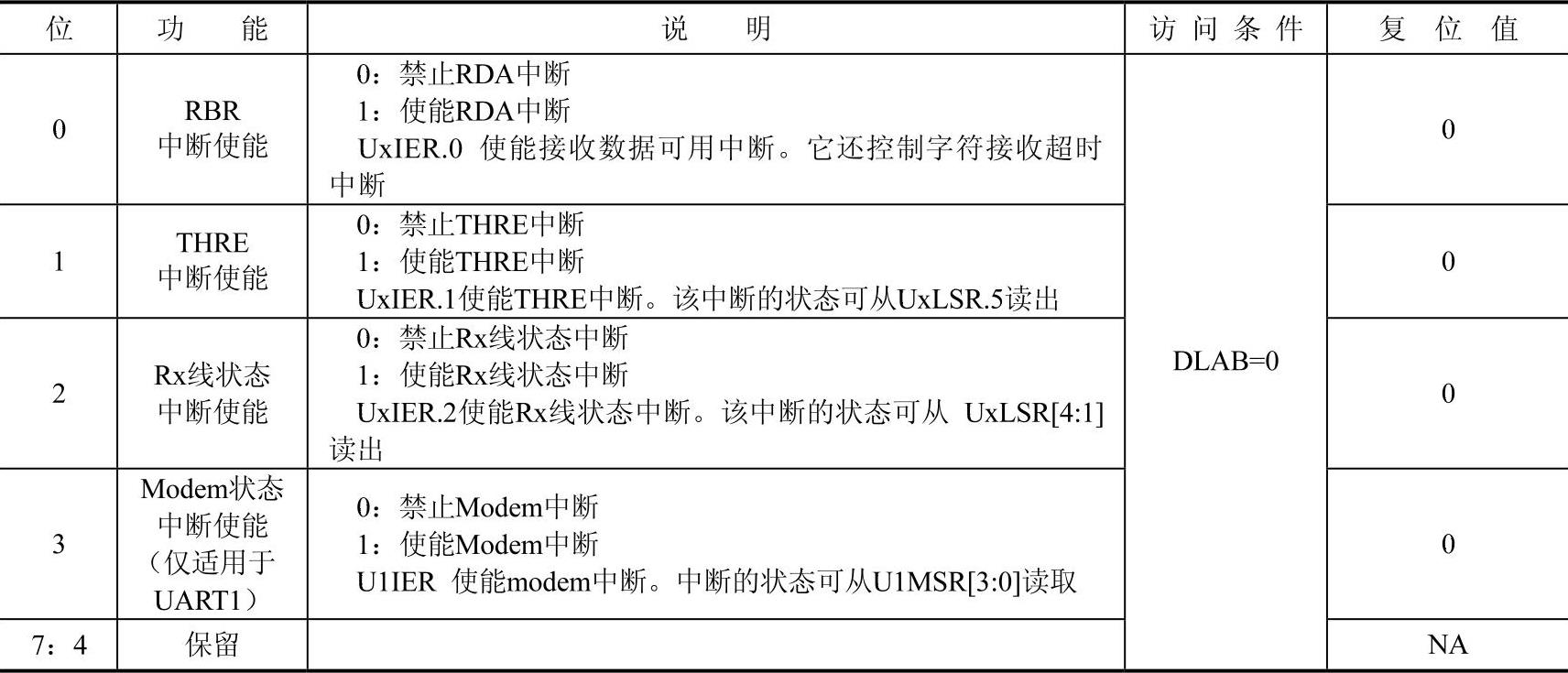

5.UART中断使能寄存器UxIER

UxIER寄存器用于使能4个UART中断源,其功能如表4-9所列。

表4-9 UxIER寄存器功能

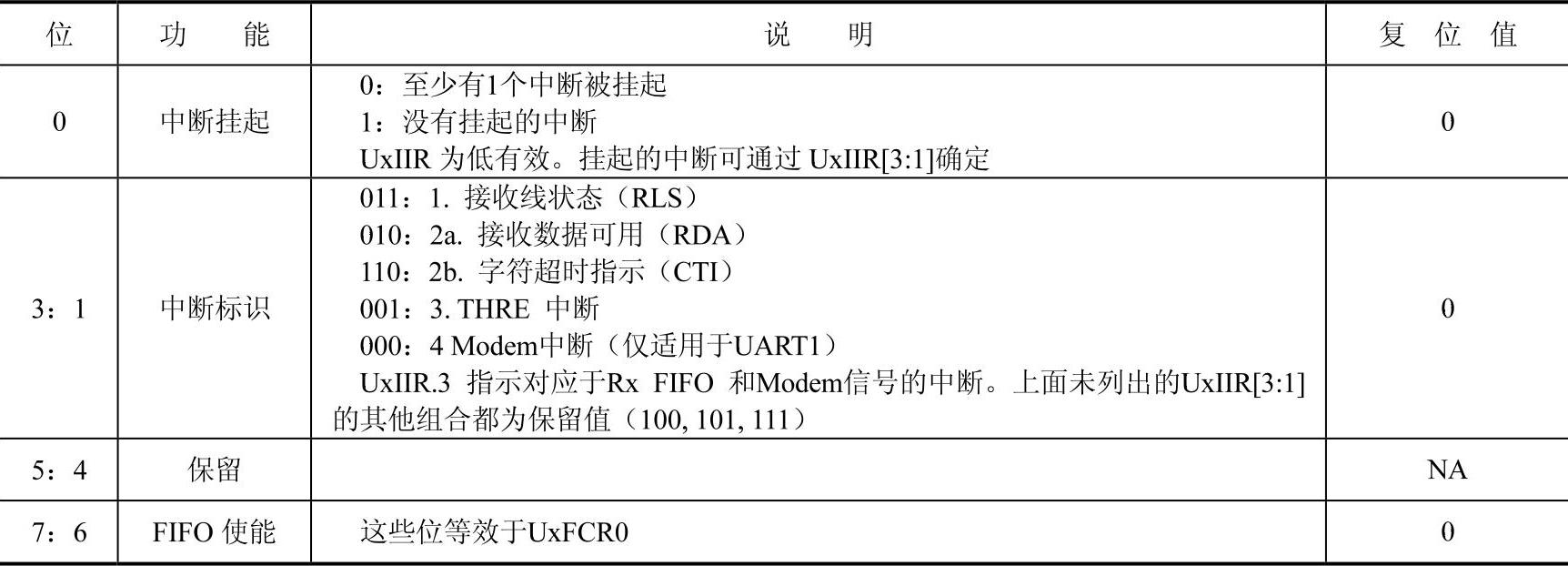

6.UART中断标识寄存器UxIIR

UxIIR寄存器提供状态代码用于指示一个挂起中断的中断源和优先级。在访问UxIIR过程中,中断被冻结。如果在访问UxIIR时产生了中断,该中断被记录,下次访问UxIIR时可读出。

UxIIR为只读寄存器,其功能如表4-10所列。

表4-10 UxIIR寄存器功能

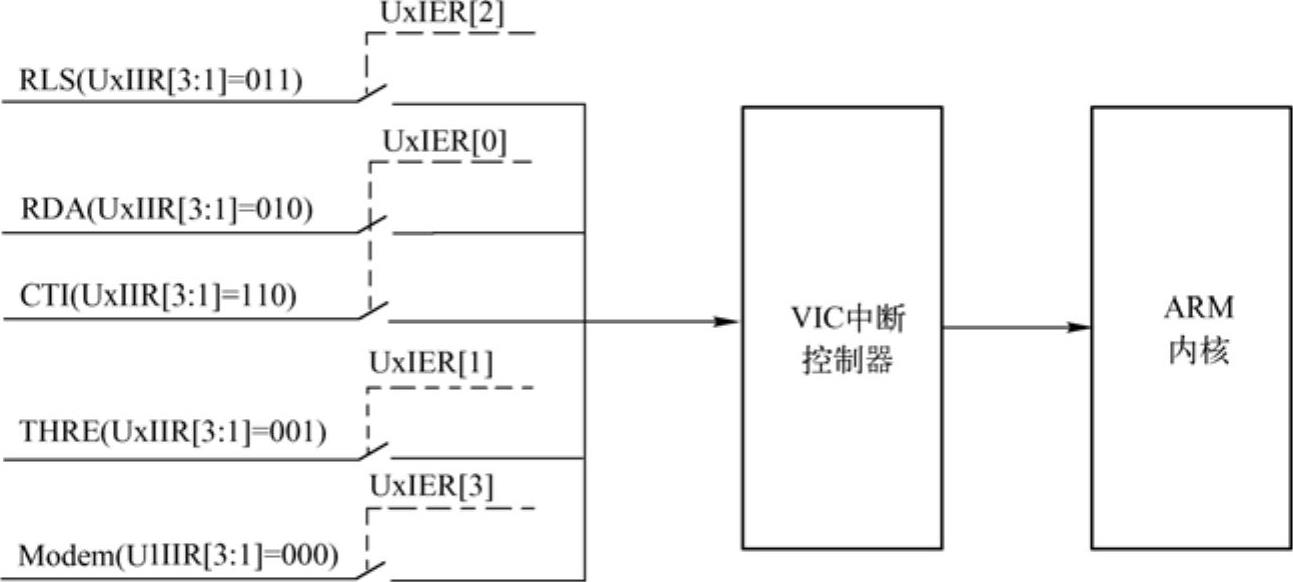

UART中断源和中断使能关系如图4-2所示。

图4-2 UART中断源和中断使能关系

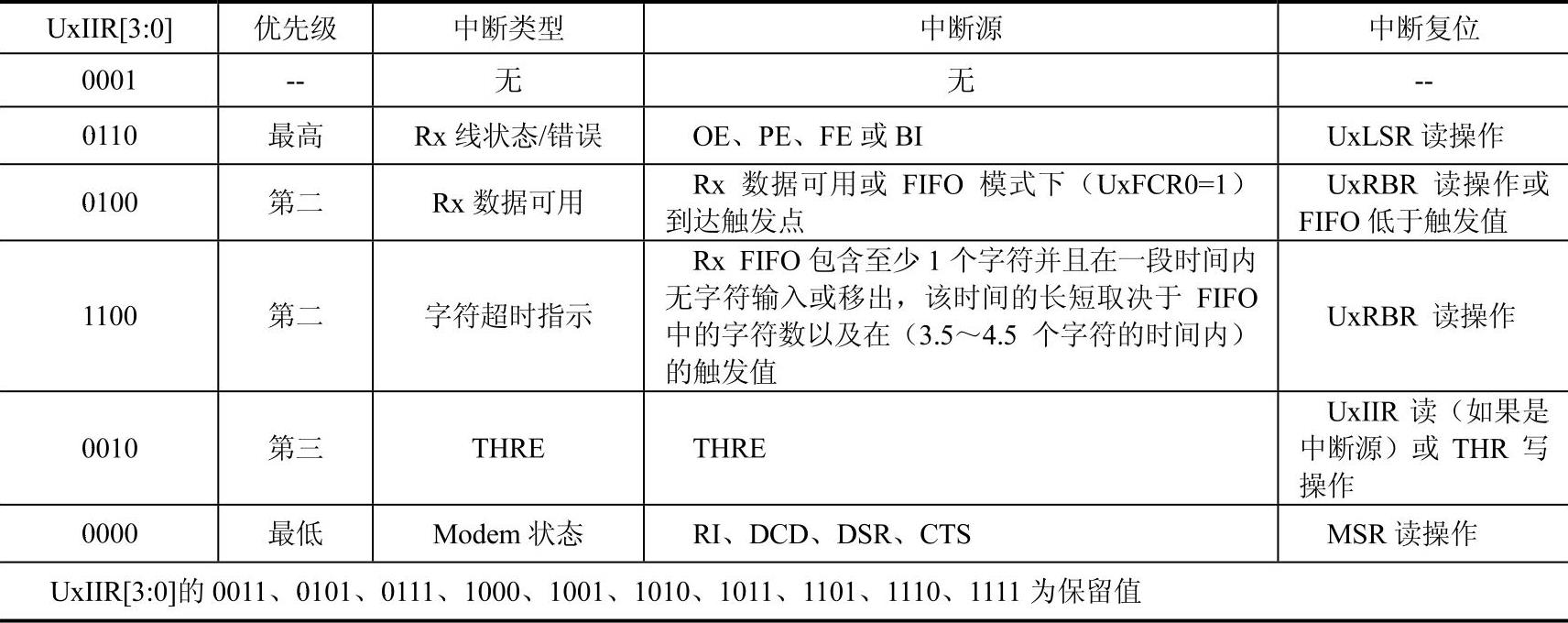

中断的处理如表4-11所列。只要给定了UxIIR[3:0]的状态,中断处理程序就能确定中断源以及如何清除激活的中断。在退出中断服务程序之前,必须读取UxIIR来清除中断。

RLS中断(UxIIR[3:1]=011)是最高优先级的中断。只要Rx输入产生4个错误条件(溢出错误(OE)、奇偶错误(PE)、帧错误(FE)和间隔中断(BI))中的任意一个,该中断标志将置位。产生该中断的Rx错误条件可通过查看UxLSR[4:1]得到,当读取UxLSR时清除中断。(https://www.daowen.com)

RDA中断(UxIIR[3:1]=010)与CTI中断(UxIIR[3:1]=110)共用第二优先级。当Rx FIFO到达UxFCR[7:6]所定义的触发点时,RDA被激活;当Rx FIFO的深度低于触发点时,RDA复位;当RDA中断激活时,CPU可读出由触发点所定义的数据块。

CTI中断(UxIIR[3:1]=110)为第二优先级中断。当Rx FIFO包含至少1个字符并且在接收3.5到4.5个字符的时间内没有发生Rx FIFO动作时,产生该中断。Rx FIFO的任何动作(读或写RSR)都将清除该中断。当接收到的信息不是触发值的倍数时,CTI中断将会清空RBR。例如,如果一个外设想要发送一个105个字符的信息,而触发值为10个字符,那么前100个字符将使CPU接收10个RDA中断,而剩下的5个字符使CPU接收1~5个CTI中断(取决于服务程序)。

THRE中断(UxIIR[3:1[=001]为第三优先级中断。当THR FIFO为空并且满足特定的初始化条件时,该中断被激活。这些初始化条件将使THR FIFO被数据填充,以免在系统启动时产生许多THRE中断。初始化条件在THRE=1时,实现了一个字符的延时减去停止位,并在上一次THRE=1事件之后,没有在UxTHR中存在至少2个字符。在没有译码和服务THRE中断时,该延迟为CPU提供了将数据写入UxTHR的时间。如果THR FIFO中曾经有两个或更多字符,而当前UxTHR为空时,THRE中断立即设置。当发生UxTHR写操作或UxIIR读操作,并且THRE为最高优先级中断(UxIIR[3:1]=001)时,THRE中断复位。

Modem中断(U1IIR)[3:1]=000)仅用于UART1,它是最低优先级中断。只要在Modem输入引脚RI、DCD、DSR或CTS上发生任何状态变化,该中断就会被激活。此外,Modem输入口线RI上低到高电平的跳变也会产生一个Modem中断。Modem中断源可通过检查U1MSR[3:0]得到。读取U1MSR将清除Modem中断。

表4-11 中断的处理

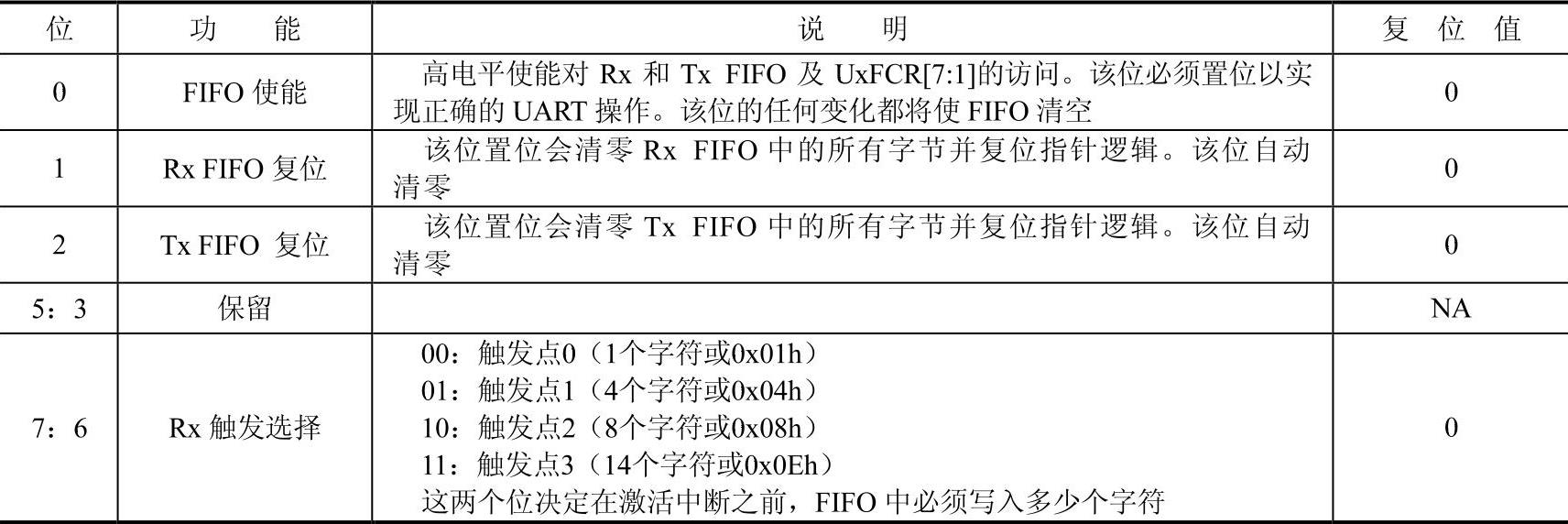

7.UART FIFO控制寄存器UxFCR

UxFCR寄存器控制UART Rx和UART Tx FIFO的操作,其功能如表4-12所列。

表4-12 UxFCR寄存器功能

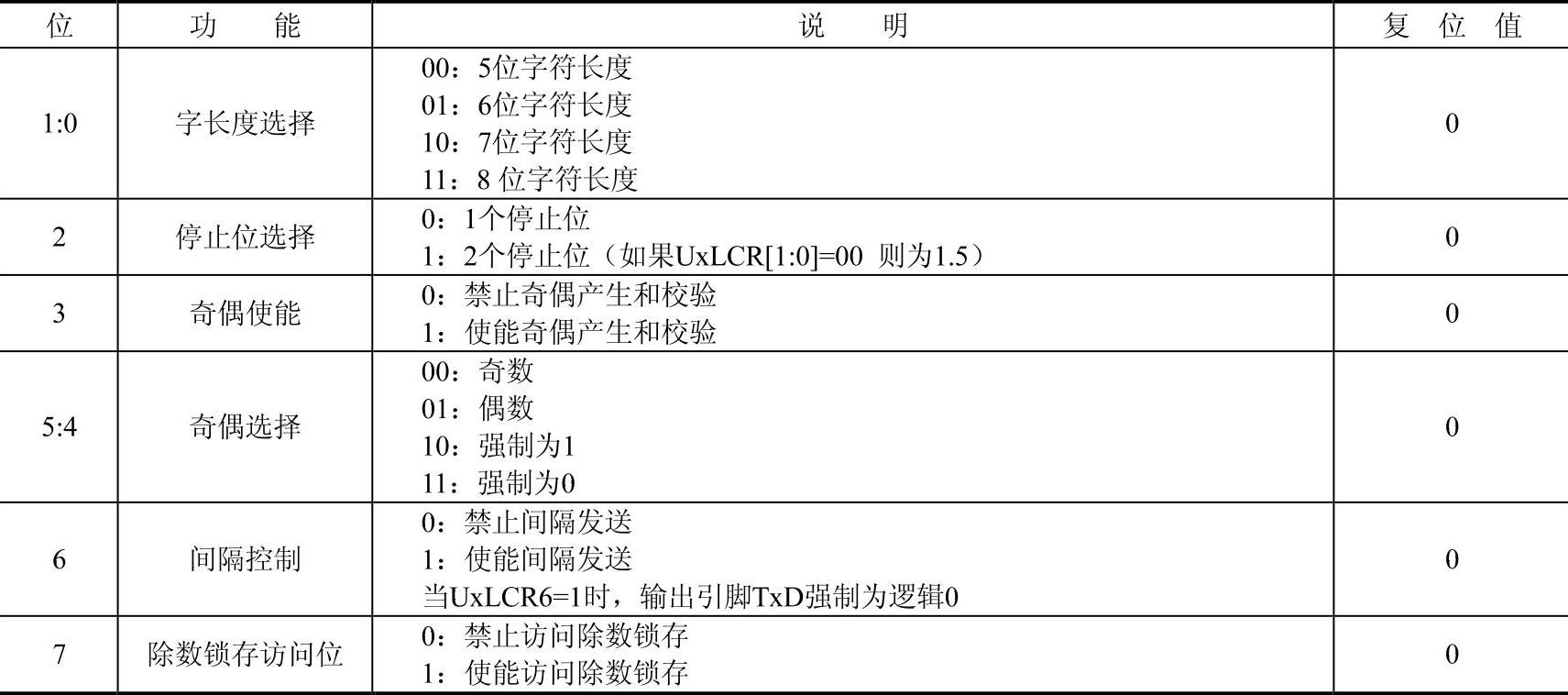

8.UART线控制寄存器UxLCR

UxLCR寄存器决定发送和接收数据字符的格式,其功能如表4-13所列。

表4-13 UxLCR寄存器功能

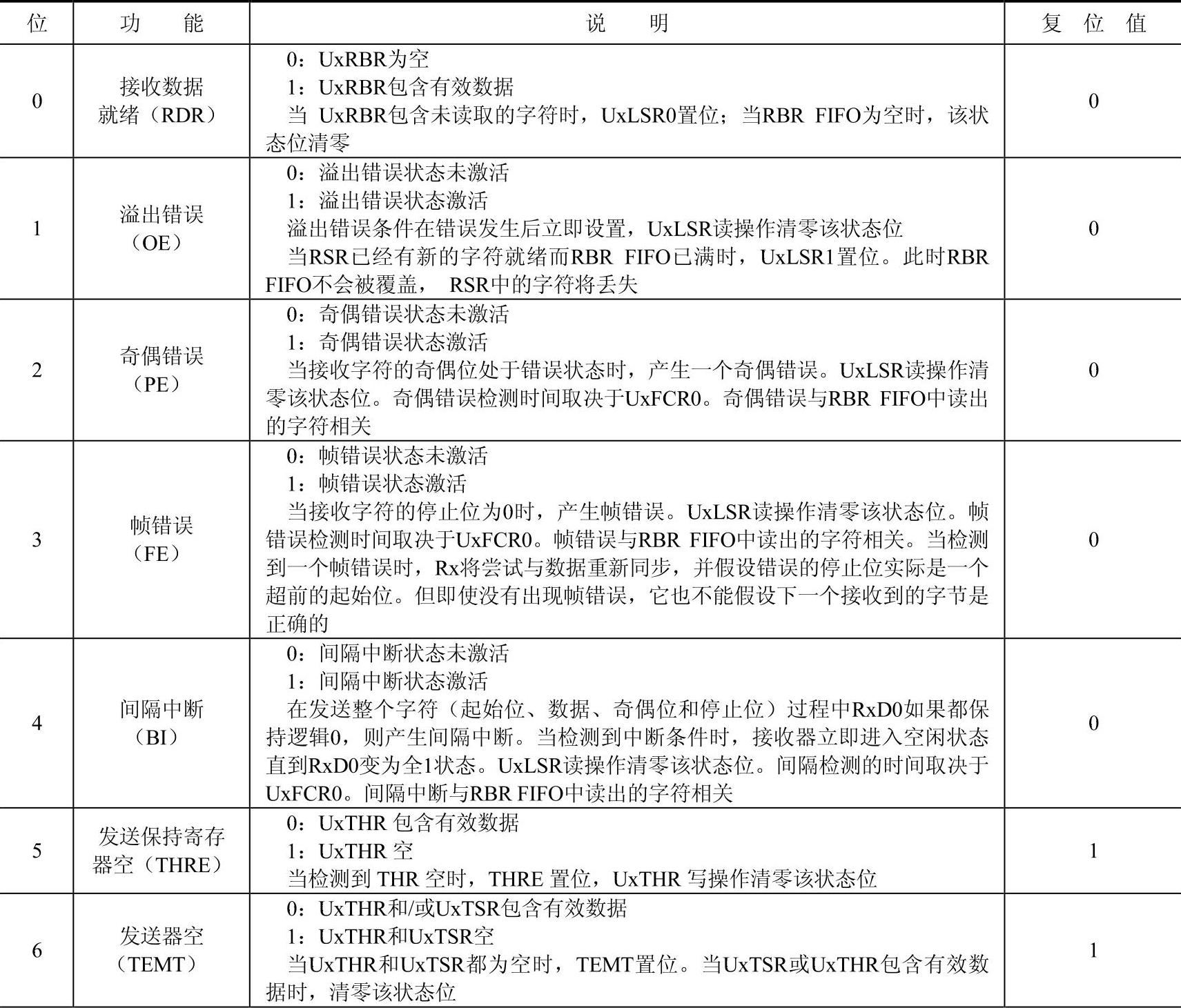

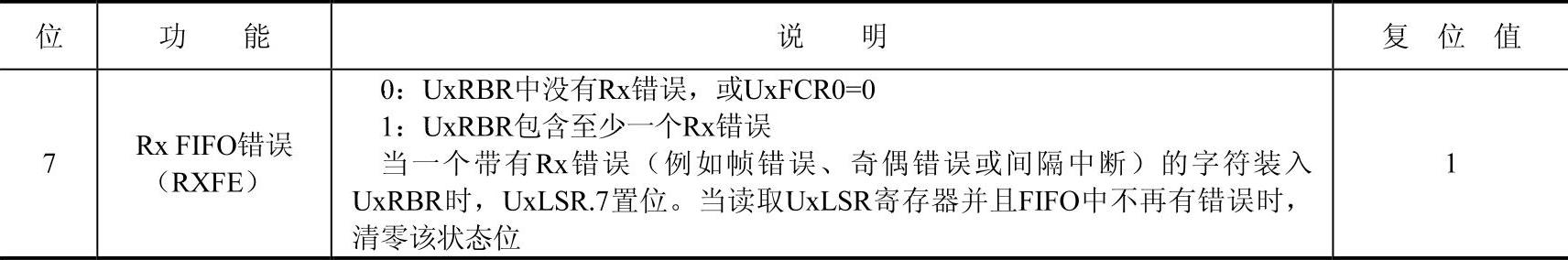

9.UART线状态寄存器UxLSR

UxLSR为只读寄存器,它提供Tx和Rx模块的状态信息,其功能如表4-14所列。

表4-14 UxLSR寄存器功能

(续)

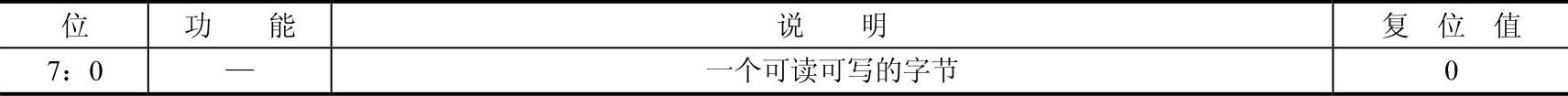

10.UART高速缓存寄存器UxSCR

在UART操作时UxSCR无效。用户可对该寄存器进行读/写。不提供中断接口向主机指示UxSCR所发生的读/写操作。UxSCR寄存器功能如表4-15所列。

表4-15 UxSCR寄存器功能

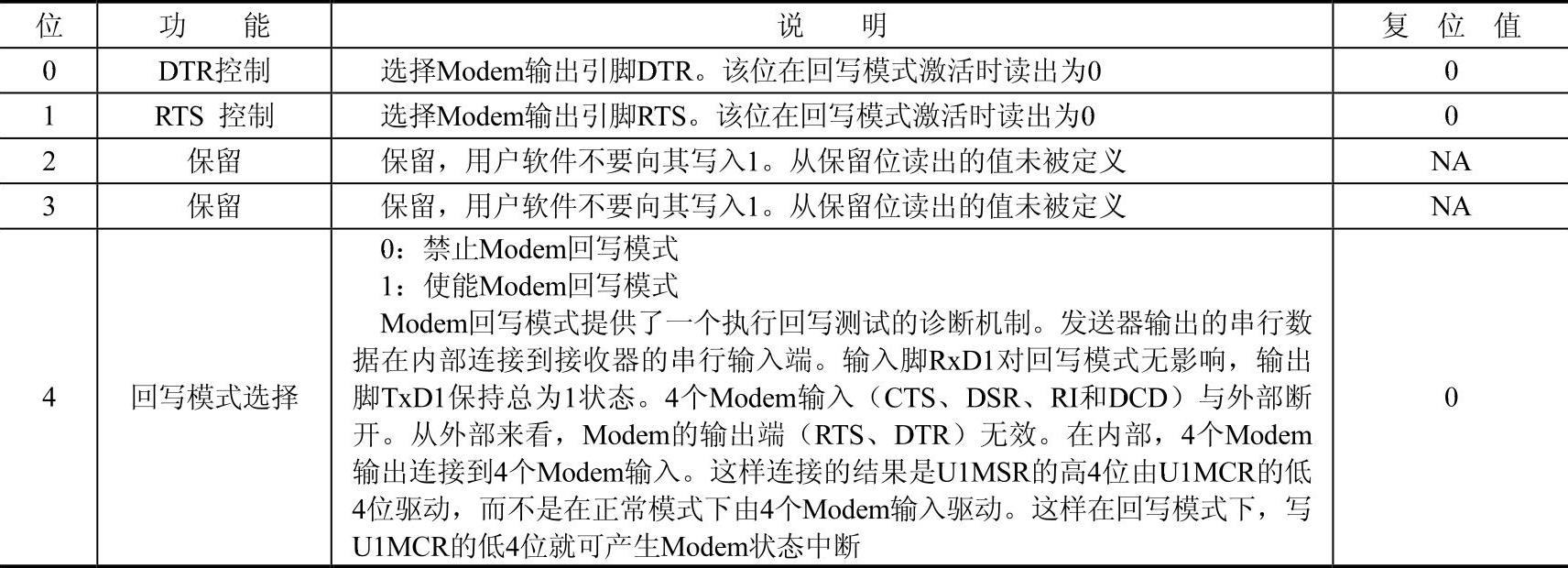

11.UART1 Modem控制寄存器U1MCR

U1MCR使能Modem的回写模式并控制Modem的输出信号,其功能如表4-16所列。

表4-16 U1MCR寄存器功能

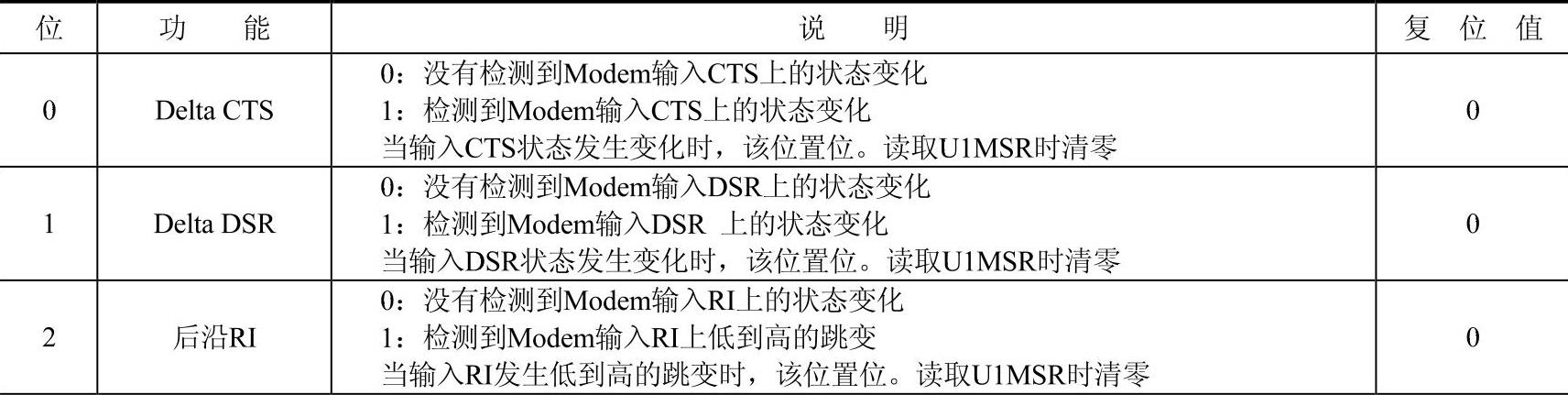

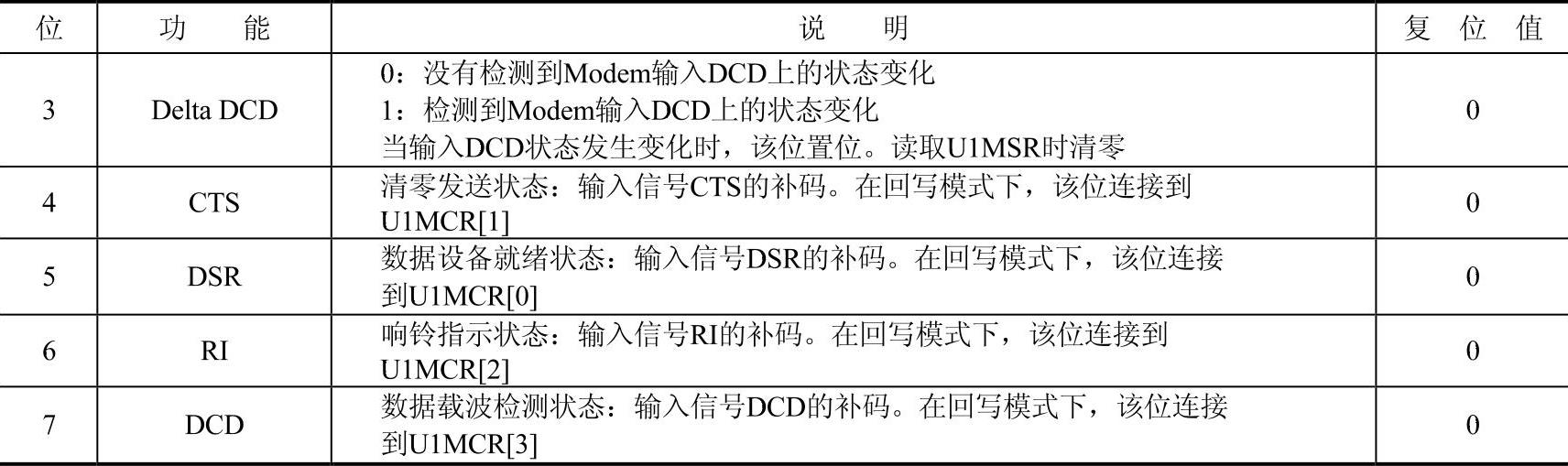

12.UART1 Modem状态寄存器U1MSR

U1MSR提供Modem输入信号的状态信息,U1MSR[3:0]在读取U1MSR时清零。需要注意的是,Modem信号对UART1的操作没有直接影响,Modem信号的操作是通过软件来实现的。

U1MSR是一个只读寄存器,其功能如表4-17所列。

表4-17 U1MSR寄存器功能

(续)

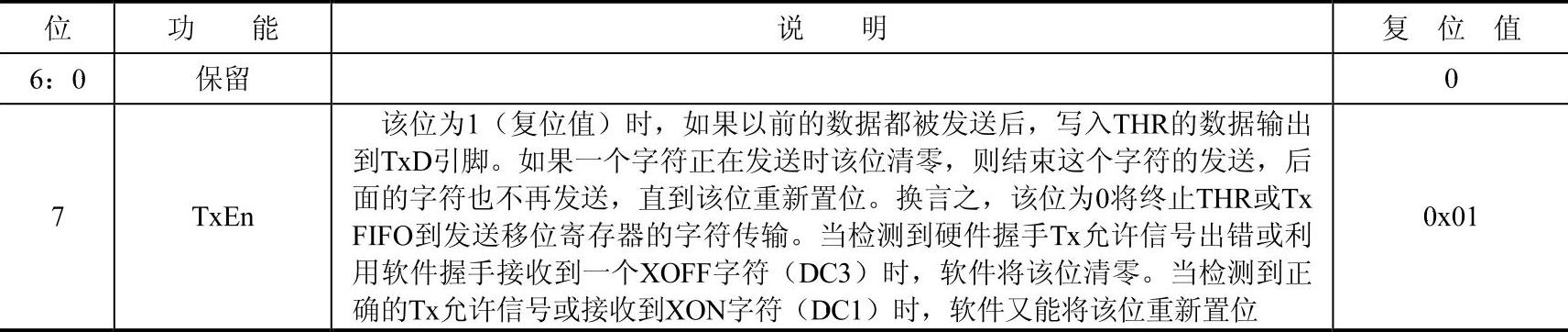

13.UART1发送使能寄存器U1MSR

UART1使能实现软件和硬件流控制,由U1TER控制。当TxEn=1时,只要数据可用,UART1发送器就将持续发送数据。一旦TxEn变为0,UART1发送器立刻停止工作。

U1TER寄存器功能如表4-18所列。

表4-18 U1TER寄存器功能

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。