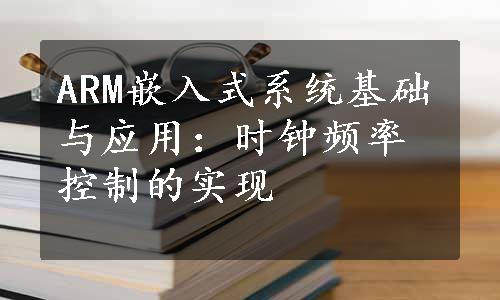

LPC2138处理器内部振荡电路支持频率为1~50MHz的时钟信号,如果使用了片内锁相环PLL或引导装载程序,输入时钟频率将被限制到10~25MHz。LPC2138对时钟频率Fosc的选择如图3-5所示。

图3-5 LPC2138对时钟频率Fosc的选择

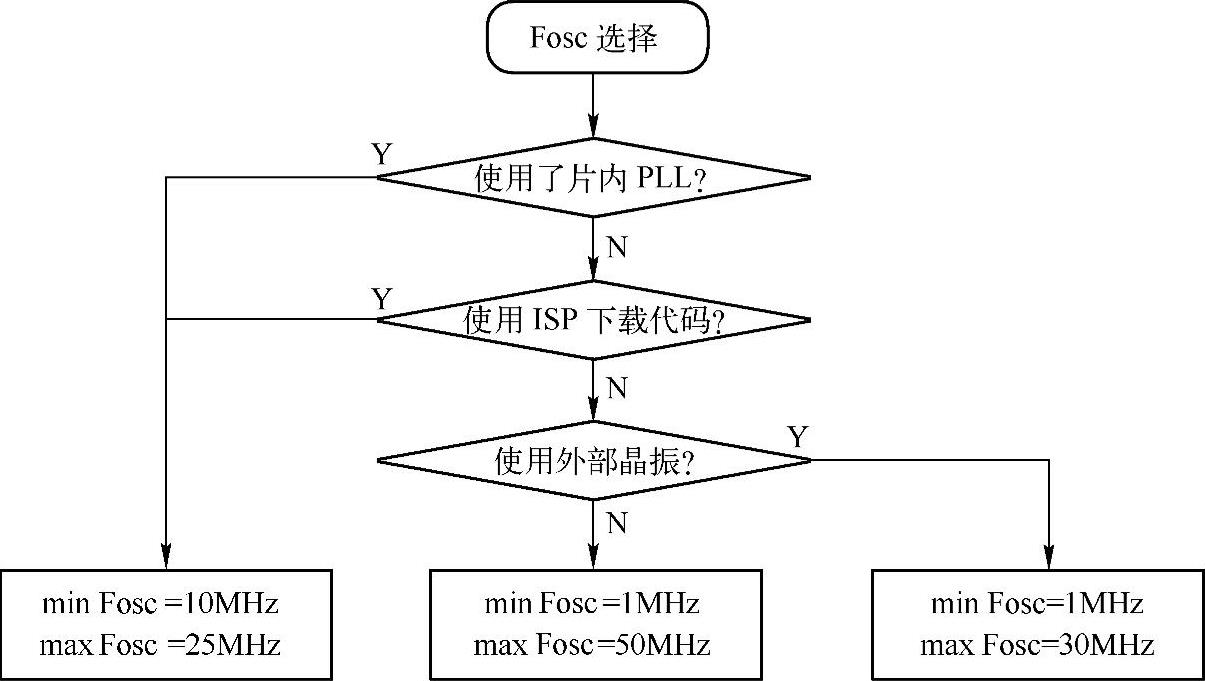

LPC2138的振荡器可以工作于两种模式:从属模式和振荡模式。

从属模式如图3-6a所示,时钟信号与一个100pF的电容Cc相连后从XTAL1端输入,其幅值不低于200mV,XTAL2端不连接。从属模式下,要求时钟信号的占空比为50%,频率限制在1~50MHz。

振荡模式如图3-6b所示,由于片内集成了反馈电阻,只需在XTAL1和XTAL2端之间连接一个外部晶振XTAL和电容Cx1、Cx2就可形成基本模式的振荡电路。振荡模式下,晶振频率限制在1~30MHz。

图3-6 振荡器工作模式

a)从属模式 b)振荡模式

上述两种振荡器模式都可以用来驱动片内锁相环PLL,给CPU和片内外设提供时钟。锁相环PLL接受输入时钟频率范围为10kHz~25MHz,输入频率通过一个电流控制振荡器(CCO)倍增到范围10~60MHz,倍频系数可以是从1~32的整数(实际上,由于LPC2138CPU最高频率限制为60MHz,LPC2138的倍频系数不能高于6)。CCO的操作频率范围为156~320MHz,因此,锁相环中有一个额外的分频器,使得PLL在提供所需要的输出频率时,CCO依然保持在允许频率范围内。输出分频器可设置为2、4、8或16分频,最小分频值为2,保证PLL输出有50%的占空比。

PLL的激活由PLLCON寄存器控制,PLL倍频器和分频器的值由PLLCFG寄存器控制。为了防止PLL参数发生意外改变或PLL失效,对这两个寄存器进行了保护。由于芯片的所有操作(包括看门狗定时器)都依赖于PLL提供的时钟,因此,PLL设置的意外改变将导致CPU执行不期望的动作。对它们的保护是由一个类似于操作看门狗定时器的代码序列来实现的。

LPC2138处理器通过如下几个寄存器来实现锁相环PLL控制。

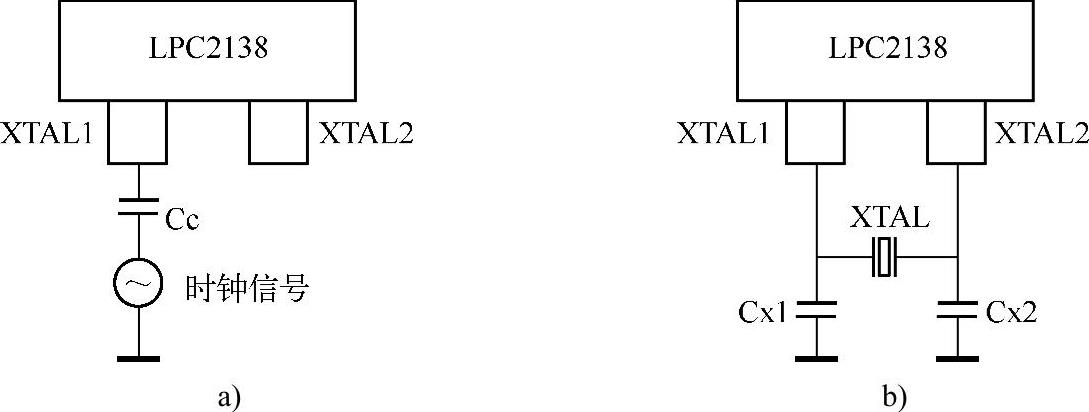

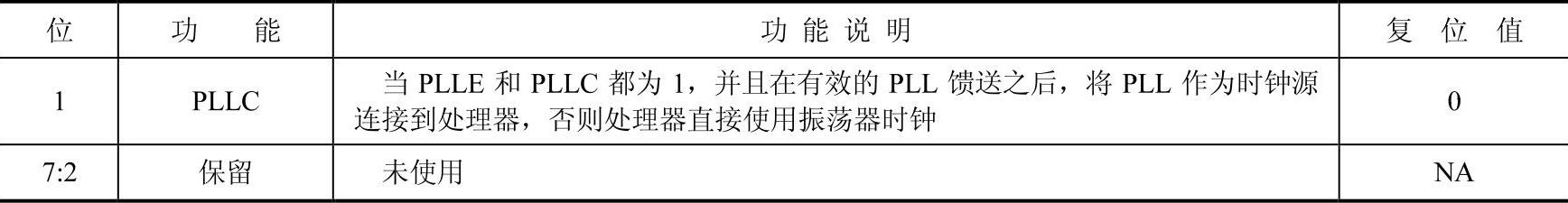

1.PLL控制寄存器PLLCON

PLLCON寄存器用于PLL的激活和连接。激活PLL,将使PLL锁定到由当前倍频器和分频器的值设定的频率上。连接PLL,将使处理器和所有片内功能都根据PLL的输出时钟频率运行。写入PLLCON寄存器的值只有在对PLL馈送寄存器PLLFEED执行了正确的PLL馈送序列之后才会生效。PLLCON寄存器的功能如表3-6所列。

表3-6 PLLCON寄存器功能

(续)

PLL在作为时钟源之前必须进行设置、激活并锁定,PLL在芯片复位和进入掉电模式时被关闭并旁路,PLL只能通过软件激活,程序必须在配置并激活PLL后等待其锁定,然后再连接PLL。将振荡器时钟切换到PLL输出或反过来操作时,内部电路对操作进行同步以确保不会产生干扰。硬件不能确保PLL在连接之前锁定或在PLL失去锁定时自动断开连接。在PLL失去锁定的情况下,振荡器很可能已经变得不稳定,这样断开PLL也挽救不了这种状况。

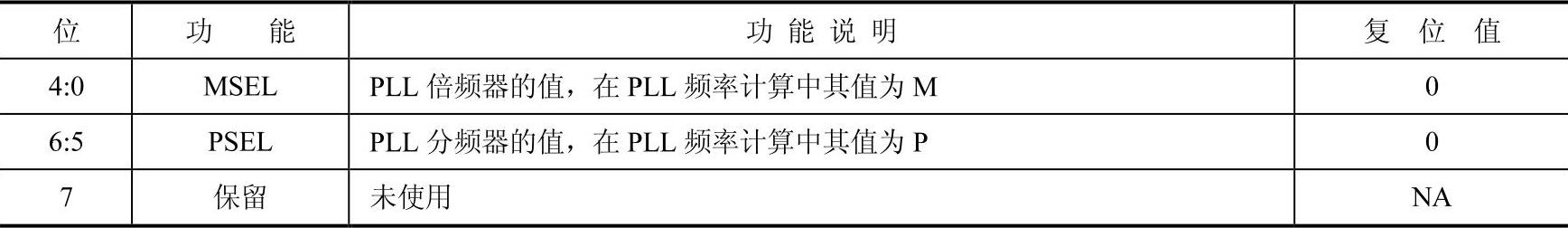

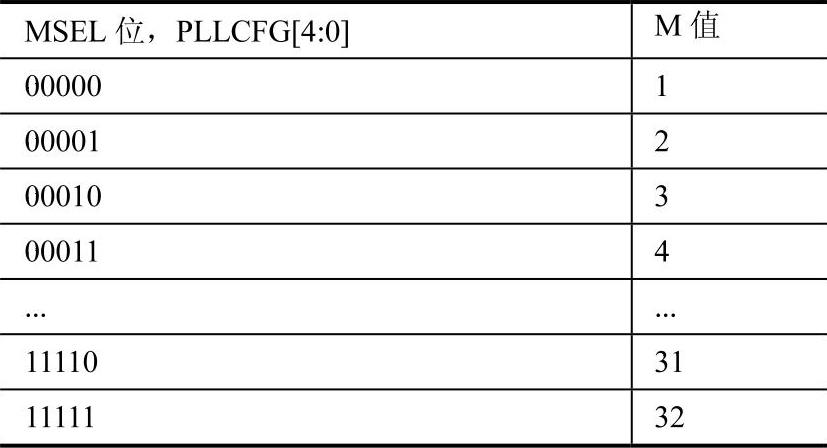

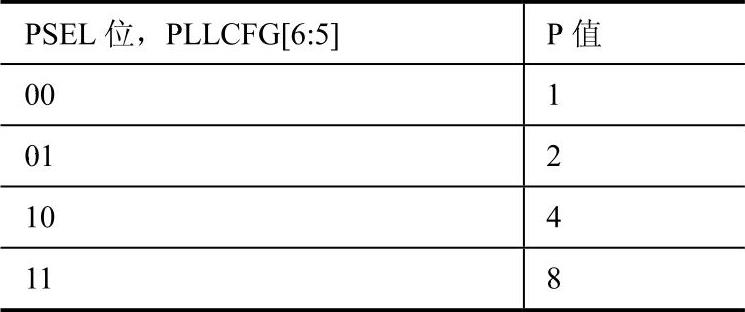

2.PLL配置寄存器PLLCFG

PLLCFG寄存器用于控制倍频器和预分频器的值(分别用字母M和P表示),在执行正确的PLL馈送序列之前,写入PLLCFG寄存器的值不会生效。PLLCFG寄存器的功能如表3-7所列。

表3-7 PLL配置寄存器功能

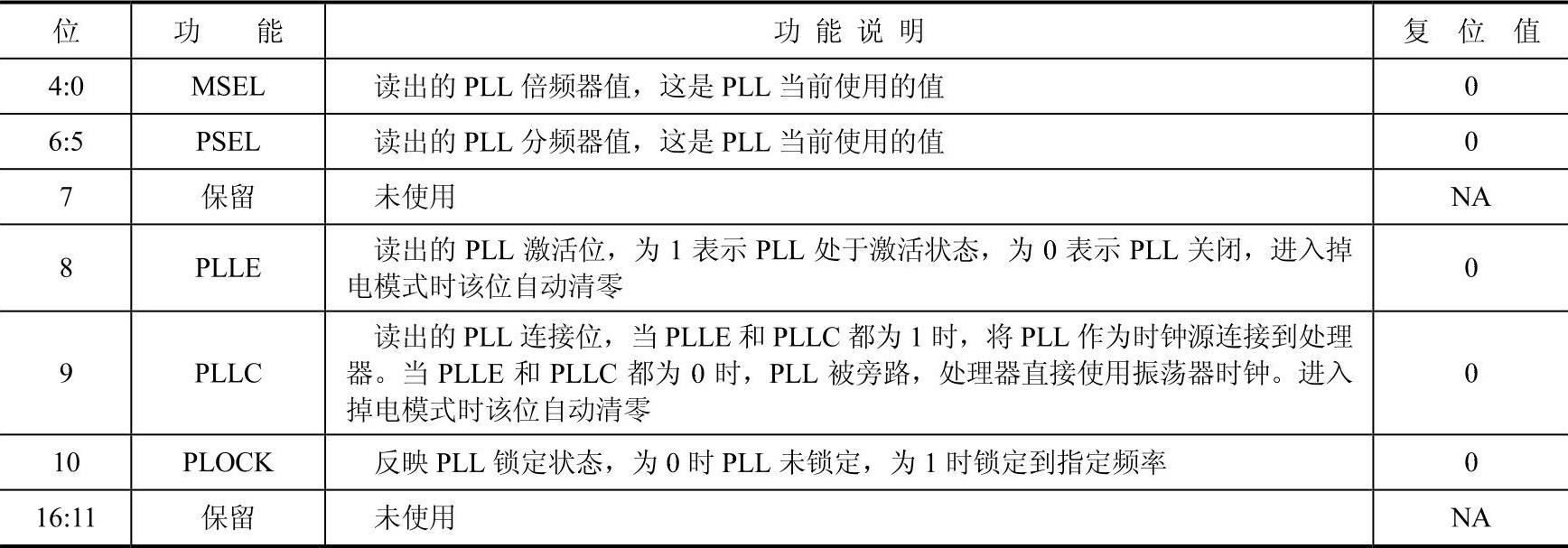

3.PLL状态寄存器PLLSTAT

PLLSTAT寄存器为只读寄存器,用于读回当前正在使用的PLL参数和状态。PLLSTAT寄存器的值可能与PLLCON和PLLCFG的值不同,这是因为在没有执行正确的PLL馈送序列之前,PLLCON和PLLCFG寄存器中的值无效。PLLSTAT寄存器的功能如表3-8所列。

表3-8 PLL状态寄存器功能

PLLSTAT寄存器中的PLOCK位连接到中断控制器,这样可以使用软件打开PLL并连接到其他功能,不需要等待PLL锁定。发生中断时(PLOCK=1)可以连接PLL并禁止中断。

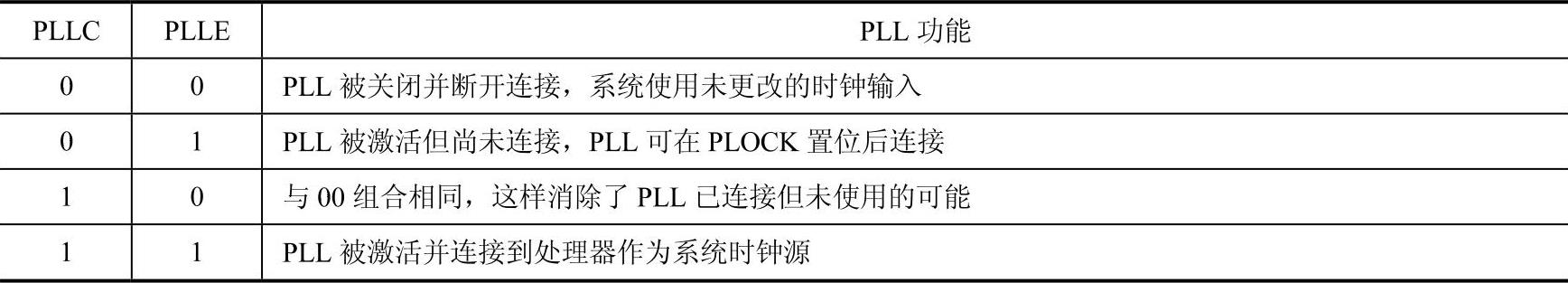

PLL有3种工作模式,由PLLC和PLLE位的组合控制,如表3-9所列。

表3-9 PLL的工作模式

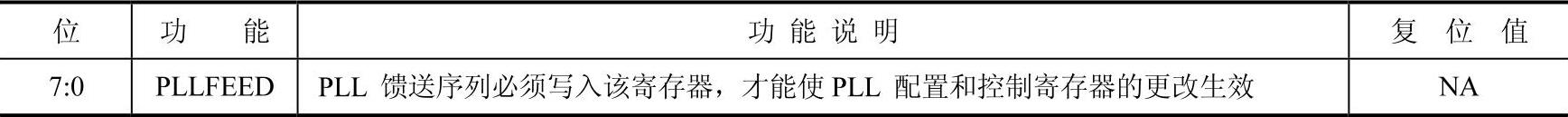

4.PLL馈送寄存器PLLFEED

必须将正确的馈送序列写入PLL馈送寄存器PLLFEED,才能使PLLCON和PLLCFG寄存器的更改生效。馈送序列是将数值0xAA和0x55依次写入PLLFEED寄存器,写入顺序必须正确,并且必须在写入期间禁止中断。PLLFEED寄存器的功能如表3-10所列。

表3-10 PLLFEED寄存器功能(www.daowen.com)

如果用户程序要更改PLL设置,并且应用程序中开启了其他中断,则在重设PLL时(其实应该是发送PLL馈送序列时),需按照如下步骤进行:

●关中断。

●发送PLL馈送序列。

●开中断。

LPC2138处理器在掉电模式下会自动关闭并断开PLL,从掉电模式唤醒不会自动恢复PLL的设定,必须由软件予以恢复。不要试图在掉电唤醒之后简单地执行馈送序列来重新启动PLL,这将导致出现在PLL锁定之前同时激活并连接PLL的危险。

PLL输出频率的计算会用到如下参数:

Fosc 晶振频率

Fcco PLL电流控制振荡器的频率

Fcclk PLL输出频率(也是处理器的时钟频率)

M PLLCFG寄存器中MSEL位的倍频值

P PLLCFG寄存器中PSEL位的分频值

PLL输出频率(当PLL激活并连接时)计算公式如下:

Fcclk=M×Fosc 或 Fcclk=Fcco/(2×P)

CCO频率计算公式如下:

Fcco=Fcclk×2×P 或 Fcco=Fosc×M×2×P

PLL的输入和设定必须满足下面条件:

●Fosc的范围为10~25MHz。

●Fcclk的范围为10MHz~Fmax(LPC2138的最大允许频率)。

●Fcco的范围为156~320MHz。

PLL的配置过程如下:

1)选择处理器工作频率Fcclk。这可以根据处理器的整体要求、UART波特率等因素来决定。外围器件的工作频率可以低于处理器频率器。

2)选择振荡器频率Fosc。注意,Fcclk必须是Fosc的整数倍。

3)计算M值以配置MSEL位。M=Fcclk/Fosc,M取值范围为1~32。写入MSEL位的值为M-1,如表3-11所列。

4)选择P值以配置PSEL位,使Fcco在定义的频率限制范围内,Fcco可通过前面介绍的公式计算。P值必须是1、2、4、或8中的一个。写入PSEL位的值所对应的P值如表3-12所列。

表3-11 PLL的倍频值

表3-12 PLL的分频值

下面举一个PLL配置实例。

假如系统要求Fosc=10MHz,Fcclk=60MHz,PLL配置如下:

M=Fcclk/Fosc=60MHz/10MHz=6,因此将M-1=5写入PLLCFG[4:0]。

P=Fcco/(Fcclk×2),Fcco必须在156~320MHz之内。Fcco取最低频率156MHz,则P=156MHz/(2×60MHz)=1.3,Fcco取最高频率可得出P=2.67。为了同时满足Fcco最低和最高频率要求,P值只能为2。因此,应写入PLLCFG[6:5]=01。最终得到PLLCFG的值为0x25。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。