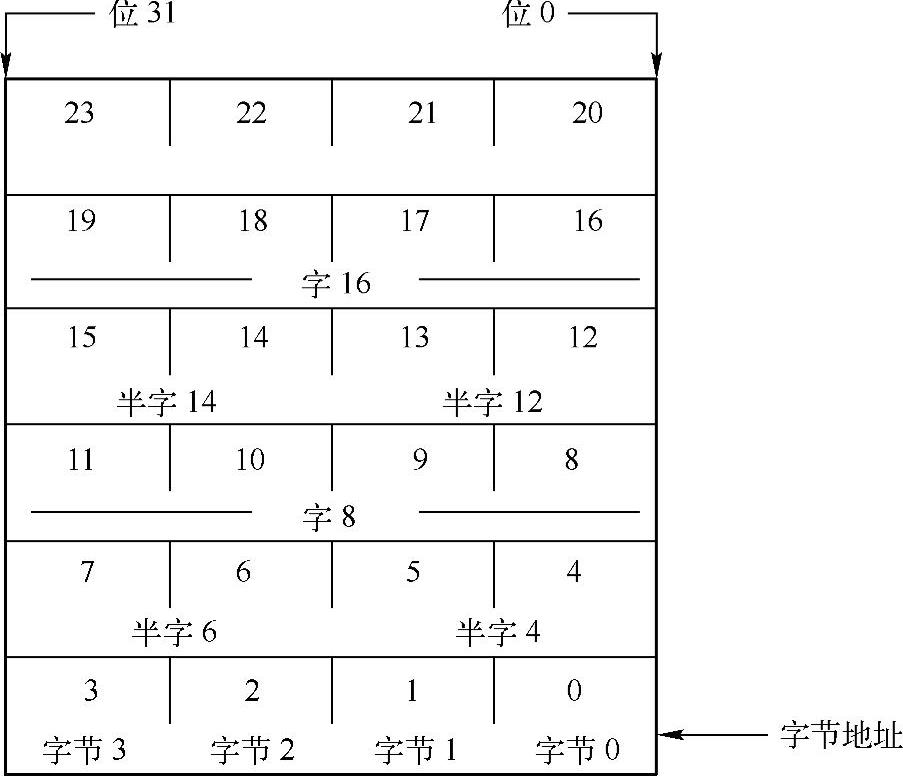

ARM体系结构支持三种数据类型:字(Word),长度为32位;半字(Halfword),长度为16位;字节(Byte),长度为8位。

在ARM存储器组织中,半字必须与2字节边界对齐,字必须与4字节边界对齐,即半字必须开始于偶数地址,字必须开始于4的倍数的字节地址,如图1-1所示。

图1-1 ARM数据类型存储图

ARM处理器采用冯·诺依曼(Von Neumann)形式的存储器结构,使用232个字节的单一、线性地址空间。从0字节开始到第3字节存放第一个字数据,从第4字节到第7字节存放第二个字数据,依次类推。指令和数据共用一条32位数据总线,只有加载、保存和交换指令可以访问存储器中的数据。作为32位的微处理器,ARM体系结构所支持的最大地址空间为4GB(232B)。

ARM7处理器采用3级指令流水线,在执行当前指令的同时对下一条指令进行译码,并对再下一条指令进行指令预取,如果预取操作溢出了地址空间顶端,则不会产生执行动作,并导致不可预知的结果。

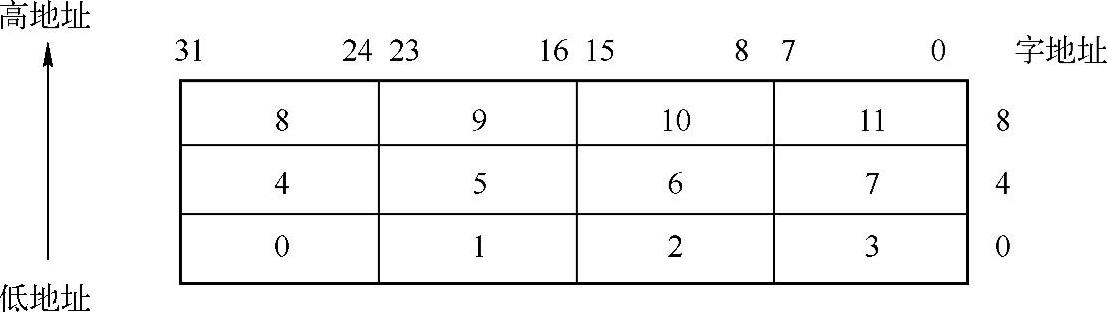

ARM体系结构可以用两种方法存储字数据,分别称为大端格式(Big Endian)和小端格式(Little Endian)。在大端格式中,字数据的高字节存储在低地址中,而字数据的低字节则存放在高地址中,如图1-2所示。

(https://www.daowen.com)

(https://www.daowen.com)

图1-2 大端存储格式

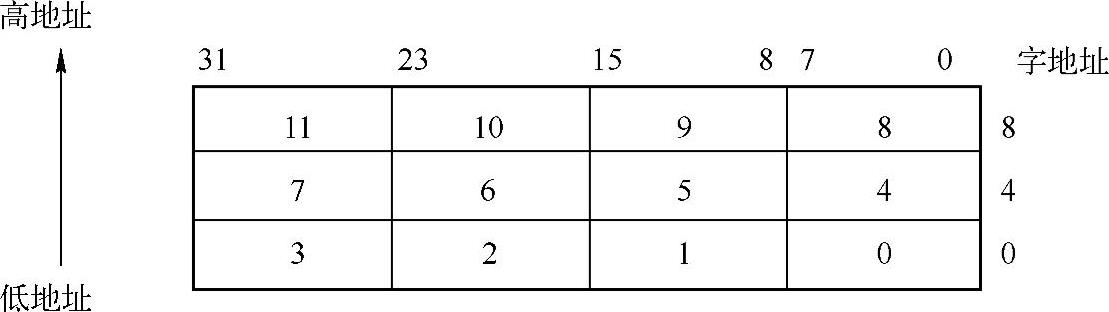

与大端存储格式相反,在小端存储格式中,低地址中存放的是字数据的低字节,高地址存放的是字数据的高字节,如图1-3所示。

图1-3 小端存储格式

多数厂家生产的ARM核处理器芯片,都能够支持大端和小端两种存储格式,默认为小端存储格式。如果一个基于ARM核的处理器芯片将存储器系统配置为其中一种格式(如小端),而实际连接的存储器系统配置为相反的格式(如大端),那么只有以字为单位的指令取指、数据加载和数据保存能够可靠地实现,其他的存储器访问将出现不可预知的结果。

ARM体系结构通常希望所有的存储器访问能适当地对齐。特别是用于字访问的地址通常应当字对齐,用于半字访问的地址通常应当半字对齐。未按这种方式对齐的存储器访问称为非对齐的存储器访问。

ARM体系结构完成I/O功能的标准方法是使用存储器映射I/O。这种方法采用特定的存储器地址,当从这些地址加载或向这些地址存储时,它们提供I/O功能。典型情况下,从存储器映射I/O地址加载用于输入,而向存储器地址I/O存储则用于输出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。