到目前为止,只考虑了阈值电压作为主参数决定直流输出电压的情况。但是,在实际中其他参数对它也会有一定影响,如二极管模型、耦合和控制电容器的参数。

为了解决上述问题,首先,需要知道什么是非理想性以及对于整流器的每个元素寄生效应出现在哪。

1.有源元件的寄生效应

2003年,Karthaus和Fischer首先声明[KAR 03],对于作为转换器的电荷转移器件,设计者可以在肖特基二极管和金属氧化物半导体场效应晶体管(MOSFET)之间做出选择。对于后者,出现了许多解决方法,例如本地的晶体管的使用、特殊的偏置电路,通过模拟内存或者动态门限MOSFET的阈值编程[TEH 09]。

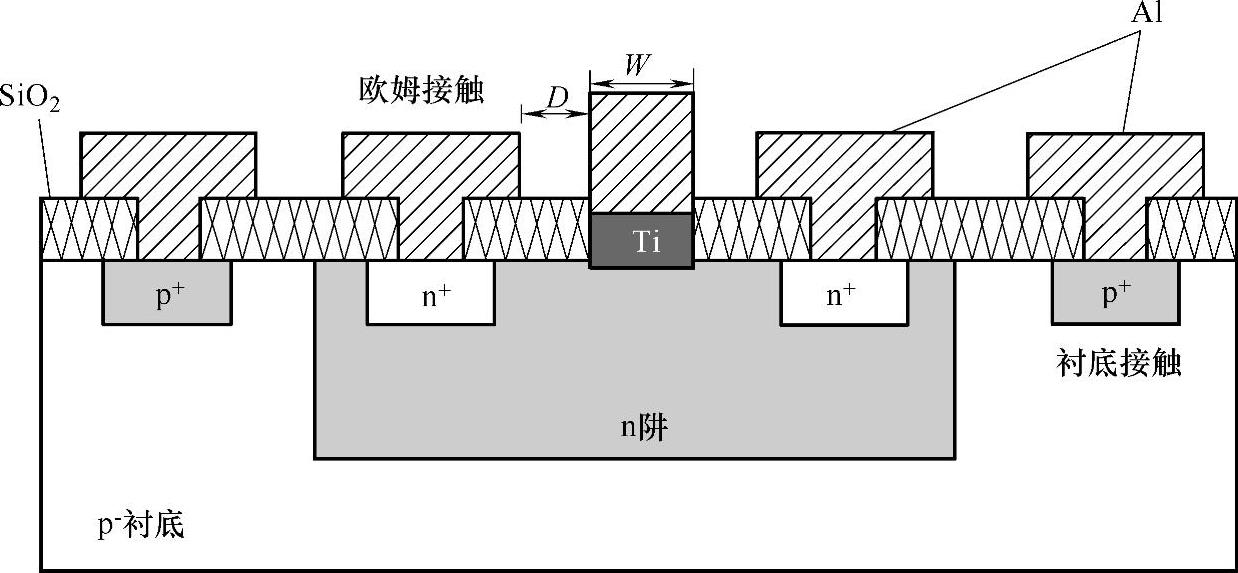

在设计一个用于UHF RFID系统的肖特基二极管时,数值、相关的非线性和二极管的RC截止频率都是需要考虑的。并且,二极管的寄生效应由几何尺寸和物理工序决定。在一个标准的CMOS工序上必须使用一个具有通用掩膜的简单集成的方式来实现二极管。图1.6所示是一个典型的平面二极管[JAM06b],图1.7显示了和它相关的电动模型。它包括一个连接n阱活跃区域的肖特基接触和一个连接掺杂n+膜的欧姆接触。这个结构允许使用紧凑的布局以便于最小化外部参数和电容的数量。

图1.6 平面肖特基栅栏二极管的横截面

图1.7 平面肖特基栅栏二极管的横截面的电动模型

当选择肖特基二极管时,使其具有较大的饱和电流IS是很重要的,因为那将使得正向电压降较低,同样也会使得基层Csub的结电容和寄生效应都比较小。然而,较大的肖特基二极管虽然具有较大的饱和电流,但同时也会带来较大的电容,而电容控制着功耗,所以需要对二极管采取最优选择。

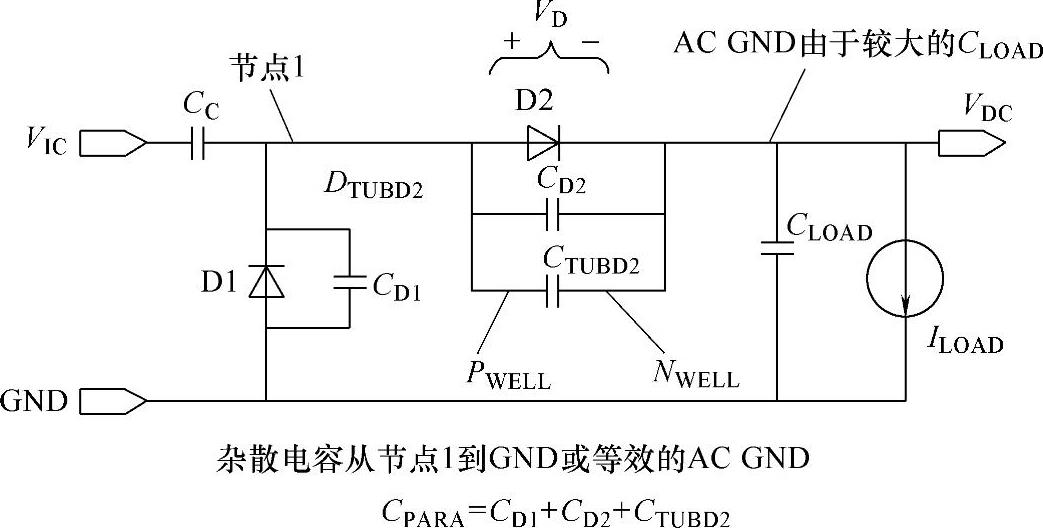

在图1.8中的节点1处,可以很清楚地知道这个基底电容类似于并联电容CPARA,它是结电容CD1和CD2、标有CTUBD2的串联二极管D2的电容加上互连的导线电容的总和。因此,CPARA一般要比CC小一个数量级。

图1.8 肖特基二极管的横截面和有寄生效应的双倍压器

二极管和耦合电容的串联电阻可以通过多指结构最小化,由于直流二极管电流很小,所以通常情况下串联的电阻Rs在UHF RFID中可以被忽略,这会导致小电阻的压降低于1mV。

使用肖特基势垒二极管(SBD)方案的主要限制是需要对CMOS工序进行专门的改进。许多实验室都在寻找如何最优化的MOSFET方法。随着晶体管的尺寸越来越小,有效的阈值电压越来越接近SBD开启电压[THE 09],大约为150~200mV。

与SBD不同的是,MOS管在一次传导过程中工作在不同区域。当它处于开启状态时,大多数时间它处在超阈值区域,在这个区域中,基极电流与栅极电压成比例。当它处于关闭状态时,它会传导反向漏电流(基极和源极的倒置)。当栅极与源极相连时,电流低于阈值并且不能被忽略。因为[YI 07]:

(1)它随着阈值电压的降低会具有指数级的增加;

(2)电流具有相同的数量级(μA);

(3)功耗不能被忽略,因为它会持续半个周期。

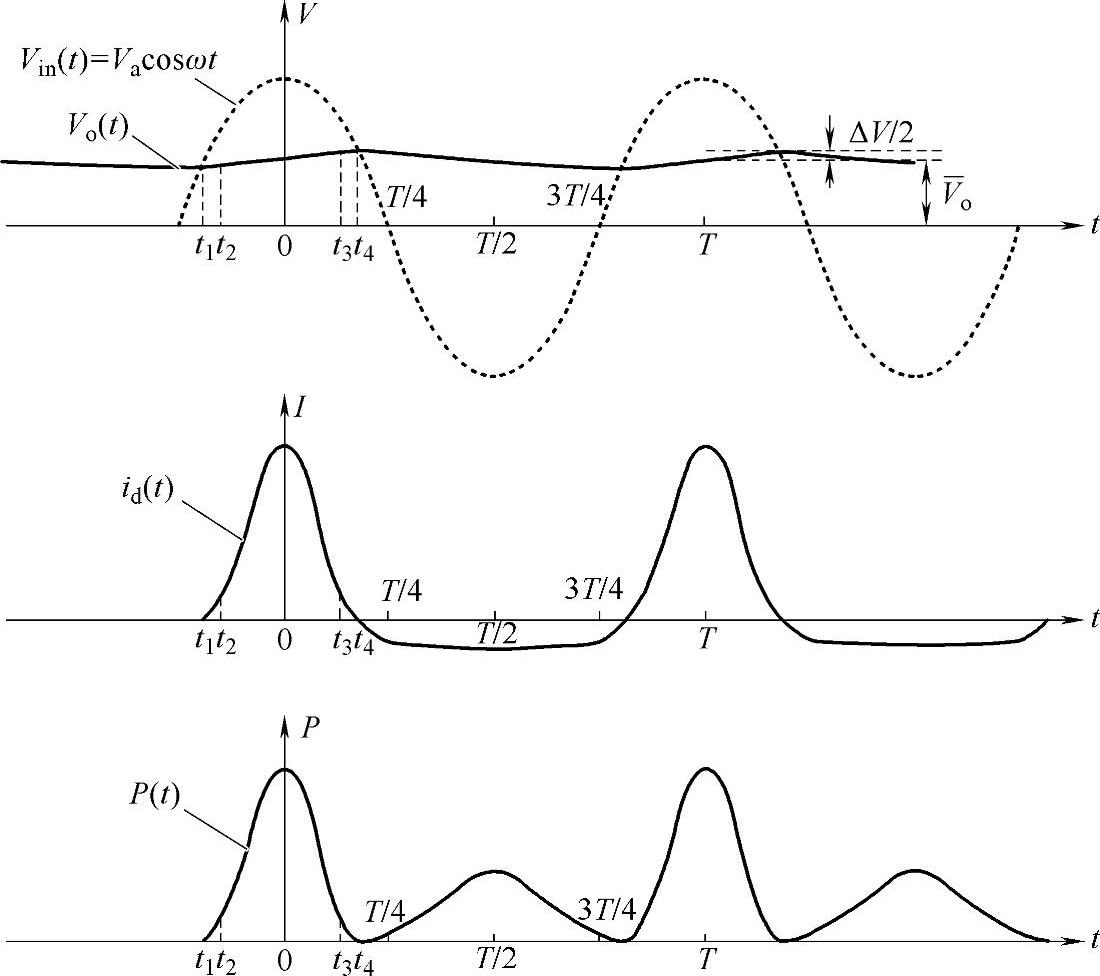

在图1.9中进行了说明,反向电流导致功率消耗。

2.无源元件的寄生效应

同样地,由于在充电时耦合电容器基底的漏电容也会导致寄生效应。因此,也应该被最小化。

事实上,附加的平行电容器对地面的影响很大,我们将在后面的匹配问题上讨论它的影响。现在,就像图1.8所示的那样,它们仍然作为分压器,因此在转换公式中,不仅要考虑输入电压,还要考虑在节点1处的修正电压。

图1.9 输入和输出电压、电流和功耗的波形

如果考虑的电容模型如图1.10所示[MAN 07],首先应该假设输入信号和耦合电容器CC的顶层相连。在这个模型中,焊盘和封装电容在整流电路的尺寸上相互独立,并且被划分到Cpak。整流器的输入电容是CPARA,并且由于二极管和晶体管的原因需要在每一级的输入中考虑与地面之间的寄生电容。在CC的底部金属板和地面之间的电容为CCP。(www.daowen.com)

这个模型推导出的式(1.10)清楚地显示了分压器的影响依赖于CPARA、CC和CCP的值。

图1.10 在理想的整流器前的电容的寄生电路模型

3.输出电压寄生效应的影响

式(1.10)表明降低电容CPARA是非常重要的。更重要的是,所有的输入电容表明,全部的阶段都是平行的。这种并行的后果是,RF电压适用于一个极低的阻抗,因此可以预期标准输入输出电压振幅下电压倍增器的最佳阶数。

图1.11表明,CPARA二极管的结电容的巨大影响可以解释最小化二极管的尺寸的重要性,无论采用肖特基二极管还是在二极管连接的MOS管。

图1.11 当CC=5pF时二极管结电容对输出电压的影响

4.中间电容器的尺寸

这些电容器作为电荷转移设备。当在输入信号负周期期间电容器进行充电,当输入信号正向时,释放电荷。因而,一个很小的值将会缩短电荷流向下一级的时间。另一方面,一个很大的值将会增加时间常数RC的值。同时,电压倍增器作为低通滤波器可以减缓标签和阅读器之间的数据交换。为了避免中间的功放产生分压,中间电容器必须合理选择使得它们满足CC≥10CD,其值通常约2~3pF。从式(1.10)可知,在这种情况下,电压损失不超过CCP/CC。

由于看到了DC的输出功率依赖于电压倍增器上的电压,因此必须考虑在AC模式下的电路状况。在AC分析中显示,中间电容器(除了所有的输出电容器)应该表现为短路;所以,所有的二极管都平行输出。

因此,对于这些电容器,基底电容必须降低。最好的方式就是选择多触点顶部金属层配置或者利用顶部两个金属层的电容来建立它们[JAM 06a]。

5.输出电容器的容积

为了确保输出DC电压是持续的,这些输出或保持电容器C必须具有特定尺寸以便它的持续时间要比RF输入信号[DEV 05]时间长很多,并且保证即使当来自于天线的RF功率在时间Tlow内无法利用时也可以正常操作。如果认为整流器的大部分负载是由板上的时钟频率的数字部分Tck产生的,则Cout的最小允许值可由下面的公式给出[MAN 07]:

式中,Csw是电容总量,通过在Vdd和地面之间的数字负载来调节;α是Vdd衰减的百分比。

这个公式导出了当前电容值接近于50~150pF。

6.寄生对功率损耗的影响

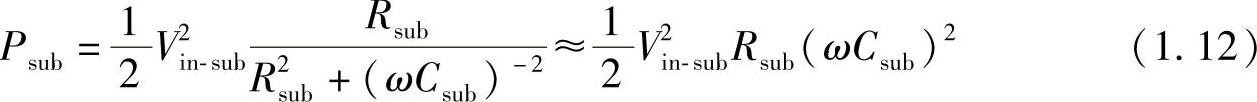

由于基底耦合产生的损耗都可以通过下式计算得到[KAR03]:

式中,Vin-sub是设备相对于基底的RF峰值电压;Csub是基底电容总量;Rsub是基底串联电阻值。

所做的假设是基于常见的低电阻率基底,此时RsubCsubω<<1。

在得出最终结论之前,必须先处理第二个约束,那就是匹配。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。