8051共有4个8位的并行I/O口,分别记作P0、P1、P2、P3。编址于特殊功能寄存器区域,既有字节地址又有位地址。每个口都包含一个锁存器、一个输出驱动器和输入缓冲器,均可进行字节输入/输出操作,每一条口线也可做位输入/输出操作。各口结构有差异,功能与用途各有异同,但每个口的位结构是相同的,故I/O的结构和原理就以位结构来说明。

一、并行I/O的结构与工作原理

1.P0口

(1)结构。

P0口的位结构如图2.11所示。由一个数据输出锁存器、两个三态数据输入缓冲器、一个数据输出的驱动电路和一个输出控制电路组成。

(2)功能。

①控制信号为低电平,作I/O口使用。

当P0口作为输出口使用时,内部总线将数据送入锁存器,内部的写脉冲加在锁存器时钟端CP上,锁存数据到Q端。经过MUX,V2反相后正好是内部总线的数据,送到P0口引脚输出。但这时场效应管V1截止,使V2漏极开路,需外接上拉电阻。

图2.11 P0口的位结构

当P0口作为输入口使用时,有读引脚和读锁存器两种情况,其中读引脚,是把端口引脚上的数据从缓冲器通过内部总线读入。由接口结构知道,读引脚前要先向口写1;读锁存器是为了适应对I/O口进行“读-修改-写”操作语句的需要。例如下面的C51语句:

P0=P0&0xf0; //读取P0口的内容进行逻辑运算后再输出

②控制信号为高电平,作地址/数据总线使用。

在进行单片机系统扩展时,作为低8位地址和8位数据分时复用口。控制信号为高电平,打开与门,并使多路开关MUX处于内部地址/数据线与驱动场效应管栅极反相接通状态。此时,输出驱动电路由于两个FET处于反相,形成推拉式电路结构,使负载能力大为提高。输入数据时,数据信号直接从引脚通过输入缓冲器进入内部总线。

2.P2口

(1)结构。

P2口的位结构如图2.12所示。

图2.12 P2口的位结构

(2)功能。

控制信号为低电平,作I/O口使用,内部用上拉电阻代替了场效应管V1,使用方法与P0相同。

控制信号为高电平,作为高8位地址输出口。

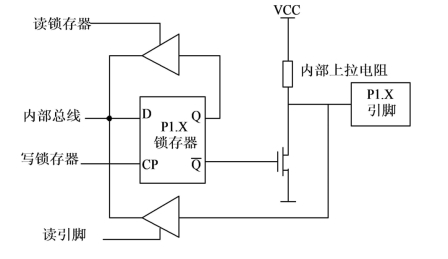

3.P1口(https://www.daowen.com)

P1口的位结构如图2.13所示。

P1口通常是作为通用I/O口使用的,内部用上拉电阻代替了场效应管V1。与P0口一样,也有读引脚和读端口两种情况。操作方法与P0口相似。

图2.13 P1口的位结构

4.P3口

(1)结构。

P3口位结构如图2.14所示。

图2.14 P3口的位结构

(2)功能。

①作I/O口使用。

第二功能信号为高电平时,与非门的输出由锁存器输出端Q决定,P3口作为通用输出口使用。而作为I/O使用的数据输入,与P2口相同仍取自三态缓冲器的输出端。

②具有第二功能。

P3口各引脚的第二功能如表2.13所示。第二功能信号有输入和输出两类,一类是:当P3口作为第二功能输出使用时,锁存器输出Q应为高电平,与非门的输出由第二功能输出端决定。另一类是:第二功能输入时,输入的第二功能信号从增加的缓冲器输出端取得。

不管是作为输入口还是第二功能信号输入,输出电路中的锁存器输出和第二功能输出信号线都应保持高电平,使场效应管截止。

表2.13 P3口各引脚第二功能定义

二、并行I/O口的负载能力

P0、P1、P2、P3口的电平与CMOS和TTL电平兼容。

P0每一口线以吸收电流方式可驱动8个LSTTL输入(1个LSTTL输入,高电平20μA,低电平0.36mA),用作通用I/O时,输出级处于漏极开路状态,集电极开路或漏极开路电路驱动时需外接上拉电阻。

P1、P2、P3口的每一位能驱动4个LSTTL负载。由于输出驱动电路设有内部上拉电阻故无须外接。

不同单片机,I/O口的负载能力不同。在设计单片机的硬件接口电路时,首先就要查询单片机I/O口的负载能力,以确定单片机在带负载时是否要加驱动电路。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。