【摘要】:PIE1是外围中断使能寄存器1,包含了多个外围中断的使能位。需要注意的是,要想让CPU响应这些中断源,前提是INTCON的PEIE位和GIE位必须置位。表6-4 PIE1寄存器数据位定义1)bit0TMR1IE:TMR1溢出中断使能位。2)bit1TMR2IE:TMR2对PR2匹配中断使能位。3)bit2CCP1IE:CCP1中断使能位。5)bit4TXIE:USART发送中断使能位。8)bit7PSPIE:并行从动端口的读/写中断使能位。

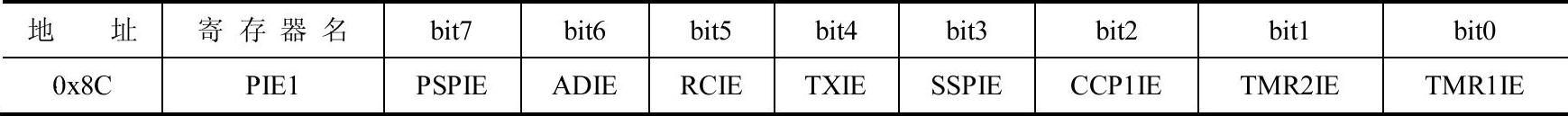

PIE1是外围中断使能寄存器1,包含了多个外围中断的使能位。其各个位名称如表6-4所示。需要注意的是,要想让CPU响应这些中断源,前提是INTCON的PEIE位和GIE位必须置位。

表6-4 PIE1寄存器数据位定义

1)bit0TMR1IE:TMR1溢出中断使能位。

1:允许TMR1溢出中断。

0:禁止TMR1溢出中断。

2)bit1TMR2IE:TMR2对PR2匹配中断使能位。

1:允许TMR2对PR2匹配中断。

0:禁止TMR2对PR2匹配中断。

3)bit2CCP1IE:CCP1中断使能位。

1:允许CCP1中断。

0:禁止CCP1中断。

4)bit3SSPIE:同步串行口中断使能位。

1:允许SSP中断。(www.daowen.com)

0:禁止SSP中断。

5)bit4TXIE:USART发送中断使能位。

1:允许USART发送中断。

0:禁止USART发送中断。

6)bit5RCIE:USART接收中断使能位。

1:允许USART接收中断。

0:禁止USART接收中断。

7)bit6ADIE:A/D转换器中断使能位。

1:允许A/D中断。

0:禁止A/D中断。

8)bit7PSPIE:并行从动端口的读/写中断使能位。

1:允许PSP的读/写中断。

0:禁止PSP的读/写中断。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。