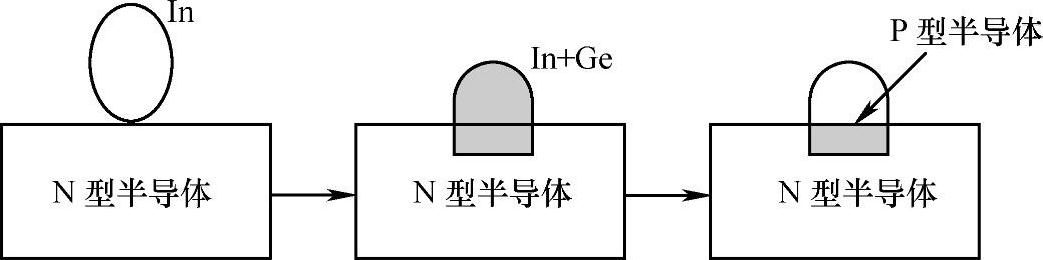

图3-1 合金法制造PN结的过程

PN结是指半导体的P型区和N型区的结合部。在通常情况下,半导体在PN结处只有掺杂情况的改变而无晶体结构的改变,即原子的周期性规则排列在该处必须连续。彼此分离的一块P型半导体和一块N型半导体的机械接触通常难以实现原子之间的连接,因而不能形成PN结。生产实践中一般通过异型掺杂局部改变材料导电类型的方法,或通过晶体的外延生长新生一层导电类型相反的材料层的方法,来形成PN结。利用掺杂方式形成PN结的工艺技术主要有合金法、扩散法和离子注入法。

合金法首先在半导体表面淀积一层异型掺杂物,然后在适当温度下加热,使界面处形成杂质与半导体的熔融薄膜,这层合金膜在随后的冷却过程中即形成与主体具有连续晶体结构的异型掺杂层。如图3-1所示用合金法制造PN结的过程。把一小颗铟球(In)放在N型锗单晶片上,加热到一定的温度,形成铟锗共熔体,然后降低温度,在降温过程中,锗便从共熔体中析出,沿着锗片的晶向再结晶。在再结晶的锗区中,将含有大量的P型杂质锢,使该区变成P区,从而形成了PN结。

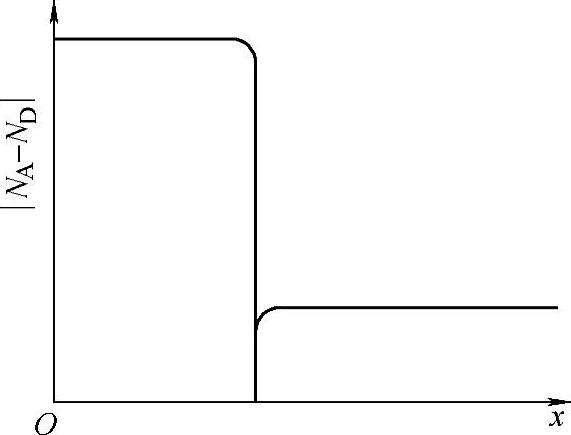

对于用这种方法形成的PN结,其杂质分布的改变具有突变性,因而称为突变结,如图3-2所示。N区中施主杂质浓度为ND,而且均匀分布;P区中受主杂质浓度为NA,也是均匀分布的。在交界面处,杂质浓度由从ND(N型)突变为NA(P型),具有这种杂质分布的PN就是突变结。实际突变结两边的杂质浓度相差很多,例如N区的施主杂质浓度为1016cm-3,而P区的受主杂质浓度为1019cm-3,通常把这种结称为单边突变结。对于单边突变结,若NA>>ND,则记为P+N结;若NA<<ND,则记为PN+结,右上角标+表示高浓度。早期的电力半导体器件多采用此法制造,但目前已不多用,因为杂质浓度和掺杂层的厚度在这种工艺中不易精确控制。

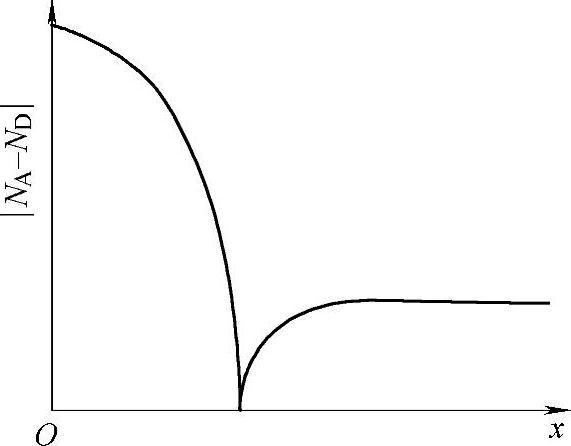

扩散工艺利用固体中的原子扩散原理,将N型半导体片(或P型半导体片)置于P型掺杂剂(或N型掺杂剂)的环境中,通过氧化、光刻、扩散等工艺让杂质原子从半导体片的表面向体内缓慢扩散。用这种方式掺入的杂质,其浓度总是表面高,体内低,在某确定深处的浓度与杂质的本性和扩散过程的温度高低及时间长短等多种因素有关。用扩散工艺形成的PN结,出现在扩散杂质与半导体内原有的异型杂质浓度相等的高度补偿之处,杂质分布的改变在这里比较平缓,因而称为缓变结,如图3-3所示。大功率的电力半导体器件基本上都要使用这种方法形成PN结的。

(https://www.daowen.com)

(https://www.daowen.com)

图3-2 突变结杂质浓度分布

图3-3 缓变结杂质浓度分布

离子注入法是目前最理想的掺杂方法之一,但所用设备比较复杂。该方法是把杂质元素(如硼、磷、砷)的原子,经过离子化变成带电的杂质离子,然后用强电场加速,获得高能量(约几万到几十万eV)的离子直接轰击到半导体基片内,经过退火激活,在体内形成一定杂质浓度的PN结。尽管其掺杂均匀性好,精确性和重复性高,但只在电力半导体器件制造业中小范围使用。

外延法是在半导体器件与集成电路制造业中普遍采用的一种半导体薄层生长技术。使用这种方法不仅可以在一块半导体片的表面延续一层异型掺杂薄膜,也可延续一层浓度不同的同型掺杂薄膜。前者形成的是PN结,后者形成的是PP+结或NN+结,统称为高低结。用这种方法比较容易获得较为理想的突变结,但生长层越厚,晶体结构的完美性越不易保证,对衬底表面的要求也就越高,因而在电力半导体器件,特别是高耐压器件的制造工艺中较少使用,但在功率集成电路和一些新型电力电子器件的制造工艺中则被普遍采用。

可见,采用不同的制作工艺,就会得到不同的杂质分布,但为了简化理论分析,通常将PN结的杂质分布分为突变结和线性缓变结两种情况。在本章中注重讨论的是双极型器件的基本工作原理,因此无特殊说明都假设PN结是突变结。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。