发展毫米波器件一直是高频频谱利用的先导,研制大宽带、低噪声、大功率、高效率、高可靠性、长寿命、多功能的毫米波器件是高频通信技术的关键。

过去几年中,有关毫米波通信频段(例如60 GHz)的研究已经变得相当重要,很多研究机构都在致力于这一频段通信系统的商业应用。高频传播衰减使其成为一个短距离通信方式,同时频点提升也带来了天线尺寸的减小,因此高频段通信(例如60 GHz)技术成为国内外研究的热点,也取得了显著的成就。

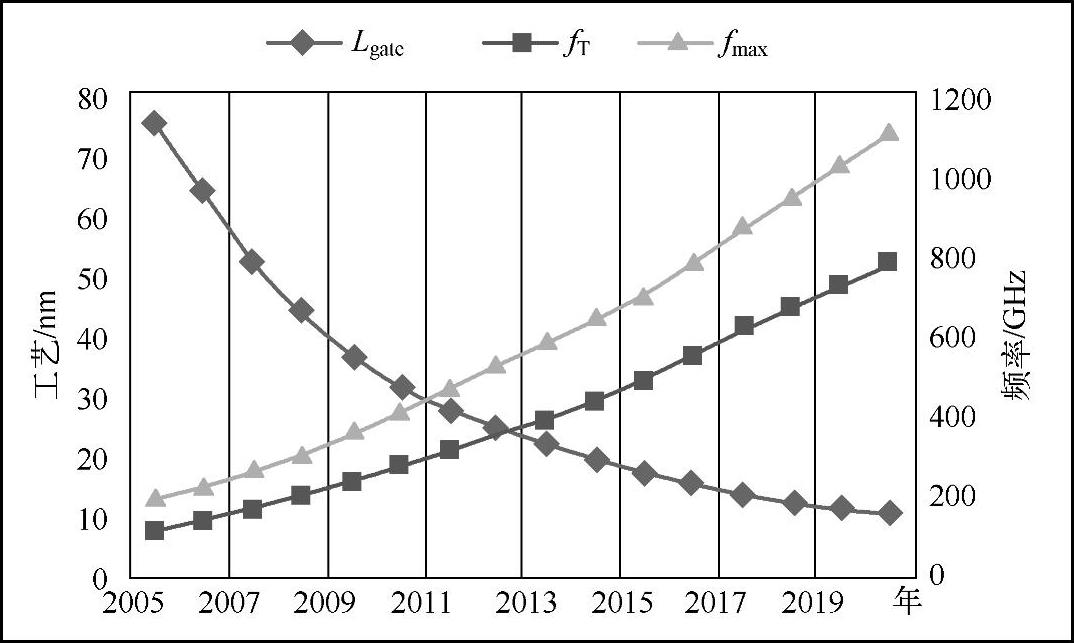

根据摩尔定律,毫米波是个不可避免的趋势。随着深亚微米和纳米工艺的日趋成熟,设计实现CMOS毫米波集成电路已经成为可能。随着CMOS尺寸的不断减小,截止频率不断提高,如图6-23所示,硅工艺成为了一种可行的替代毫米波的应用。虽然毫米波电路研究并非始于硅基,但是硅是毫米波电路的不二之选。许多以非硅为基础的技术,比如GaAs MES-FET、PHEMT、InP HEMT、GaAs MHEMT、GaAs HBT、InP HBT等,虽然其可以提供更高的工作频率,但它们价格昂贵,并且生产量较低,因此集成度有限。此外,这些工艺不像硅(特别是CMOS)技术发展迅速。行业和政府的投资,以及一个健康和充满活力的数十亿美元的市场,使硅工艺器件拥有稳定的产业规模。

图6-23 CMOS截至频率随工艺进步发展趋势

过去业界对硅基毫米波集成电路的研究比较少,人们认为在硅工艺上实现工作在高频段(如60 GHz)的集成电路是非常困难的。但近年来,这个课题已经引起了非常多的科研院所和公司的兴趣[19-22]。从通信发展史上看,以前大多数商业的研究兴趣集中在1~10 GHz频段的手机和手提电脑语音通信和数据应用方面。同时,快速增长的无线数据,如WiFi,在无线交换机中提供了新的构架,解决了短距离传输问题,尤其是针对视频和个人局域网。随着多媒体业务的增长,以及手持视频设备和快速被应用的高清网络电视和平板电视已经创立了一个健康的技术需求,这促使了高速无线视频传输的发展。如此大量的数据业务需求促使人们对毫米波硅基技术产生很大的兴趣。

毫米波CMOS集成电路是在基于CMOS射频集成电路(RFIC)的基础上发展起来的。对于CMOS RFIC的研究始于20世纪90年代,在之后的近十年中CMOS技术无论是在工艺、无源器件还是电路设计上都取得了巨大的进步。首先,从工艺上来讲,正如摩尔定律预言的那样,CMOS工艺自80年代以来从原先的3μm工艺发展到0.13μm,而如今更是缩小到几十纳米(nm)以下的纳米级工艺。另一方面,根据恒电场下的按比例缩小理论,随着CMOS工艺尺寸的不断缩小,CMOS晶体管的特征频率fT和最大振荡频率fmax将得到进一步提升。在标准90 nm CMOS工艺下,fT和fmax已经可以达到100 GHz以上。虽然CMOS技术与SiGe或InP技术相比,在晶体管的特征频率以及最大振荡频率上没有优势,因为在相同工艺尺寸条件下,后者可以轻易地获得更高的fT和fmax,但是低成本的CMOS技术已经可以应用于毫米波晶体管,这是一个重大的进步。同时,随着CMOS技术在工艺和无源器件上的进步,CMOS电路设计在近十几年来也得到迅猛发展,工作频率几乎以每十年提高一个数量级的速度上升。至今,无论是在哪个工作频段,设计高性能的LNA(低噪声放大器)、混频器和VOC(压控振荡器)总是研究重点,LNA处于接收前端的第一级,其噪声系数在很大程度上决定了整个前端的噪声性能,由于增益和噪声系数是相互矛盾的两个性能指标,因此设计实现兼具高增益、低噪声及低功耗的CMOS LNA非常困难。尽管如此,近两年来已经有人在毫米波频段的CMOS LNA做了尝试,其性能已经接近甚至超过采用InP实现的LNA。

在现在的集成电路设计中,“高集成度”的含义已经不再局限于单位芯片面积上能够集成多少晶体管,而是一个芯片上能够集成多大的系统,在这个系统里可以包含不同波段、不同功能的模块。应用CMOS工艺制作的毫米波集成电路与基带电路有着很好的一致性,为之后的系统集成提供了积极的先决条件。在短短几年中,高集成度和复杂的毫米波系统已被学术界和工业研究实验室所报道。这些全集成芯片由数千射频、数字晶体管和基于多金属层的硅芯片的片上无源器件组成,其中包括所有的接收器、发射器和交换机的模块,如低噪声放大器、混频器、压控振荡器、锁相环、功率放大器以及片上的天线。

毫米波CMOS收发前端的研究近年来取得了丰硕的成果。Razavi首先在60 GHz的频率范围内尝试用CMOS工艺实现收发前端[21]。随后又尝试将本振集成到接收链路中。文献[22]介绍了采用标准90 nm CMOS工艺制作的全集成60 GHz接收芯片,在工作频率范围内,芯片噪声低于8.3 dB,增益高于26 dB,已经比较接近最新研究的Bi CMOS工艺的结果,并且在功耗等方面有显著的优势。在射频集成电路设计中,有源器件通常用于驱动或放大电路,而无源器件多用于匹配网络电路。

毫米波前端电路设计的主要挑战以及我国在相应领域的一些发展如下。

(1)LNA

高频LNA基本设计方法和低频段上的LNA设计并没有太大的不同,需要工作在晶体管的截止频率附近,要充分考虑器件分布参数的影响,并在设计时需要精心考虑这些寄生参数。低噪声放大器作为整个通信电路的前端,其噪声性能制约了整个系统的指标。随着半导体工艺的进步,器件的特征尺寸不断减小,特征频率不断提高,器件的噪声特性和放大特性都有很大程度的提高。在过去五年对毫米波CMOS集成电路的研究中,低噪声放大器的特性有了很大的提高,某些性能已经不亚于商用Ⅲ-V族芯片。在我国中科院微电子所和中国科技大学、电子科技大学都已研制V-Band(46~56 GHz)频段上噪声系数分别为4.7 dB和5.7 dB、增益为18 dB和20 dB的90nm的CMOS器件。中科院上海微系统所支持W-Band(75~110 GHz)频段上NF为5 dB、增益为15 dB的GaAs器件。可以看到,在增益及噪声系数方面,现在的CMOS集成电路已经与商用芯片的性能相当接近。

(2)混频器

采用CMOS技术,在毫米波频段很难获得很大的本振功率输出,必须在一个合理的本振输出功率(通常为0 dBm)下设计满足要求的变频增益和噪声系数。毫米波频段的器件模型不准确也增加了使用复杂混频结构的难度。浙江大学在V-Band上支持带宽25 GHz且损耗小于10 dB的90 nm的CMOS器件。东南大学在W-Band支持带宽25 GHz且损耗小于14 dB的90nm的CMOS器件。(https://www.daowen.com)

(3)功率放大器

低工作电压和寄生电容(尤其是漏源电容)较大限制了放大器的高频最大输出功率;当前我国电子科技大学支持Q-Band(36~46 GHz)输出功率21 dBm、增益18 dB、90 nm CMOS器件;清华大学支持V-Band输出功率15 dBm、增益10.6 dB、65nm CMOS器件。

(4)振荡器和分频器

作为通信链路中的重要组成部分,传统的VCO一般由GaAs或SiGe工艺制成。CMOS工艺的导电衬底和闪烁噪声制约了CMOS VCO的相位噪声性能。清华大学可研制Q-Band和V-Band频段上PN=-110.3 dBc/Hz、带宽10 MHz、65 nm工艺的CMOS器件,电子科技大学可研制V-Band频段上PN=-95 dBc/Hz、带宽1 MHz、65 nm工艺的CMOS器件,东南大学支持研发W-Band频段上PN=-93 dBc/Hz、带宽10 MHz、130 nm的CMOS器件。

(5)封装和测试

由于毫米波的频率很高,封装所带来的寄生效应(如寄生电容、寄生电感、或者寄生耦合等)对毫米波电路的性能具有极大的影响。

(6)ADC和DAC

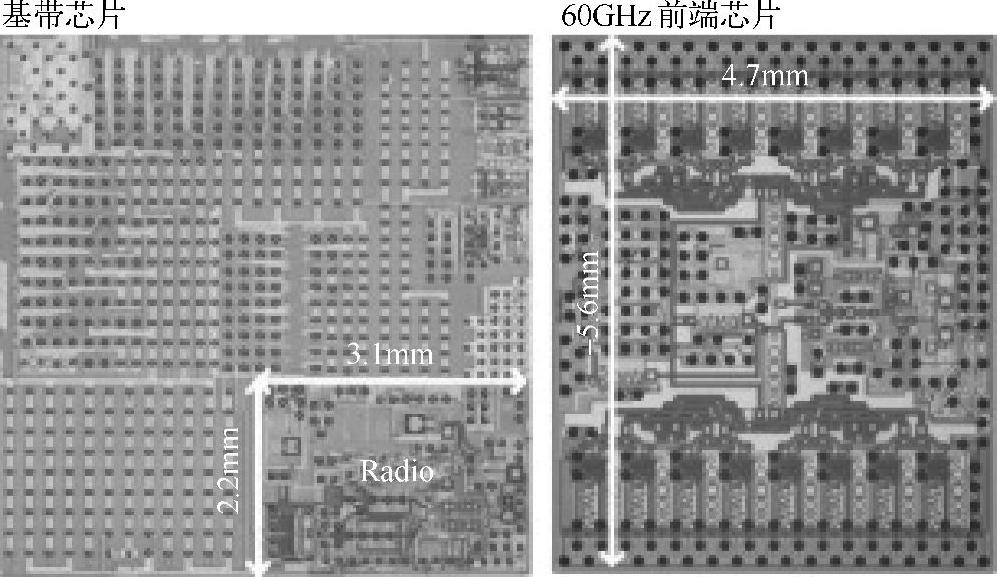

在ADC(Analog to Digital Converter,模数转换器)和DAC(Digital to Analog Converter,数模转换器)方面,以博通公司公开的60 GHz套片为例,如图6-24所示,该基带芯片含2.6 GS/s的ADC两个及DAC两个,基带芯片售价不高于50美元,按上述转换器面积比例折算,平均单个ADC/DAC成本不高于2美元。由此可见,因为成本、功耗、集成度方面的优势,采用主流CMOS工艺,且与CPU、逻辑、DSP等片上集成的数据转换器将替代独立数据转换器,成为商用高速系统的主流。

图6-24 博通芯片

国内众多企业及研究机构在高速数据转换器方面已经突破了基础技术问题,研究成果已经开始应用转化;西安电子科技大学和东南大学已验制出1GSps采样速率、6 bit采样带宽、0.18滋m工艺的COMS ADC器件,北京时代民芯科技有限公司可以提供3 GS/s采样速率、8 bit采样带宽、0.18滋m工艺的ADC COMS器件。在DAC COMS器件方面,中国电子科技集团公司第24研究所已研制1.2 GS/s采样速率、14 bit采样带宽、0.18μm工艺的COMS器件。通过产业政策的合理引导和系统架构的革新,数据转换器将不再对高速通信产业化形成制约。

随着国际上毫米波芯片的研究发展,国内研究机构已开展了毫米波芯片多领域研究,基本覆盖40~100 GHz收发信机的关键技术,已基本具备产业化的技术基础。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。