6.2.2.1 STM32与FPGA的接口设计

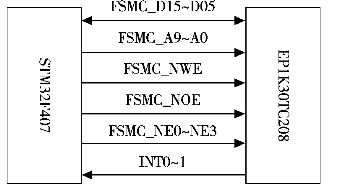

考虑到FPGA在多路并行数据处理方面有明显的优势,设计采用STM32F407的FSMC(Flexible Static Memory Controller,可变静态存储控制器)并行总线接口实现与FPGA的连接,并将FPGA当成STM32F407的外部SRAM来配置,通过扩展出的数据/地址/控制三总线来实现操作,这样既能保证较快的操作速度,又具有很高的灵活性。接口电路硬件连接如图6-11所示。

图6-11 STM32F407与FPGA接口连接电路

FSMC总线地址映射分为4个Bank,各占256M字节空间。其中Bankl可用来扩展SRAM,Bankl又分为4个region,设定region对应的片选信号(NE1-NE4)高低电平就可以选用不同的设备,且各设备对应的地址范围也不同。FAGA连接在FSMC总线的Bankl.region3中,HADDR总共有28根地址线(HADDR[27~0]),其中HADDR[26~27]用来对Bankl的4个区进行寻址。当FPGA使用region3时,对应的HADDR[27∶26]等于10。当Bankl在外接16位宽度存储器时候,只有HADDR[25∶1]是有效的,对应关系变为:HADDR[25∶1]->FSMC[24∶0],由此可知,接口地址FSMC_A[9~0]对应的HADDR的地址为0x68000000~0x680007FE,并且地址FSMC=HADDR>2,也就是当进行数据读写操作时,内部的HADDR地址为0x0004时,外部映射的FSMC总线地址则为0x0002。

6.2.2.2 数据采集的实现

(1)PPI符号信息的采集。

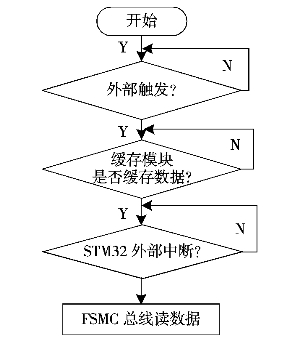

PPI符号信息包含符号启动脉冲、符号时钟、符号代码Ⅰ-Ⅵ共8路信号,其中符号启动脉冲与符号时钟作为采集控制的触发信号,决定整个采集控制模块的工作时序。采集流程图如图6-12所示。

图6-12 PPI符号信息采集流程图(https://www.daowen.com)

当产生外部触发信号后,8路并行数据通过集成电路74541进行缓存,并产生STM32外部中断信号触发STM32外部中断,进而控制FSMC总线进行读操作得到PPI符号信息。

(2)PPI符号位置信息的采集。

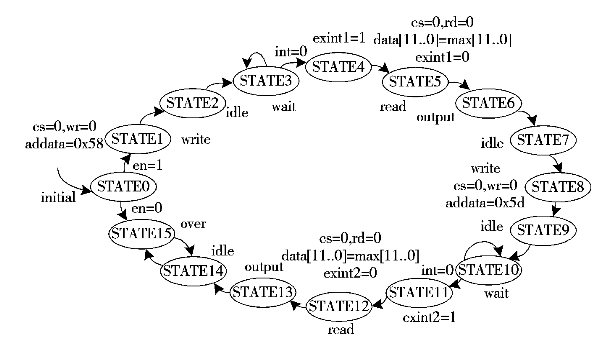

PPI符号位置信息包含符号水平偏转与符号垂直偏转两路模拟信号,采用MAX196进行AD转换。为了保证转换的实时性,设计了一种AD控制模块完成MAX196的采集时序控制,该控制模块采用状态机控制,是一种外部触发内部禁止的采集模式,如图6-13所示,实现了在一次符号时钟周期内完成对PPI符号两路偏转信号的连续采集,提高了采集的准确性和连续性。

图6-13 状态机控制流程

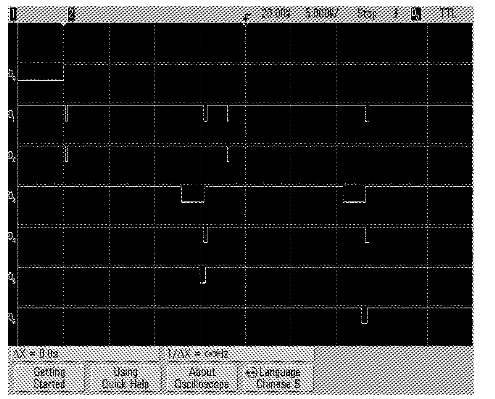

状态机的初始状态是STATEO,当外部触发信号满足要求,使en=1,转入STATE1,输出片选脉冲cs和写脉冲wr,使能AD转换,并且写入8位控制字,启动AD转换,进入STATE3,等待AD完成数据转换。转换结束时,AD产生中断脉冲int,接着进入STATE4、STATES,进而输出片选脉冲cs与读脉冲rd,转换的结果也存入data数据缓存器中,并产生STM32的外部中断触发信号,使exintl=0。STATE0-STATE7为第一个采集周期,,并自动进入下一个采集周期。STATE8-STATE14完成同样的采集控制过程,并在STATE15结束采集。直到下一个状态机的使能信号en到来后再次启动采集控制,该过程使用Verilog HDL语言来描述,时序仿真如图6-14所示,图中,D0-D6分别表示en、cs、wr、int、rd、exintl和exint2。

图6-14 AD控制模块的时序仿真

根据实际采集需求,AD的转换量程选择为10 V,采用双极性内部转换模式,需要进行2通道AD转换。由MAX196用户文档可知,通道0采集的8位控制字为0x5d,通道1采集的8位控制字为0x5c。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。