PC104总线有7种基本操作,对应7种不同的总线周期。其中,由CPU驱动的5种,由DMA控制器驱动的2种。

存储器读总线周期;

存储器写总线周期;

I/O端口读总线周期;

I/O端口写总线周期;

中断响应周期;

从存储器到I/O设备的DMA总线周期;

从I/O设备到仪器的DMA总线周期。

下面以应用较多的IO读、写介绍PC104总线操作。

6.1.3.1 IO读时序

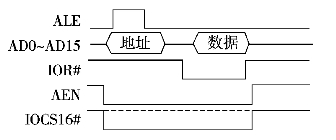

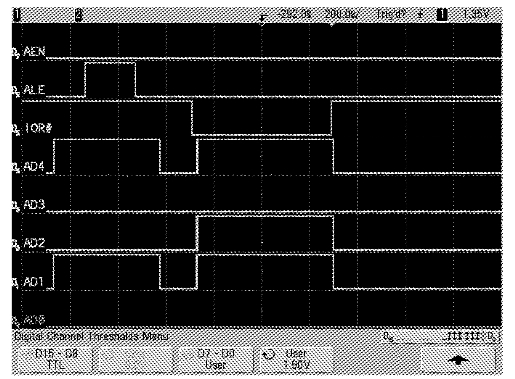

下面介绍用STM32F103的GPIO仿真PC104总线的基本思路。如图6-4所示,CPU首先置低AEN信号,标明总线由CPU控制。接下来送出地址信号,同时将ALE置高,并在地址线信号有效的情况下将ALE置低,以便地址在ALE高电平期间被锁存,然后撤销地址信号。在地址信号从地址数据复用总线上撤销后,将IOR#置低,此时设备端数据信号应出现在数据总线上,数据将在IOR#低电平期间读入到CPU内部,再将IOR#置高,通知设备数据总线上的数据缓冲区(或锁存器)可以进入高阻态,同时置高AEN,表明IO读总线周期结束,CPU释放总线控制权。执行读操作时,CPU根据IOCS16#信号确定设备是8位还是16位操作,当IOCS16#为低电平,按16位执行读操作,反之,按8位执行读操作。

图6-4 PC104总线IO读时序

6.1.3.2 IO写时序

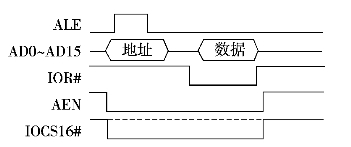

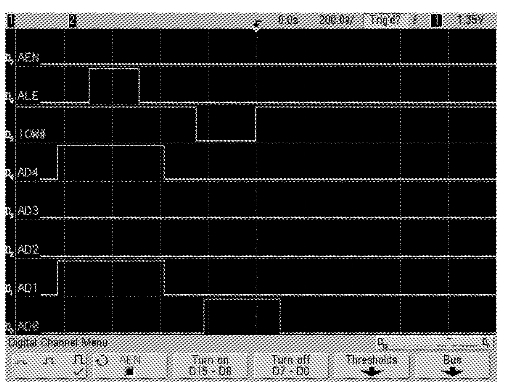

与IO读相似,如图6-5所示,CPU首先置低AEN信号,标明总线由CPU控制。接下来送出地址信号,同时将ALE置高,并在地址线信号有效的情况下将ALE置低,以便地址在ALE高电平期间被锁存,然后撤销地址信号。在地址信号从地址数据复用总线上撤销后,将IOW#置低,此时CPU将数据信号放到数据总线上,再将IOR#置高,数据将在IOW#上升沿被锁存到设备内部,同时置高AEN,表明IO写总线周期结束,CPU释放总线控制权。执行写操作时,CPU根据IOCS16#信号确定设备是8位还是16位操作,当IOCS16#为低电平,按16位执行写操作,反之,按8位执行写操作。

图6-5 PC104总线IO写时序

实际上PC104总线各信号与其时钟同步,上述描述并未考虑时钟,这主要是采用GPIO信号仿真PC104总线的时序过程是由软件实现的,因此,实际应用中是通过提高GPIO的速率或用软件延时等方法仿真PC104总线时序的。

用GPIO仿真PC104总线的关键之一是软件,软件控制着GPIO端口仿真三总线信号,按PC104总线的操作时序进行相应操作。其基本思想是根据硬件设计确定的GPIO端口与PC104总线的映射关系,将各GPIO信号进行宏定义,再根据PC104总线时序,按映射关系操作相应的GPIO端口。(https://www.daowen.com)

6.1.3.3 端口初始化

由于GPIO端口均为多功能复用端口,应用前应先对其初始化,初始化包括数据地址复用总线初始化和5条控制总线初始化,包括引脚选择,端口速率和输入输出方式配置。具体为:

PE端口定义为地址数据复用总线,对应16个引脚的输入输出方式配置为浮空输入,时钟频率设置为50 MHz;

PD端口定义为控制总线,其中PD4(ALE),PD11(IOR#),PD13(IOW#)与PD15(AEN)引脚输入输出方式设置为推挽输出,时钟频率设置为50 MHz。PD2是输入引脚(IOCS16#)引脚输入输出方式设置为浮空输入,时钟频率设置为50 MHz。

6.1.3.4 IO读软件设计

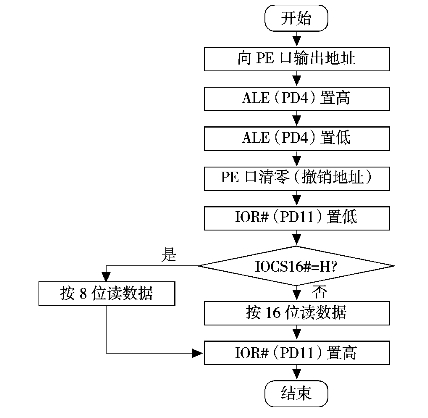

IO读基于PC104总线IO读时序编写软件代码。其流程如图6-6所示。

图6-6 仿真PC104总线IO读流程图

在CPU获得控制总线控制权的情况下AEN置低,在总线IO读开始前,将IOR#与IOW#置高,将ALE置低。IO读开始,STM32F103先向PE端口输出地址,然后置高ALE,以便于锁存地址信号,接下来置低ALE、清除地址。接着向设备发出读信号IOR#,即将PD11置低。根据IOCS16#电平状态,确定是按8位还是16位读入数据,然后将数据读入到CPU。数据读入后将PD11置高,IO读操作结束。

6.1.3.5 IO写软件设计

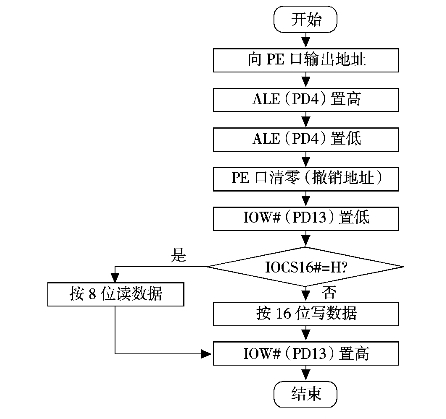

与IO读类似,如图6-7所示,在总线IO写开始前,将IOR#与IOW#置高,将ALE置低。IO写开始,STM32F103先向PE端口输出地址,然后置高ALE,以便于锁存地址信号,接下来置低ALE、清除地址。接着向设备发出写信号IOW#,即将PD13置低。根据IOCS16#电平状态,确定是按8位还是16位向设备写数据,然后将数据送到PE端口,将PD13置高,PD13(IOW#)的上升沿数据锁存到设备,IO写操作结束。

图6-7 仿真PC104总线IO写流程图

图6-8和图6-9分别为STM32F103仿真PC104总线实际读、写操作时序波形。其中数据地址只选取低五位显示。通过波形可见基本符合PC104总线时序。

图6-8 IO读逻辑分析仪时序图

图6-9 IO写逻辑分析仪时序图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。