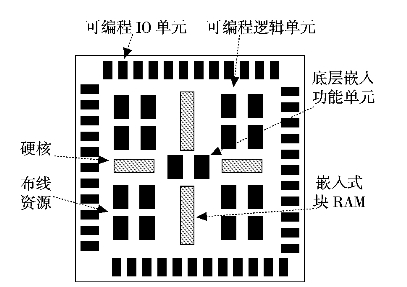

FPGA基本结构由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等,如图5-4所示。

图5-4 FPGA基本结构

每个单元的基本概念介绍如下。

1)可编程输入/输出单元。

输入/输出(Input/Ouput)单元简称I/O单元,它们是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配需求,为了使FPGA具有更灵活的应用,目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可以适配不同的电气标准与I/O物理特性;可以调整匹配阻抗特性、上下拉电阻,以及调整驱动电流的大小等。

可编程I/O单元支持的电气标准因工艺而异,不同芯片商、不同器件的FPGA支持的I/O标准不同,一般来说,常见的电气标准有LVTTL,LVCMOS,SSTL,HSTL,LVDS,LVPECL和PCI等。值得一提的是,随着ASIC工艺的飞速发展,目前可编程I/O支持的最高频率越来越高,一些高端FPGA通过DDR寄存器技术,甚至可以支持高达2Gbit/s的数据数率。

2)基本可编程逻辑单元。

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的逻辑功能。FPGA一般是基于SRAM工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT,Look Up Table)和寄存器(Register)组成。FPGA内部查找表一般为4输入,查找表一般完成纯组合逻辑功能。FPGA内部寄存器结构相当灵活,可以配置为带同步/异步复位或置位,时钟使能的触发器,也可以配置成锁存器,FPGA依赖寄存器完成同步时序逻辑设计。一般来说,比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存器与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。例如,Altera可编程逻辑单元通常被称为LE(Logic Element),由一个寄存器加一个LUT构成。Altera大多数FPGA将10个LE有机地组合在一起,构成更大的功能单元——逻辑阵列模块(LAB,Logic Array Block),LAB中除了LE还包含LE之间的进位链,LAB控制信号,局部互联线资源,LUT级联链,寄存器级联链等连线与控制资源。Xilinx可编程逻辑单元叫Slice,它是由上下两个部分组成,每个部分都由一个寄存器加一个LUT组成,被称为LC(Logic Cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合与级联。Lattice的底层逻辑单元叫PFU(Programmable Function Unin,可编程功能单元),它是由8个LUT和8~9个寄存器构成,当然这些可编程逻辑单元的配置结构随着器件的不断发展也在不断更新,最新的一些可编程逻辑器件常常根据需求设计新的LUT和寄存器的配置比率,并优化其内部的连接构造。

3)嵌入式块RAM。

目前大多数FPGA都有内嵌的块RAM(Block RAM),FPGA内部嵌入可编程RAM模块,大大地拓展了FPGA的应用范围和使用灵活性。FPGA内嵌的块RAM一般可配置为单口RAM,双口RAM,伪双口RAM,CAM,FIFO等常用存储结构。RAM的概念和功能读者应该非常熟悉,在此不再赘述。FPGA中其实并没有专用的ROM硬件资源,实现ROM的思路是对RAM赋予初值。所谓CAM,即内容地址存储器,CAM这种存储器在其每个存储单元都包含了一个内嵌的比较逻辑,写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。概括地讲,RAM是一种根据地址读,写数据的存储单元;而CAM和RAM恰恰相反,它返回的是端口数据相同的所有内部地址。CAM的应用也十分广泛,比如在路由器中的交换表等。FIFO是先进先出队列的存储结构。FPGA内部实现RAM,ROM,CAM,FIFO等存储结构都可以基于嵌入式块RAM单元,并根据需求自动生成相应的粘合逻辑以完成地址和片选等控制逻辑。

不同器件商或不同器件族的内嵌块RAM的结构不同,Xilinx常见的块RAM大小是4kBit和18kBit两种结构,Lattice常用的块RAM大小是9kBit,Altera的块RAM最灵活,一些高端器件内部同时含有3种块RAM结构,分别是M512 RAM,M4K RAM,M9K RAM。

需要补充的一点是,除了块RAM,还可以灵活地将LUT配置成RAM,ROM,FIFO等存储结构,这种技术被称为分布式RAM。根据设计需求,块RAM的数量和配置方式也是器件选型的一个重要标准。

4)丰富的布线资源。

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,这些布线资源根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;(https://www.daowen.com)

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有直接的关系。

5)底层嵌入功能单元。

底层嵌入功能单元的概念比较笼统,这里我们指的是那些通用程度较高的嵌入式功能模块,比如PLL(Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU等。随着FPGA的发展,这些模块被越来越多地嵌入到FPGA的内部,以满足不同场合的需求。

目前大多数FPGA厂商都在FPGA内部集成了DLL或者PLL硬件电路,用以完成时钟的高精度、低抖动的倍频、分频、占空比调整、相移等功能。目前,高端FPGA产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高。Altera芯片集成的是PLL,Xilinx集成的是DLL,Lattice的新型FPGA同时集成了PLL与DLL以适应不同的需求。Altera芯片的PLL模块分为增强型PLL和快速PLL等。Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM。这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接例化,另一种是在IP核生成器中配置相关参数,自动生成IP。另外可以通过在综合、实现步骤的约束文件中编写约束文件来完成时钟模块的约束。

越来越多的高端FPGA产品包含DSP或CPU等软处理核,从而FPGA将由传统的硬件设计平台逐步过渡到系统级设计平台。例如Altera的Stratix IV、Stratix V等器件族内部集成了DSP core,配合同样逻辑资源,还可实现ARM、MIPS、NIOS II等嵌入式处理系统;Xilinx的Virtes II和Virtex II pro系列FPGA内部集成了Power PC450的CPU Core和MicroBlaze RISC处理器Core;Lattice的ECP系列FPGA内部集成了系统DSP Core模块,这些CPU或DSP处理模块的硬件主要由一些加、乘、快速进位链、Pipelining和Mux等结构组成,加上用逻辑资源和块RAM实现的软核部分,就组成了功能强大的软运算中心。这种CPU或DSP比较适合实现FIR滤波器、编码解码、FFT等运算密集型运用。FPGA内部嵌入CPU或DSP等处理器,使FPGA在一定程度上具备了实现软硬件联合系统的能力,FPGA正逐步成为SOPC的高效设计平台。Altera的系统级开发工具是SOPC Buider和DSP Builder,专用硬件结构与软硬件协同处理模块等;Xilinx的系统设计工具是EDK和Platform Studio;Lattice的嵌入式DSP开发工具是Matlab的Simulink。

6)内嵌专用硬核。

这里的内嵌专用硬核与前面的底层嵌入单元是有区分的,这里讲的内嵌专用硬核主要指那些通用性相对较弱,不是所有FPGA器件都包含硬核。我们称FPGA和CPLD为通用逻辑器件,是区分于专用集成电路(ASIC)而言的。其实FPGA内部也有两个阵营:一个是通用性较强,目标市场范围很广,价格适中的FPGA;另一个是针对性较强,目标市场明确,价格较高的FPGA。前者主要指低成本FPGA,后者主要指某些高端通信市场的可编程逻辑器件。

FPGA器件在性能上主要有以下特点:

①FPGA器件采用SRAM编程技术,从而构成了高密度、高速度、高可靠性和低功耗的逻辑可编程器件。

②在使用FPGA器件时,需对其进行数据配置。配置完成后,FPGA器件才可完成设计要求的逻辑功能。当断电时,FPGA器件中的配置数据自动丢失。

③内部延时与器件结构和逻辑连接等有关,因此传输时延不可预测。

表5-1为Altera公司主要FPGA器件性能对照表,其中低成本、大批量设计应用可以采用Cyclone系列;高端设计应用可以采用Arria、Stratix等系列。

表5-1 Altera公司主要FPGA器件性能对照表

FPGA和CPLD均属于高密度密度PLD,两者区别见表5-2。

表5-2 CPLD/FPGA的区别

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。