CPLD器件的代表品种有Altera公司的MAX(1993年)、MAX II(2004年)、MAX V CPLD(2010年)系列、Lattice公司的ISP LSI1000、ISP MACH4000V/B/C/Z/ZE CPLD系列和Xilinx公司的XC7300系列等,这些器件都运用在系统编程(ISP)技术。

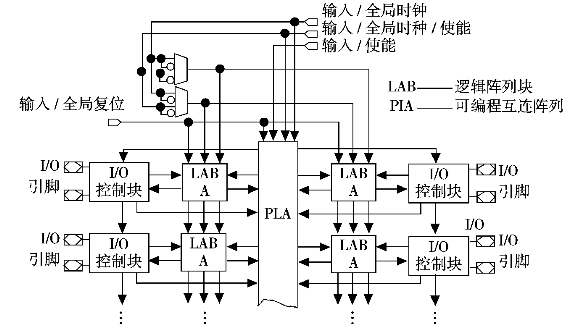

Altera公司的MAX7000系列器件是多阵列矩阵MAX(MultipleArrayMatrix)结构,如图5-3所示,主要由逻辑阵列块LAB(Logic Array Block)、I/O控制块和可编程互连阵列PIA(Programmable Interconnect Array)构成。

图5-3 MAX7000系列器件逻辑结构

MAX7000系列器件包含32~256个逻辑宏单元(Macrocell),每个逻辑宏单元由可编程的“与”阵列和一个固定的“或”阵列,以及一个具有独立可编程时钟、时钟使能、清除和置位功能的可配置触发器组成。每16个宏单元构成一个逻辑阵列块LAB。多个LAB通过可编程互连阵列PIA和全局总线相连。每个LAB还与相应的I/O控制模块相连,以提供直接的输入和输出通道。(www.daowen.com)

所有MAX7000系列器件的专用输入、I/O引脚和LAB均可与可编程互连阵列PIA相连。但只有每个LAB所需的输入、输出信号才通过PIA连线,因此,只有部分LAB输入和输出使用全局总线,从而降低了逻辑阵列规模。PIA有固定的传输延迟时间,实现的时序与器件内部逻辑布线无关。

I/O控制模块允许每个I/O引脚单独地配置成输入、输出、双向和三态方式,且逻辑电平为TTL电平;所有的I/O引脚都由全局输出使能信号控制。此外,MAX7000系列器件提供双I/O反馈结构,即宏单元和I/O引脚的反馈是相互独立的。当I/O引脚被配置为输入引脚时,与其相连的宏单元可以用作“隐埋”宏单元。MAX7000系列器件具有输出电压摆率控制、可编程保密位、可编程功率节省模式等优点,每个I/O引脚均具有ISP和集电极开路的特性。器件内部设有JTAG(Joint Test Action Group),联合测试行动组1边界扫描测试(Boundary Scan Testing,BST)电路,可通过JTAG接口实现在线编程(ISP)。

CPLD器件在性能上主要有以下特点:

①与GAL器件一样,CPLD可进行多次编程、改写和擦除。

②有多位加密位,因此可完全杜绝编程数据的非法抄袭。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。