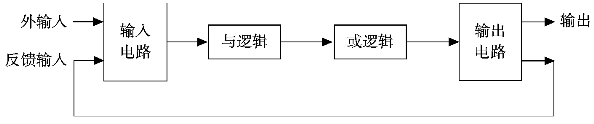

数字电路常用表达式之一是“与或逻辑式”,基于这一思路开发了PLD器件,其基本模型如图5-1所示,由输入电路、输出电路、与逻辑阵列及或逻辑阵列构成。

图5-1 PLD基本模型

其中,输入电路模块是把输入信号变为内部信号并具有一定的负载内部电路的能力,与逻辑模块实现乘积项输出(F=AB),或逻辑模块实现或运算(F=A+B),输出反馈电路模块主要完成直接输出或寄存输出及输出信号的反馈。

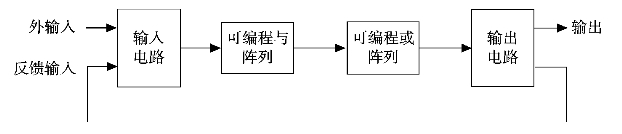

在PLD器件中通常把电路图画成阵列的形式,“与逻辑”“或逻辑”分别用阵列结构表示,并称其为可编程与阵列和可编程或阵列,阵列中交叉点处为“熔丝”结构,这些“熔丝”是可编程为连接或断开的,编程的过程由计算机在编程软件和编程器下完成。

一般的可编程逻辑器件(PLD)的基本结构如图5-2所示。其中,外输入及反馈信号经输入电路产生全部输入变量的原变量和反变量,经可编程与阵列完成与运算,产生多个所需的乘积项;又经可编程或阵列完成或运算,所需的“与-或”逻辑表达式信号就由输出电路输出。(www.daowen.com)

图5-2 PLD基本结构

由于一般PLD具有规模较大的可编程与阵列和可编程或阵列,所以常用符号表示可编程交叉点的连接关系,称为编程单元。交叉点上的“×”符号表示此编程单元编程为连接,“.”符号表示此编程单元为固定连接(不可编程),无任何标记则表示此编程单元编程为不连接。

根据可编程逻辑器件的制造工艺不同,目前PLD编程单元不仅只是二极管熔丝结构一种,而是有多种类型。一般编程单元可分为易失性和非易失性两种。易失性编程单元采用的是SRAM结构,其特点是器件掉电后,编程信息丢失,现场可编程门阵列(FPGA)采用的就是这种类型。非易失性编程单元采用的是EPROM,EEPROM等结构,其特点是编程信息可长期保存,在器件掉电后,编程信息仍不会丢失。非易失性PLD又可分为一次性编程PLD和多次性编程PLD。一次性编程采用熔丝型开关、反熔丝型开关为编程单元。多次性编程采用的是利用绝缘栅场效应管栅极层中存储电荷,并使开启电压发生变化的浮栅结构。

除上述的PLD基本结构外,目前还有一类可编程逻辑器件采用查找表结构。查找表实际上是一个逻辑函数发生器,其工作原理类似于用ROM实现组合逻辑函数。查找表的输入等效于ROM的地址码,通过查找ROM中的地址码表,可得到对应的逻辑输出。

随着集成工艺的发展,PLD的集成规模越来越大,当前PLD已发展到万门以上的复杂可编程逻辑器件(Complex Programmable Logic Device,CPLD)系列,以及更大规模的现场可编程门阵列(Field Programmable Gate Array,FPGA)。CPLD和FPGA大都采用各种分区的阵列结构,即将整个器件分成若干的区。有的区包含有若干个I/O端、输入端及规模较小的“与”“或”阵列和宏单元,相当于一个小规模的PLD;有的区则只是完成某些特定逻辑功能。各区之间可通过几种结构的可编程全局互连总线连接。编程时,同一模块的电路一般安排在同一区内,因此只有少部分输入和输出使用全局互连总线,从而大大降低了逻辑阵列规模,缩小了电路传输延迟时间。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。