数字集成电路中的定型产品主要是供各种寄存器(锁存器)、计数器等供选用,设计者可按所需功能在“数字集成电路手册”中查阅芯片型号,了解其引脚信号作用及电平要求。了解成品时序逻辑电路的构成方式,有助于准确选用成品电路和丰富设计思路。

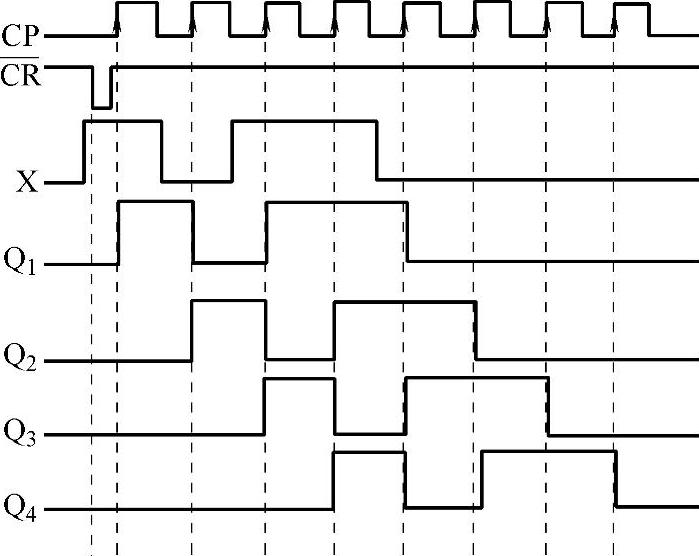

分析时序逻辑电路的原理主要针对触发器的使用和动作方式。同步触发器的动作,做真值表或波形图时,首先要确定触发器输出状态变换的时间(或时刻),然后再依据输入信号决定输出状态。

上升沿触发是触发器的状态变化发生在CP信号由低电平上升变为高电平的时刻,在真值表中用↑表示,在波形分析时,把箭头符号表示在CP脉冲上,成为“ ”状。下降沿触发是触发器的状态变化发生在CP信号由高电平下降变为低电平的时刻,在真值表中用↓符号表示,在波形分析时,把箭头符号表示在CP脉冲上,成为“

”状。下降沿触发是触发器的状态变化发生在CP信号由高电平下降变为低电平的时刻,在真值表中用↓符号表示,在波形分析时,把箭头符号表示在CP脉冲上,成为“ ”状。

”状。

1.寄存器

寄存(锁存)信息是D触发器的基本应用,按功能可分为数码寄存器和移位寄存器两种。1个D触发器存放一位二进制代码,N个触发器组成可存放N位代码的寄存器。

(1)数码寄存器

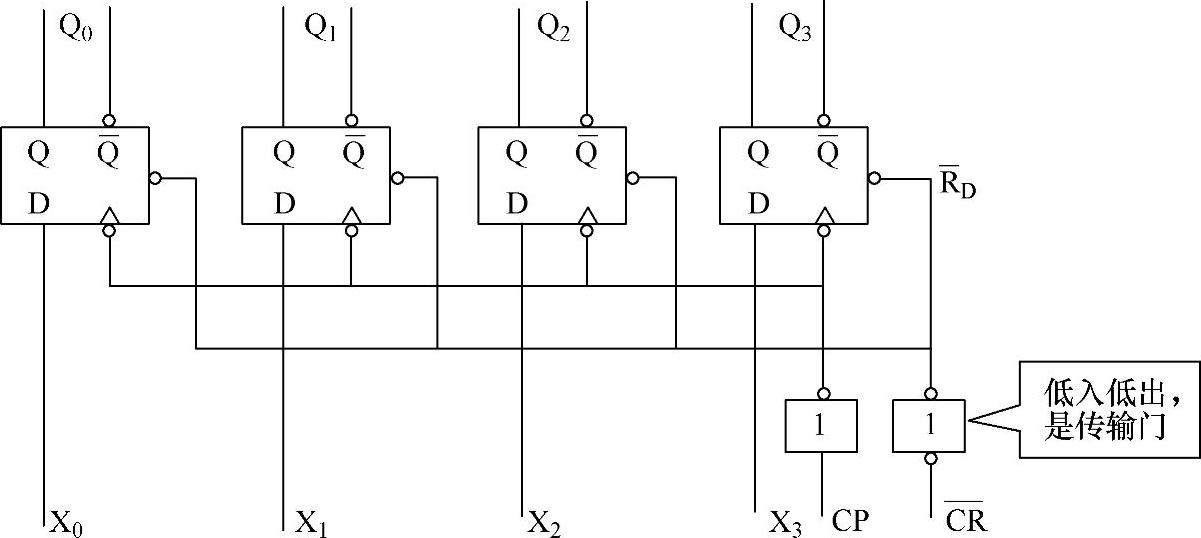

数码寄存器按存储数据的位数用多个D触发器并排方式构成,采用同步式结构,把各触发器的CP信号接在一起。图4-117所示为4位数码寄存器。

图4-117 4位数码寄存器

电路用4个D触发器构成。CP为上升沿有效。CR为清零信号,低电平有效。X3、X2、X1、X0为寄存器的4位输入端,Q3、Q2、Q1、Q0为输出端。

数码寄存器是专用于暂存数据的,常用于存放数据、指令等二进制代码。数据可随时按原样存入,并能随时读出。

写入的数据送到输入端,CP信号为数据写入脉冲,CP有效时刻各触发器的输出端立即更新,并保持不变,直到有新数据输入和CP触发。

当 时,各触发器直接受控复位,使

时,各触发器直接受控复位,使 、

、 、

、 、

、 均为零,称为寄存器清零。

均为零,称为寄存器清零。

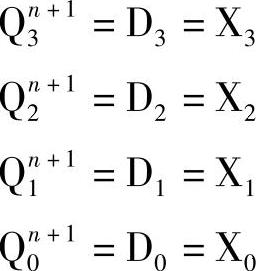

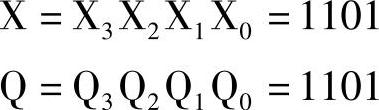

当 =1、CP=

=1、CP= 时,4位触发器同时接收数据输入:

时,4位触发器同时接收数据输入:

如:

在 并且CP无效时间里,触发器保持原状态不变。

并且CP无效时间里,触发器保持原状态不变。

读操作是从寄存器各输出端取电平信号,被存储数据不受影响。

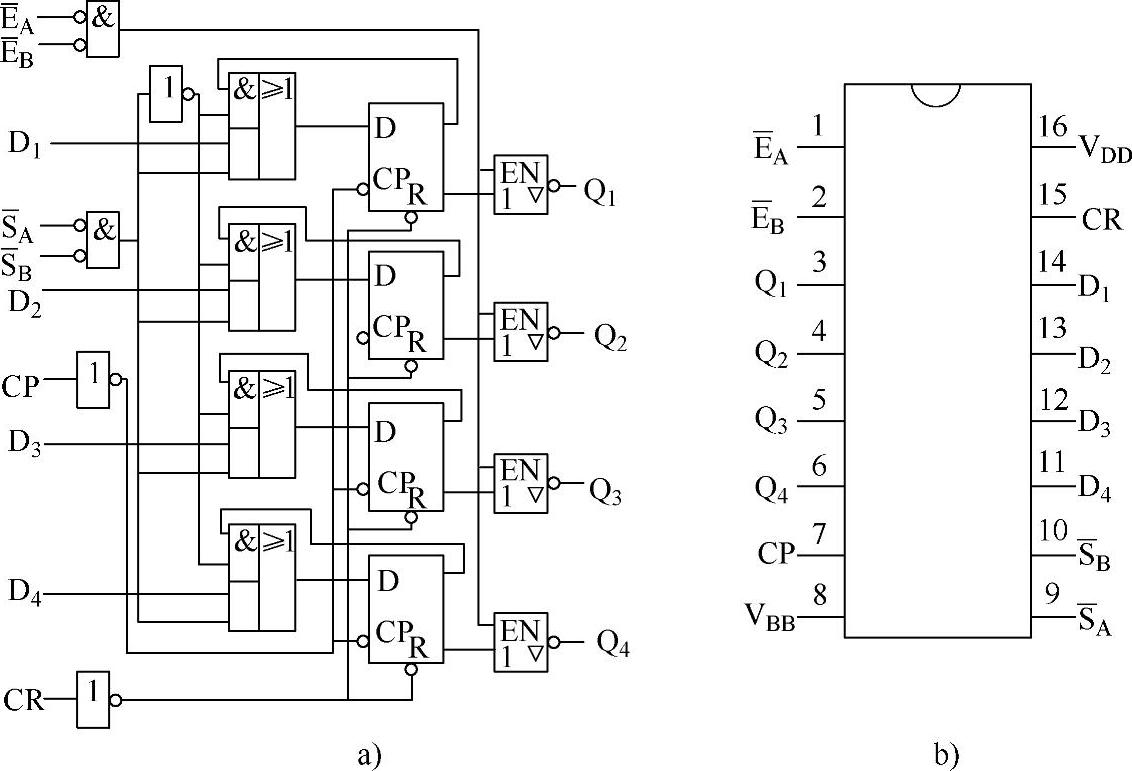

4076为4位D寄存器,其内部结构和引脚功能如图4-118所示。

4076为三态输出的4位D寄存器,它是以图4-117所示的电路为基础,增加控制电路(由三态输出门、使能信号逻辑、选通信号逻辑、时钟逻辑组成)和控制信号构成。

、

、 为电路的使能信号,控制三态输出门,两信号同时为低电平时,电路进入使能状态,有信号输出,否则为高阻态。

为电路的使能信号,控制三态输出门,两信号同时为低电平时,电路进入使能状态,有信号输出,否则为高阻态。

与

与 为电路输出信号的选通信号,两信号同为低电平时,数据才能输入;其他状态时,选通电路被封锁,电路保持原状态。

为电路输出信号的选通信号,两信号同为低电平时,数据才能输入;其他状态时,选通电路被封锁,电路保持原状态。

时钟逻辑电路将触发器要求的下降沿触发倒相为上升沿触发。表4-47为4076的电路功能表。

图4-118 4位D寄存器4076的内部结构和引脚功能

表4-47 4076的电路功能表

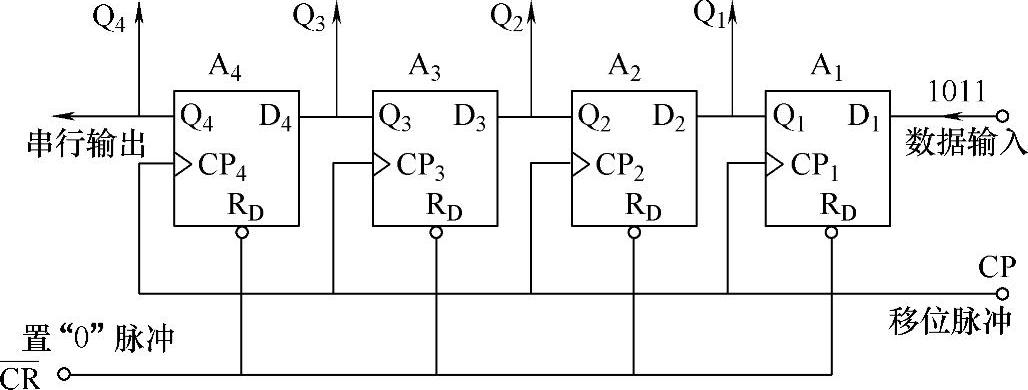

(2)移位寄存器

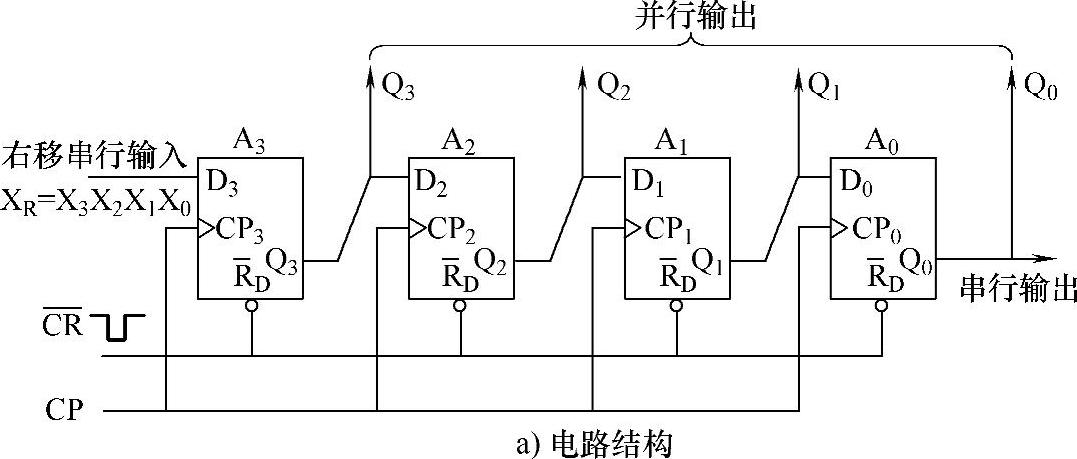

对数据有移位功能的寄存器称为移位寄存器,用多个D触发器彼此以输出端接输入端的串联方式连接,采用同步触发移位,它能在移位脉冲作用下将数据逐位移动。各触发器的时钟CP接在一起作为移位脉冲输入端,在把每个触发器的CR接在一起作为清零信号输入端。

移位寄存器主要用于数据循环移位和串行与并行传输方式的相互转换。按移位方向化分,有单向移位和双向移位两种类型。

1)单向移位寄存器。单向移位寄存器分左移位和右移位两种,两种单向移位寄存器的结构相同,只是各触发器的连接方式变换一下方向。

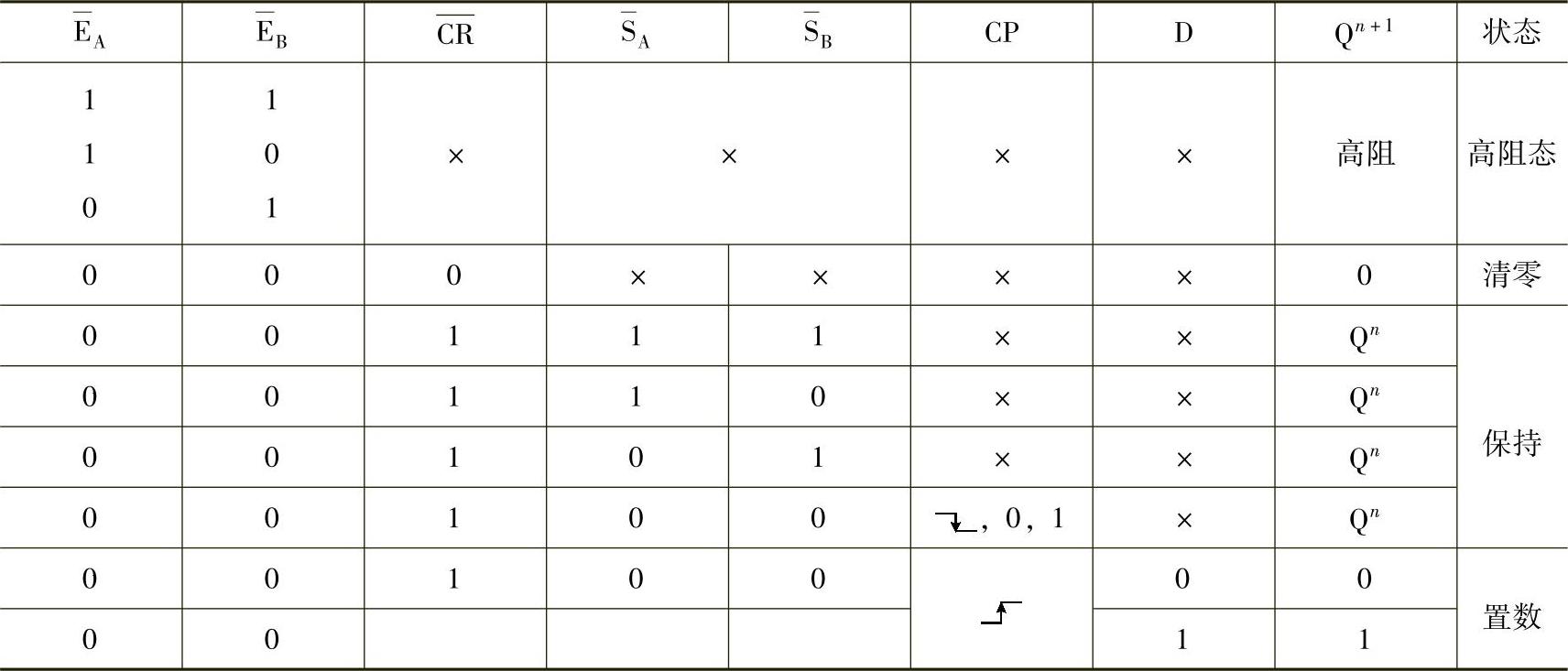

左移位寄存器是指数据以串行方式从寄存器右端(低端)输入,在移位脉冲控制下逐位左移,经N次移位,数据全部移入寄存器到达对应位置可以并行方式输出,实现串行数据向并行数据的转换。数据也可以并行方式输入,经N次左移,数据从寄存器左端以串行方式输出,实现并行数据向串行数据的转换。左移寄存器如图4-119所示。

图4-119 左移寄存器

数据在寄存器内的移位过程如图4-120所示。

图4-120 左移寄存器工作时序图

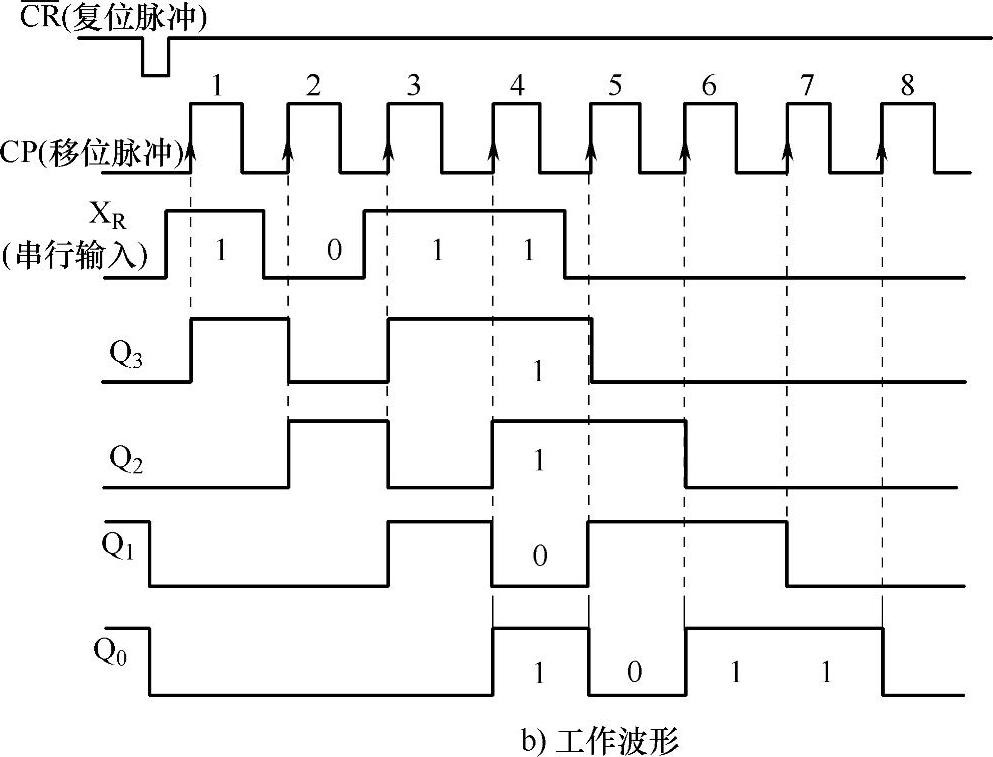

右移寄存器的操作与左移动作相反,图4-121所示为右移寄存器的结构和工作时序波形图。

图4-121 右移寄存器及工作波形

图4-121 右移寄存器及工作波形(续)

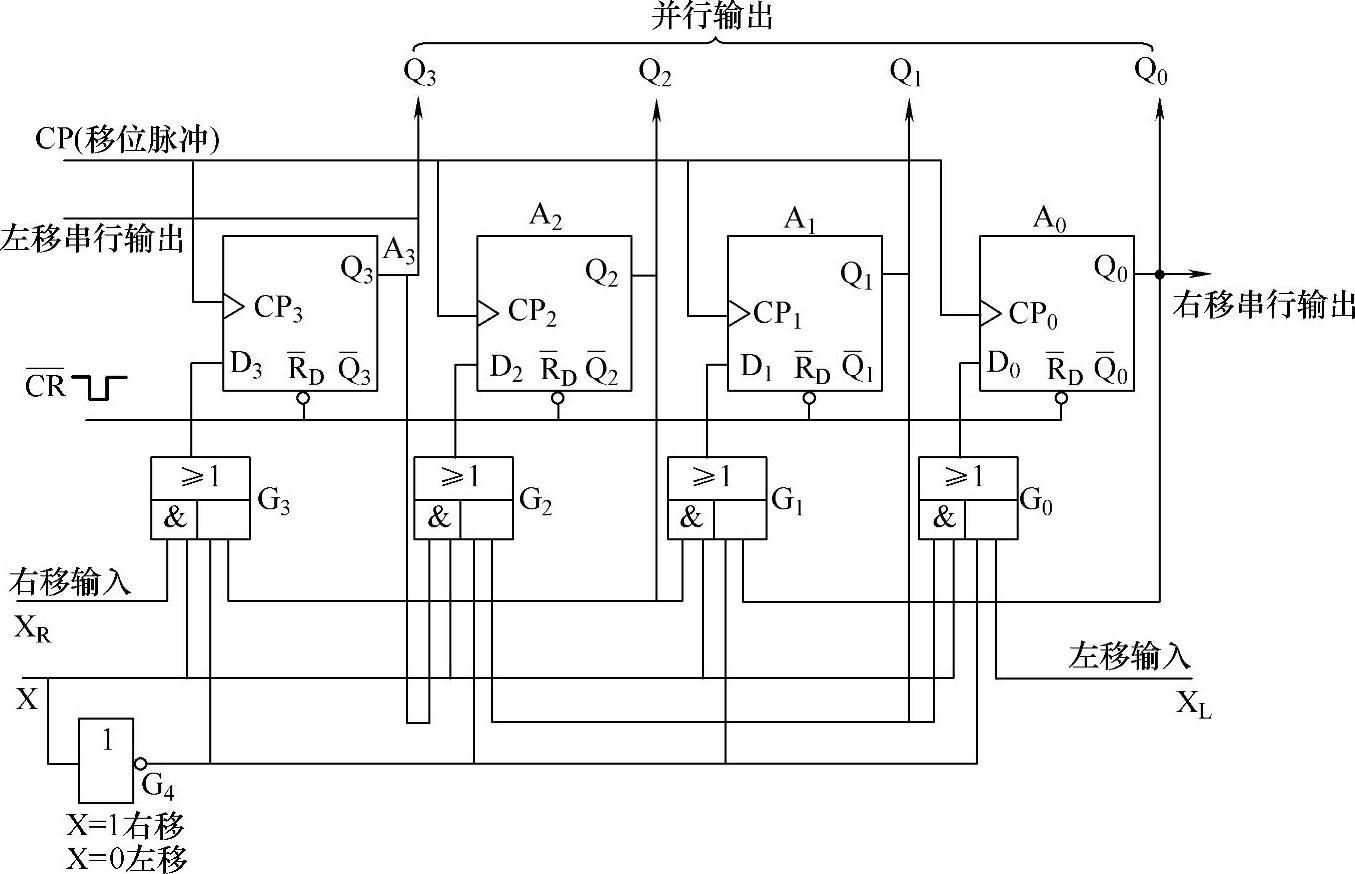

2)双向移位寄存器。既能左移又能右移的寄存器称为双向移位寄存器,图4-122所示为双向移位寄存器的结构。

图4-122 双向移位寄存器的结构

双向移位寄存器是以单向移位电路为基础,增设用与或门G0、G1、G2、G3构成的换向控制逻辑和控制信号X组成。XR为右移输入端,XL为左移输入端。

X=0时,电路为左移寄存器,数据按先高后低顺序从左移输入端XL串行输入,由低向高移位:

X=1时,电路为右移寄存器,数据按先低后高顺序从右移输入端XR串行输入,由高向低移位:

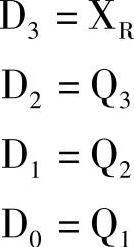

图4-123所示为74194(4位双向移位寄存器)的内部结构和引脚信号。4个R-S触发器转换为4个D触发器构成寄存器主体,DSR为右移串行输入端;RSL为左移串行输入端,D0、D1、D2、D3为并行输入端, R为低电平有效的清零信号,S1,S0为操作模式选择信号,CP为上升沿触发的移位脉冲信号,4个R-S触发器被转换为4个D触发器,Q0、Q1、Q2、Q3为并行输出端。Q0为左移串行输出端,Q3为右移串行输出端。表4-48为74194功能表。

R为低电平有效的清零信号,S1,S0为操作模式选择信号,CP为上升沿触发的移位脉冲信号,4个R-S触发器被转换为4个D触发器,Q0、Q1、Q2、Q3为并行输出端。Q0为左移串行输出端,Q3为右移串行输出端。表4-48为74194功能表。

图4-123 74194内部电路

表4-48 74194功能表(https://www.daowen.com)

2.计数器

对脉冲信号能进行计数的电路称为计数器,当脉冲信号为频率稳定的时钟信号时,计数器又具有定时器和分频器的功能。

按电路状态变换特点不同可分为加法计数器和减法计数器,接触发方式不同可分为同步计数和异步计数,按进位信号输出与电路动作关系可分为十进制计数、N位二进制计数和任意进制计数,按计数器的电路结构可分为直线形、环形、扭环式多种。

计数器通常用于为脉冲电路提供定时或波形准确的输入信号。

(1)二进制计数器

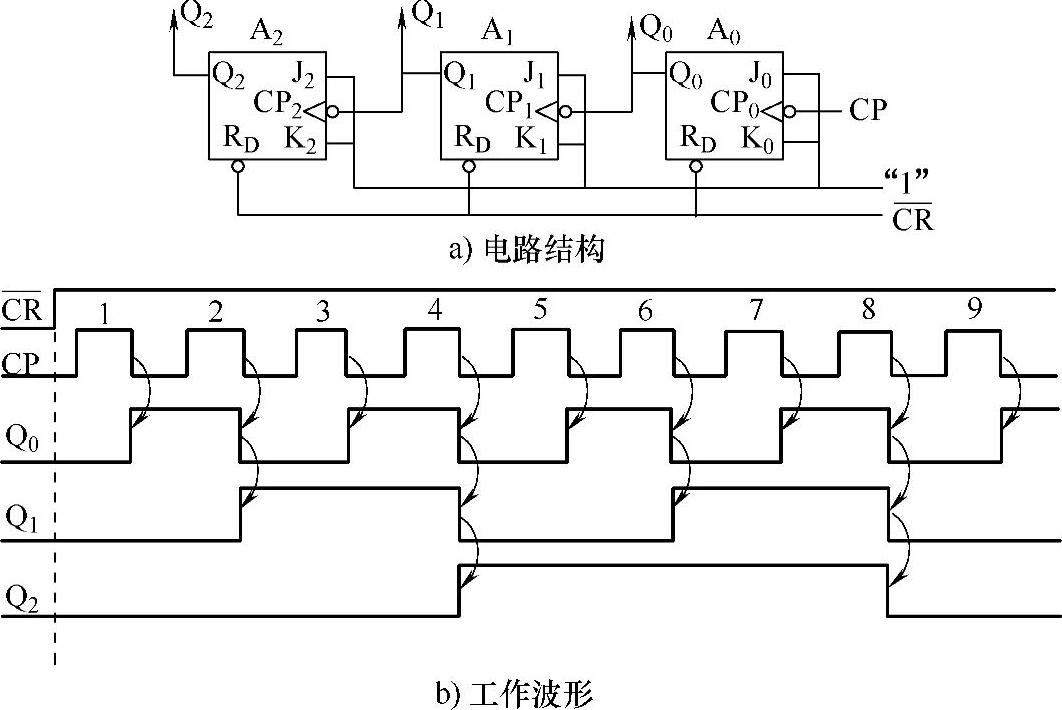

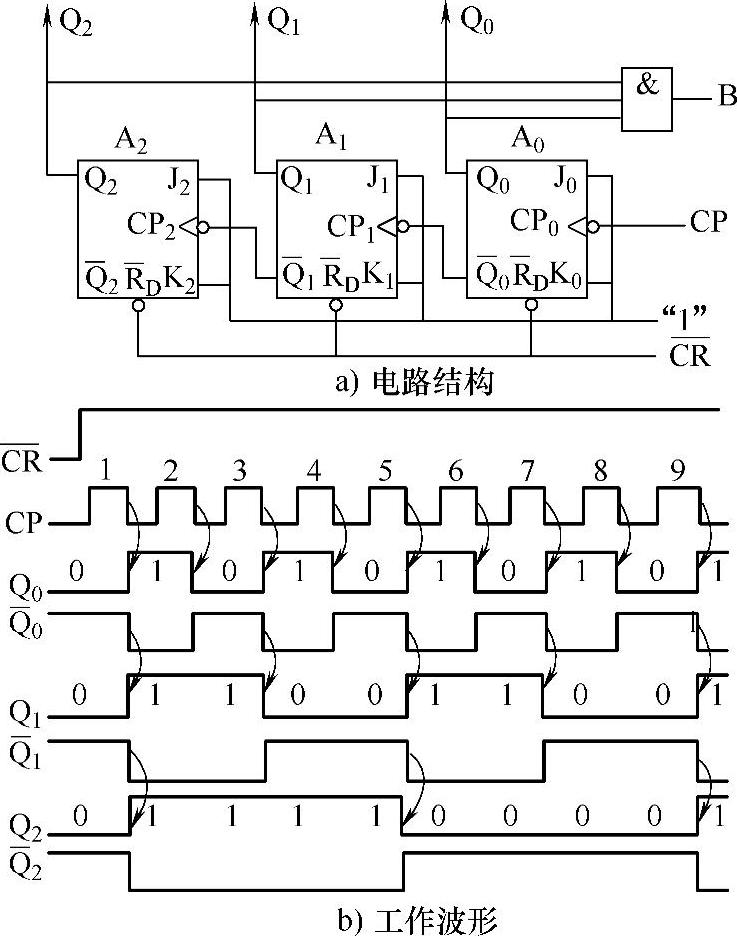

1)异步二进制计数器。异步二进制计数器的结构最简单,图4-124所示为3位二进制异步加法计数器。

图4-124下 降沿触发的3位二进制异步加法计数器

一个T′触发器就是一位二进制计数器,异步二进制计数器是用多位T′触发器串联成递进触发方式构成的,触发器之间的连接方式由触发器的触发方式和计数方式决定。

图4-124a所示电路的功能分析:

电路由3个转换为T′触发器的J-K触发器串联组成。T′触发器的输入信号为计数脉冲,下降沿触发。

电路的时钟信号连接:

三个T′触发器在自己的时钟信号触发下实现计数输出:

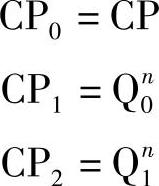

图4-125所示为电路计数输出的状态转换图。

从电路的时序图、状态转换及触发关系表(见表4-49)和状态转换图,都能说明它是一个3位二进制异步加法计数器,既能实现二进制加法计数,又具有分频功能。

图4-125 二进制加法计数器状态转换图

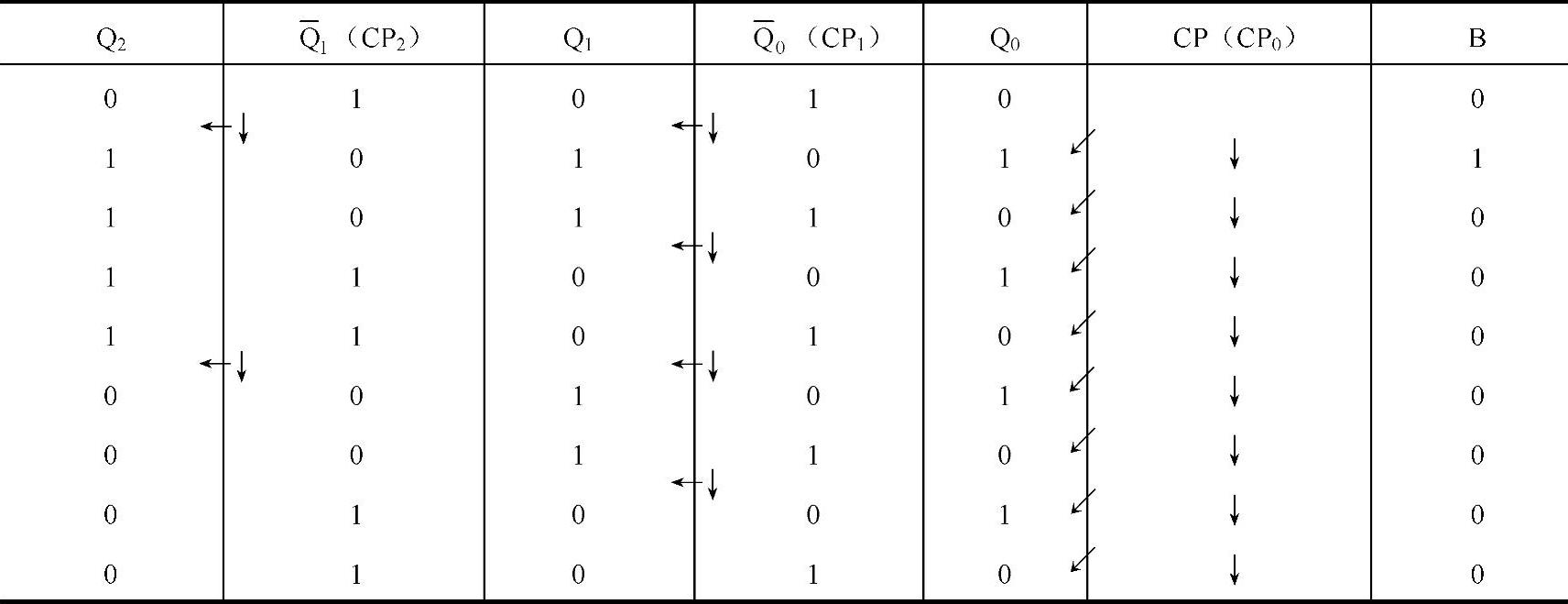

表4-493 位二进制异步加法计数器状态转换及触发关系表

计数器具有分频功能,计数器3个输出端的信号频率与最低端输入的计数脉冲信号频率的关系如下:

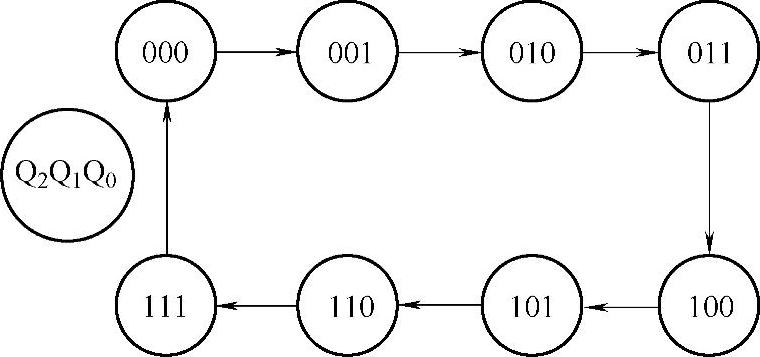

电路如果用上升沿触发的T′触发器组成,电路结构和时序图如图4-126所示。

图4-126 上升沿触发的3位二进制异步加法计数器

上升沿触发的T′触发器用D触发器转换构成。

改变触发器之间的连接方式,就可构成减法计数器,图4-127所示为3位二进制异步减法计数器。

图4-127 3位二进制异步减法计数器

电路中B为Q2Q1Q0=000状态减1时向高位的借位信号,B=Q2Q1Q0电路的状态转换见表4-50。

表4-50 3位二进制异步减法计数器状态转换表(下降沿触发)

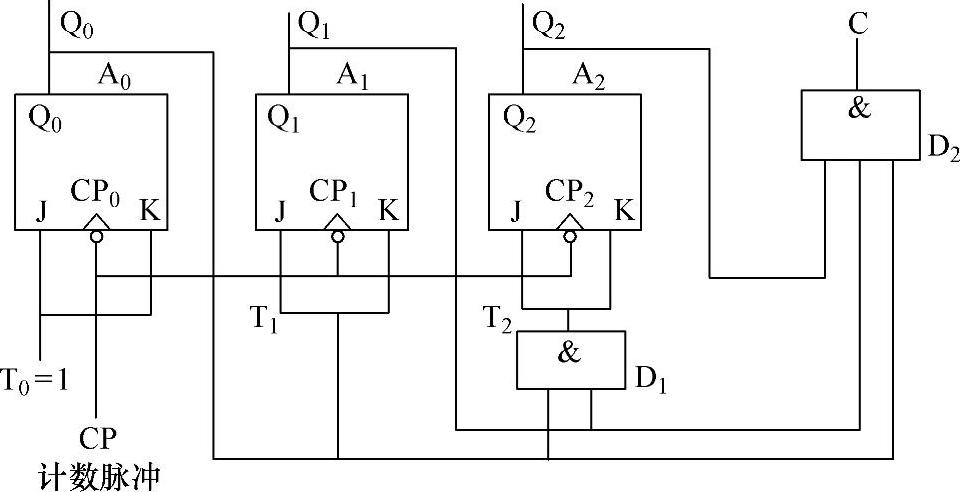

2)同步二进制计数器。异步二进制计数器电路结构虽简单,但速度较慢(触发器只能逐级翻转)。如果将这种计数器的输出信号传给译码器,会使译码电路出现竞争冒险,产生尖峰脉冲。同步计数器可弥补这两点不足。

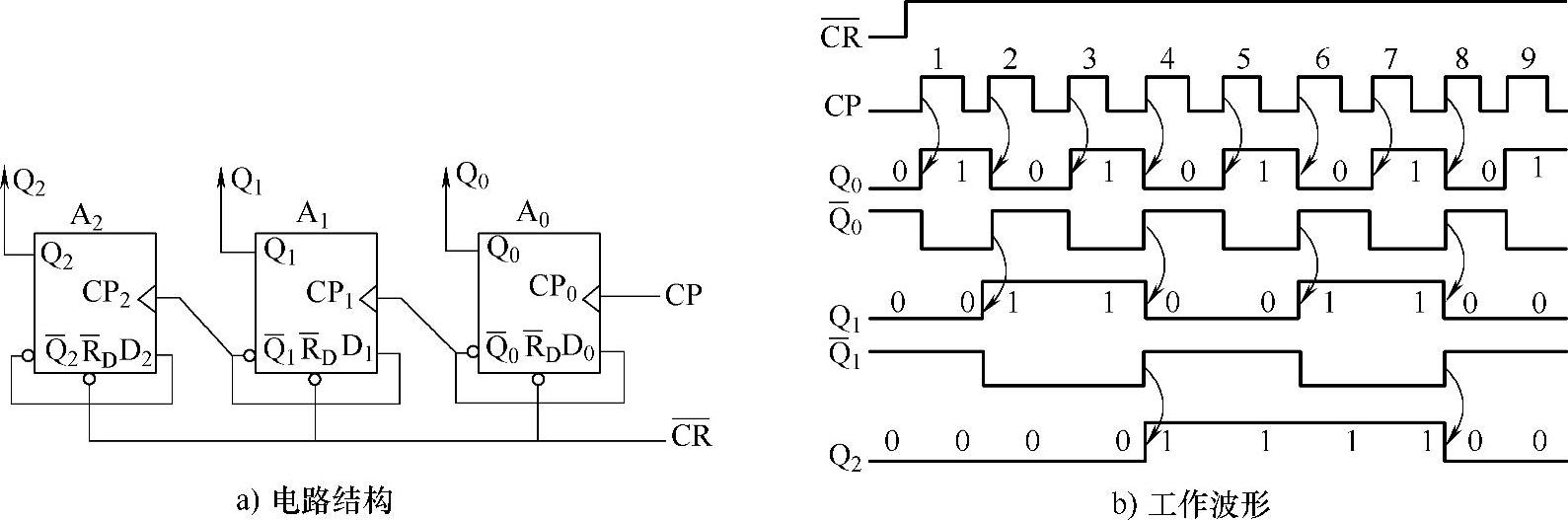

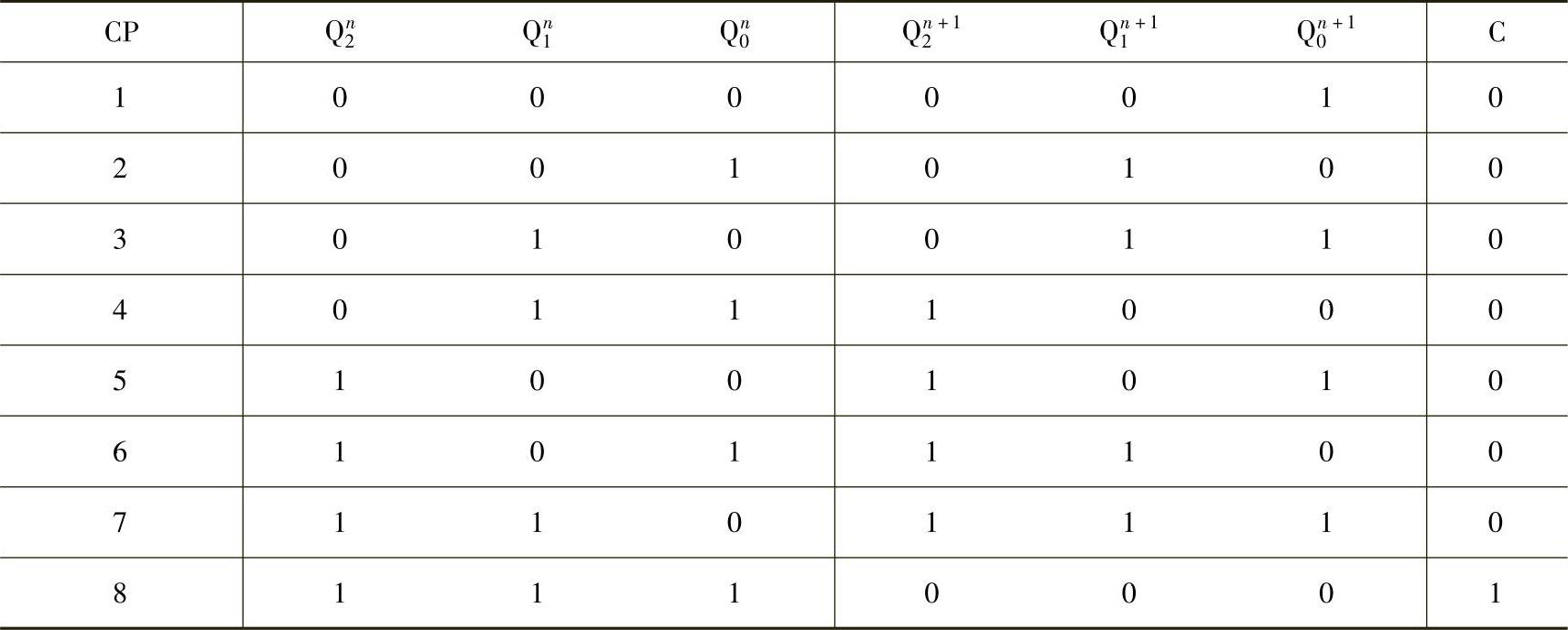

3位二进制同步加法计数器的结构如图4-128所示,其状态转换关系见表4-51。

图4-128 用T触发器组成的同步二进制加法计数器

表4-51 同步计数器状态转换真值表

计数器电路主体用3个J-K触发器进行功能转换实现:

FF2和FF1为T触发器,FF0选为T′触发器。

进位信号C=Q2Q1Q0。

(2)十进制计数器

按“逢十进一”规律进行计数的电路称为十进制计数器。

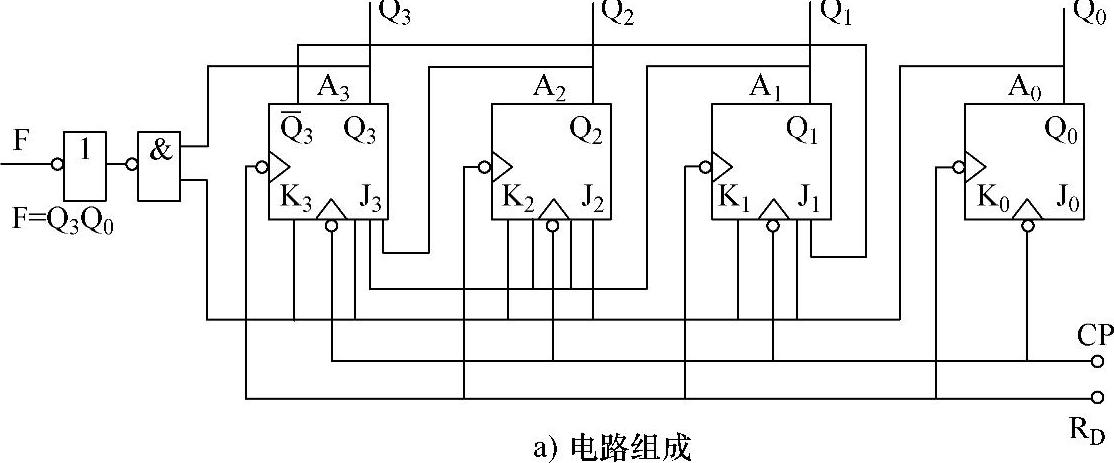

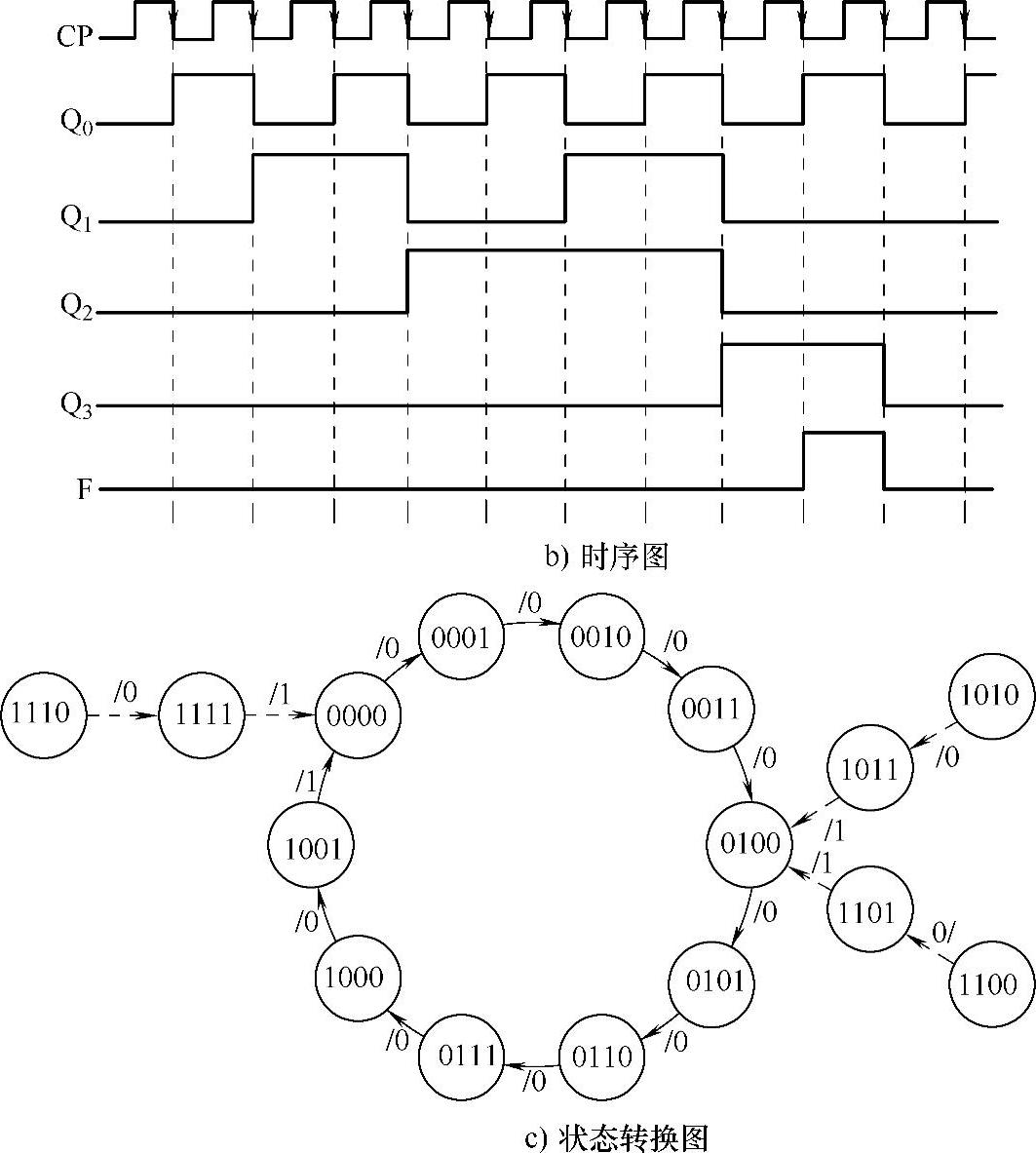

1位按8421BCD码同步十进制计数器的逻辑图以及时序图和状态转换图如图4-129所示。

图4-129 同步十进制加法计数器电路组成、时序图、状态转换图

图4-129 同步十进制加法计数器电路组成、时序图、状态转换图(续)

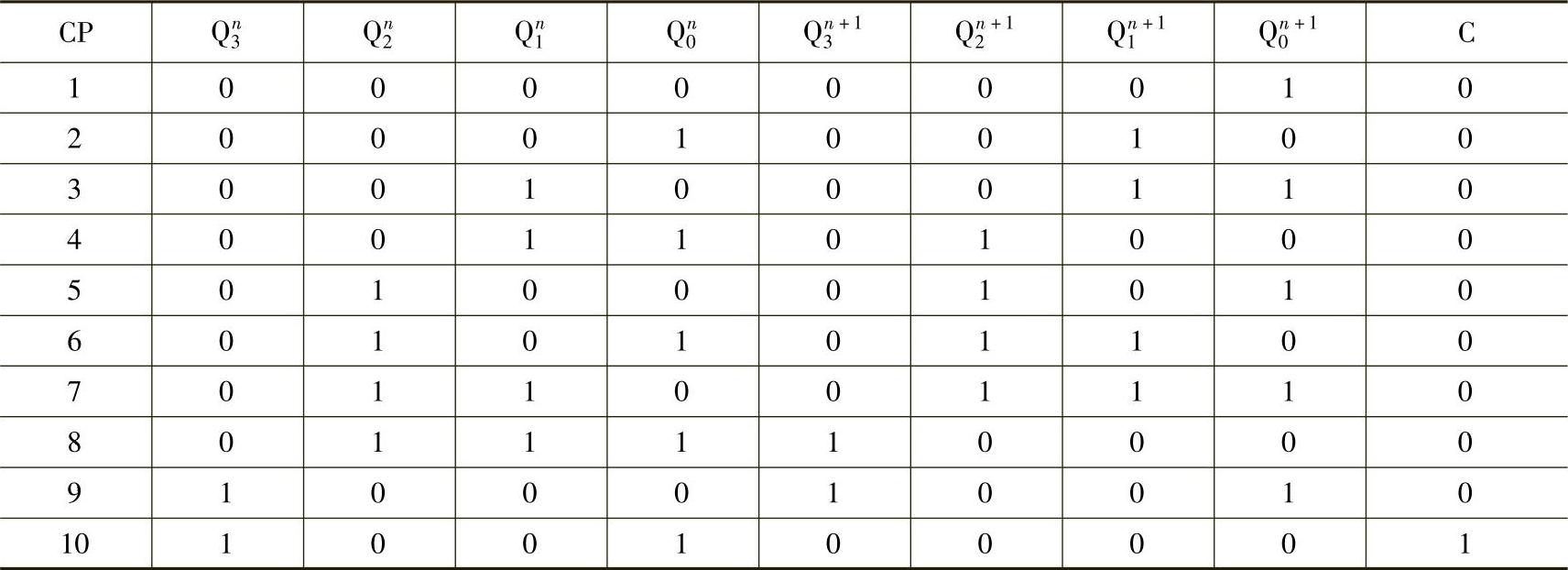

1位十进制计数器应该有10种不同状态。依据2n-1<N≤2n的关系,需用4位触发器FF3、FF2、FF1、FF0构成电路,电路的状态转换关系真值表见表4-52。

表4-52 8421码十进制加法计数器状态转换表

电路中4个触发器FF3、FF2、FF1、FF0都用J-K触发器,但FF2实际是T触发器,FF0为T′触发器,是计数脉冲输入端。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。