把输出信号引回输入端,形成信号反馈,在电路中构成自锁定功能,既是时序逻辑电路的结构特征,也是触发器构成的基本原理。

1.基本R-S触发器

基本R-S触发器的结构最简单,既是一个独立品种,又是构成其他触发器的基本单元。

依据实际使用需要,基本R-S触发器的输入信号有高电平有效与低电平有效的区别,由不同逻辑门构成。

(1)输入信号高电平有效的基本R-S触发器

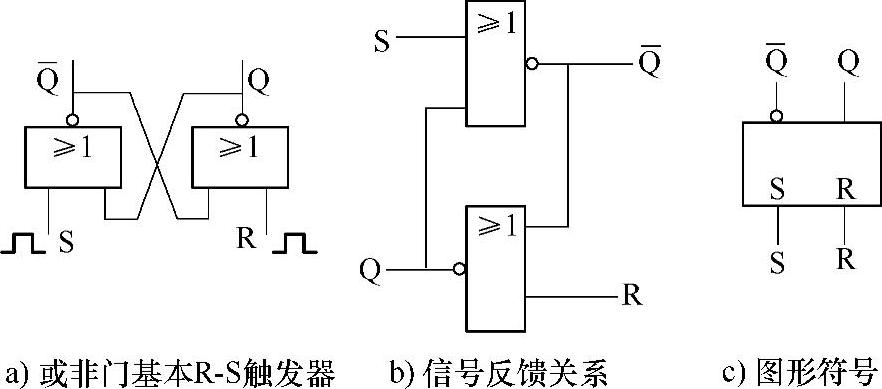

1)电路构成。输入信号高电平有效的基本R-S触发器用或非门构成,如图4-94a所示。

图4-94 或非门基本R-S触发器、信号反馈关系、图形符号

图4-94b所示为信号反馈关系,基本R-S触发器的输入信号S为置1(即置位SET)信号,R为置0(即复位RESET)信号。

图4-94c所示为或非门基本R-S触发器的图形符号。触发器的图形符号用矩形框表示,有时在框中用触发器名称字母或FF作标识。

2)功能分析与输出端定名。基本R-S触发器的输入、输出信号各有两个。可按输入信号确定输出名称,也可先确定输出信号位置,再按对应关系确定输入信号名称。

或非门的输入、输出规律是“输入有1、输出为0;输入全0、输出为1”。一个输入端的1(高电平)可屏蔽其他输入端的0(低电平),所以由或非门构成的基本R-S触发器功能如下:

R=0,S=0(两信号都无效)时,两个或非门相互锁定,保持触发器的原来状态,Qn+1=Qn,称为触发器的保持态。

R=0(无效态)、S=1(有效态)时,称为触发器的置1(也叫置位)状态,无论触发器的现态Qn为何值,此时次态都为1(即Qn+1=1)的输出端为Q,另一输出端为 。图4-94中输入、输出信号的名称依此定位。

。图4-94中输入、输出信号的名称依此定位。

R=1(有效态)、S=0(无效态)时,称为触发器的置0(也叫复位或清零)状态,无论触发器的现态Qn为何值,此时Q端的次态应是0,即Qn+1=0。

R=1,S=1(两个信号都有效)时,两个或非门输出都为0,为异常的不定态。显然这种情况是不允许出现的,在使用中要注意约束。

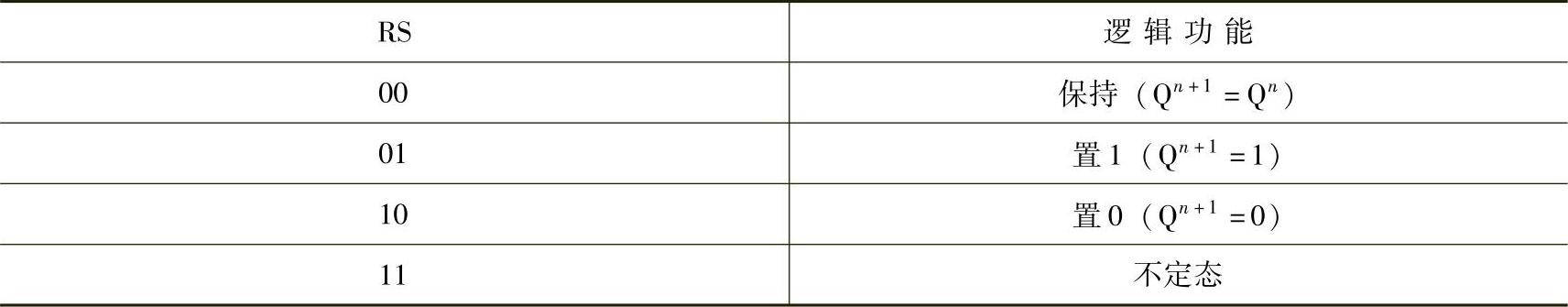

归纳或非门基本R-S触发器的逻辑功能见表4-37。

表4-37 或非门结构R-S触发器的逻辑功能

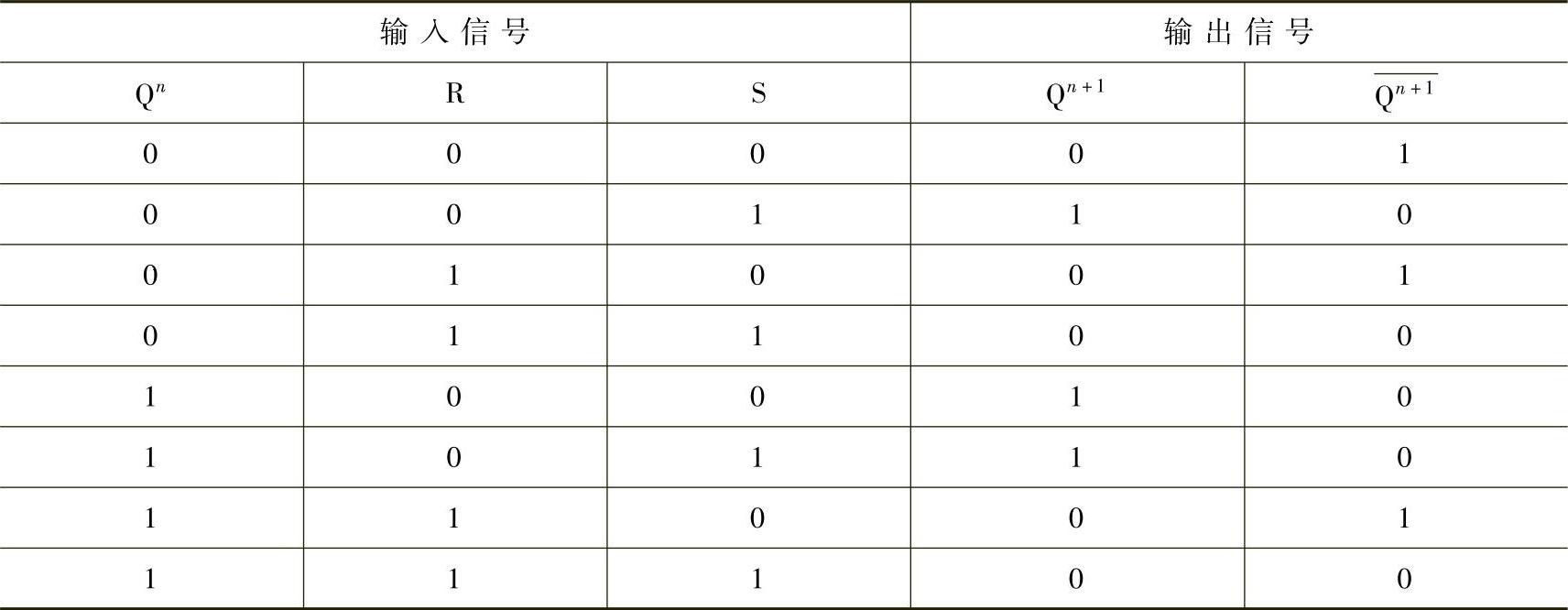

3)逻辑真值表和特性方程。在触发器的电路中,输出信号的现态Qn是次态Qn+1的输入信号,利用逻辑功能表得出真值表,见表4-38。

表4-38 高电平有效的基本R-S触发器逻辑功能真值表

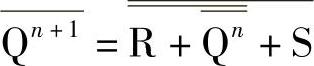

按真值表对或非门基本R-S触发器的逻辑进行化简,如图4-95所示。

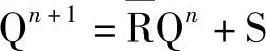

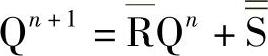

化简后得出输入信号高电平有效触发器的特性方程:

并转换为或非—或非式:

与图4-94所示或非门基本R-S触发器结构一致。

为约束R、S不能同时为1,要求RS=0。

4)逻辑波形图。触发器的逻辑功能也可以用输入、输出信号时序波形图的对应关系表示。图4-96所示为或非门结构R-S触发器的一例波形图,设触发器初态Qn=0。

图4-95 或非门基本R-S触发器逻辑化简

图4-96 或非门结构R-S触发器的波形图

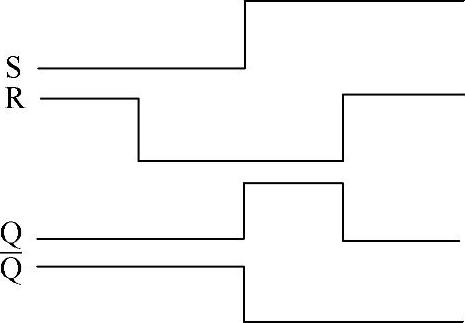

5)或非门结构的基本R-S触发器产品。CMOS系列产品中的CC4044B含4个或非门结构的基本R-S触发器,单元电路如图4-97所示。

图4-97 CC4044B的单元电路和引脚功能

电路的输入端都有非门转换输入信号的有效电平。CC4044B的单元触发器采用单端并经三态门(由CMOS管构成)输出,4个触发器的三态门由引脚⑤的E(使能)信号控制。

(2)输入信号为低电平有效的基本R-S触发器

实际中常给字母加非号表示信号低电平有效,所以触发器的两个低电平有效的输入信号用 、

、 表示。

表示。

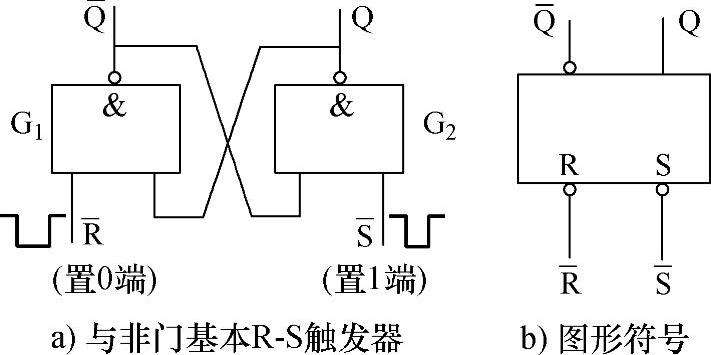

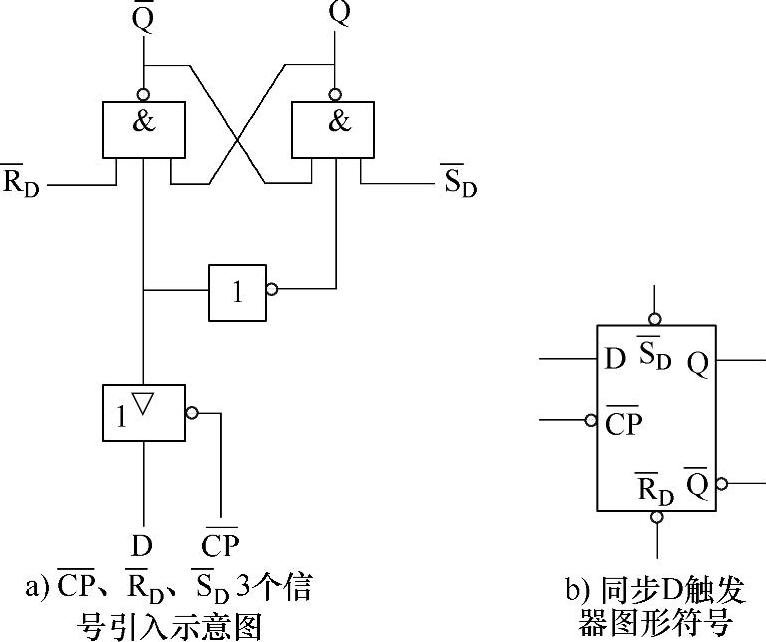

1)电路构成。输入信号低电平有效的基本R-S触发器用与非门构成,如图4-98a所示。

图4-98 与非门结构的基本R-S触发器

图4-98b所示为与非门结构的基本R-S触发器图形符号,图中给输入信号线上加小圆圈,表示该信号为低电平有效。

2)功能分析。对于与非门,输入、输出规律是“输入有0、输出为1;输入全1、输出为0”,一个输入端的0可屏蔽其他输入端的1。所以与非门结构的基本R-S触发器以输入信号的0状态为有效态,1为无效态。与非门的特性决定图4-98a的结构具有下述功能:

,

, (两个信号都有效)时,两个与非门输出都为1,为异常的不定态。显然这种情况是不允许出现的,在使用中要注意约束。

(两个信号都有效)时,两个与非门输出都为1,为异常的不定态。显然这种情况是不允许出现的,在使用中要注意约束。

(有效态)、

(有效态)、 (无效态)时,无论触发器的现态Qn为何值,次态都为0,即Qn+1=0,称为触发器置0。

(无效态)时,无论触发器的现态Qn为何值,次态都为0,即Qn+1=0,称为触发器置0。

(无效态)、

(无效态)、 (有效态)时,无论触发器的现态Qn为何值,次态都为1,Qn+1=1,称为触发器置1。

(有效态)时,无论触发器的现态Qn为何值,次态都为1,Qn+1=1,称为触发器置1。

,

, (两信号都无效)时,两个与非门相互锁定,保持触发器的原来状态,Qn+1=Qn,称为触发器的保持态。

(两信号都无效)时,两个与非门相互锁定,保持触发器的原来状态,Qn+1=Qn,称为触发器的保持态。

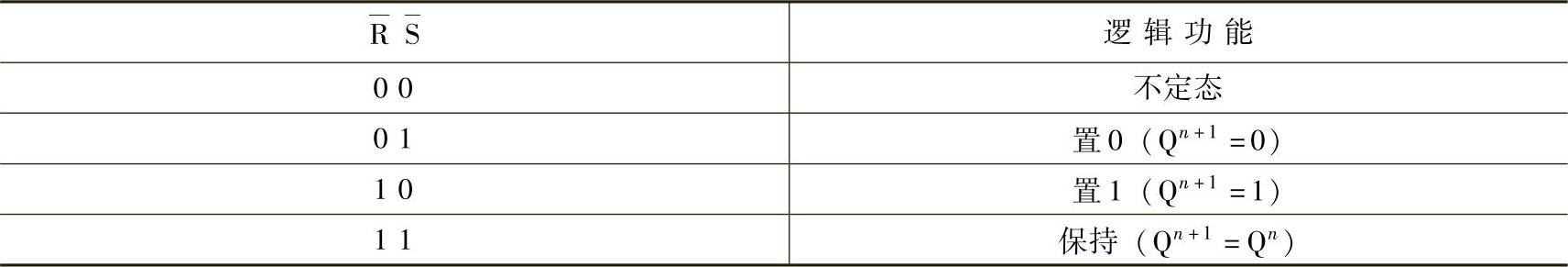

将上述归纳为与非门结构R-S触发器的逻辑功能表,见表4-39。

表4-39 与非门结构R-S触发器的逻辑功能表

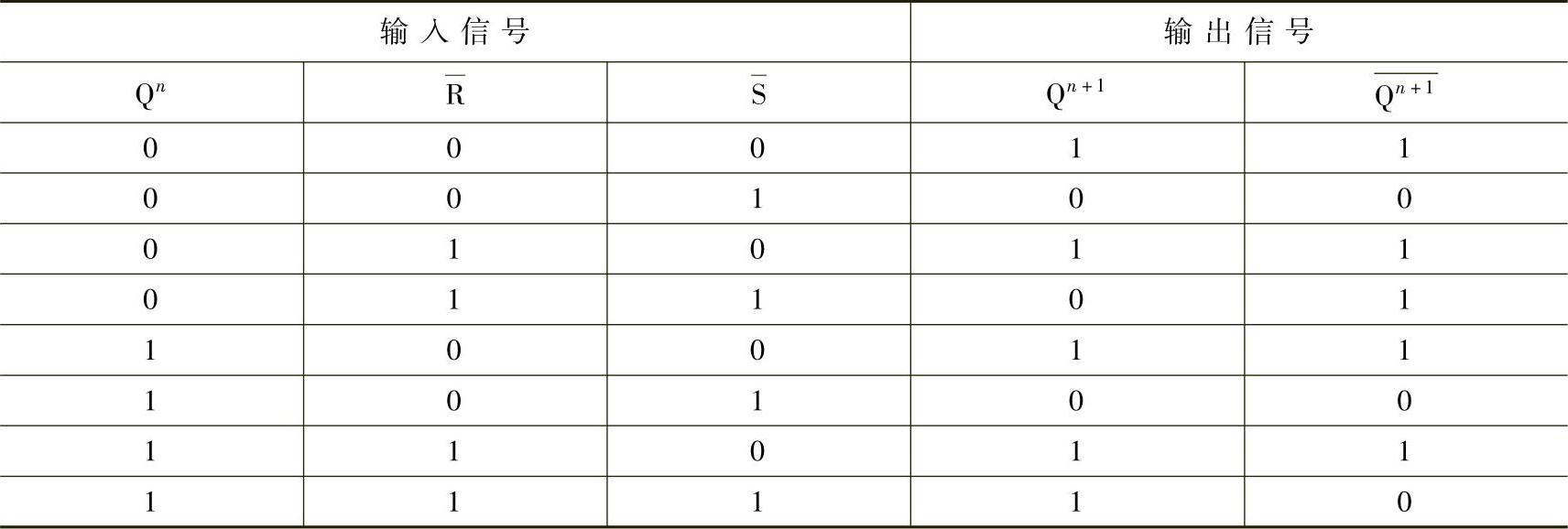

3)真值表和特性方程。利用功能表列出真值表(见表4-40)。

表4-40 输入信号为低电平有效的基本R-S触发器的全状态真值表

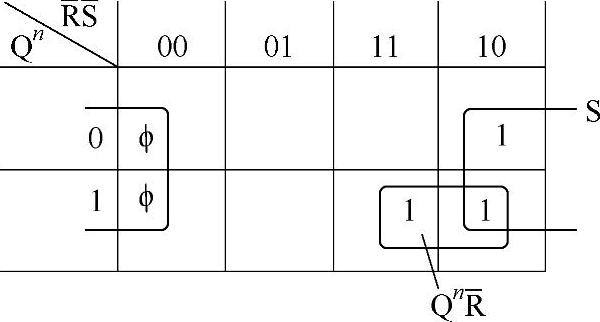

按真值表所列输入、输出状态值进行逻辑化简,如图4-99所示。真值表中有两个不允许出现的约束状态,充分利用约束项,可把表达式化到更简。

图4-99 与非结构R-S触发器的逻辑化简

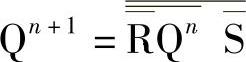

根据化简结果,得出与非门基本R-S触发器的特性方程:

应用摩根定理把上式转换为与非-与非式:

与图4-98所示与非门基本R-S触发器结构一致。

为约束 、

、 不能同时为0,要求

不能同时为0,要求 。

。

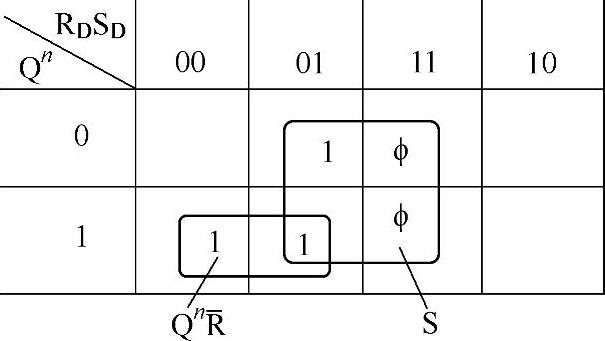

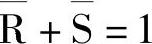

4)逻辑波形图。触发器的逻辑功能也可以用输入、输出信号的时序波形图的对应关系表示。图4-100所示为与非门基本R-S触发器的一例波形图。设触发器初态Qn=0。

5)实际产品:

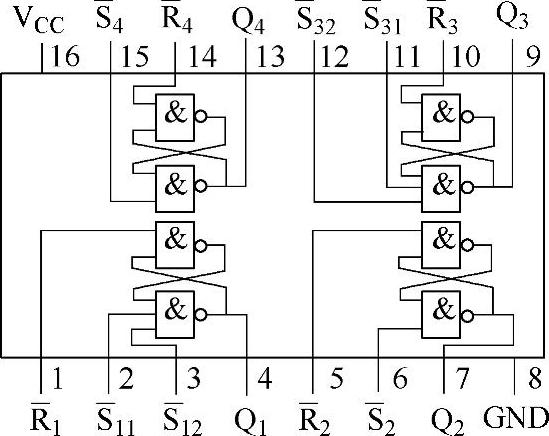

①基本R-S触发器的直接产品。基本R-S触发器的直接产品是TTL系列的74279,含4个R-S结构的锁存器,它的结构和引脚分布如图4-101所示。

图4-100 与非结构R-S触发器的波形图

图4-101 74279内部结构和引脚分布

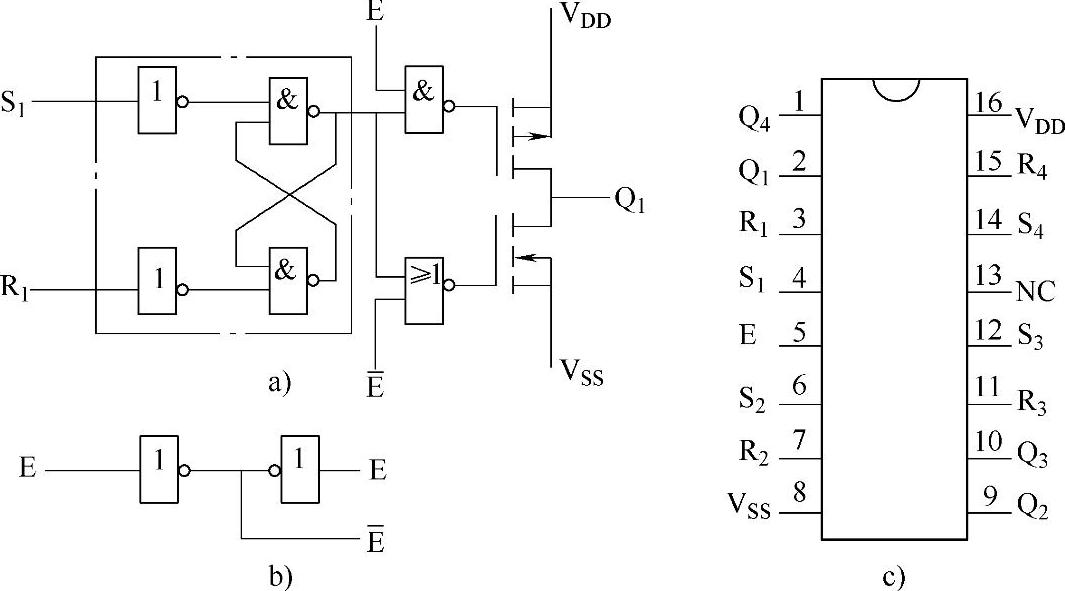

②与非门结构的基本R-S触发器产品。CC4043B是由4个与非门基本R-S触发器组成的锁存器集成电路,其内部结构如图4-102所示。(https://www.daowen.com)

图4-102 CC4043B的单元电路

CC4043B的单元触发器采用单端并经三态门(由CMOS管构成)输出,4个触发器的三态门,由芯片的⑤脚E(使能信号、允许信号)控制。

【边学边练】

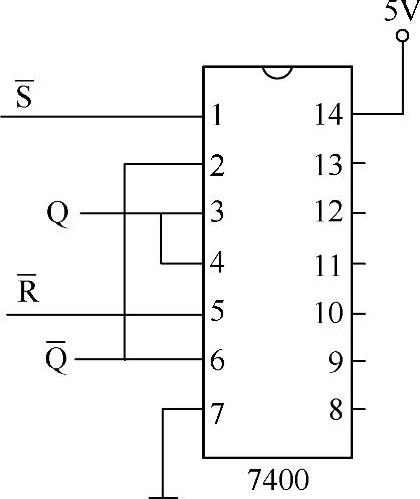

1)在数字实验板上,用一片7400按图4-103连线构成基本R-S触发器,在适当位置安排输入逻辑(也可用图4-58所示的防颤输入)和显示电路各两组,并与触发器的输入、输出端连接。

2)变换输入逻辑组合.观察输出显示灯的变化。

图4-103 基本R-S触发器测试接线图

2.同步触发器

在TTL和CMOS数字集成电路中的触发器产品,除基本R-S触发器之外,其他都是同步型的D触发器和J-K触发器。

(1)D和J-K触发器的功能构成

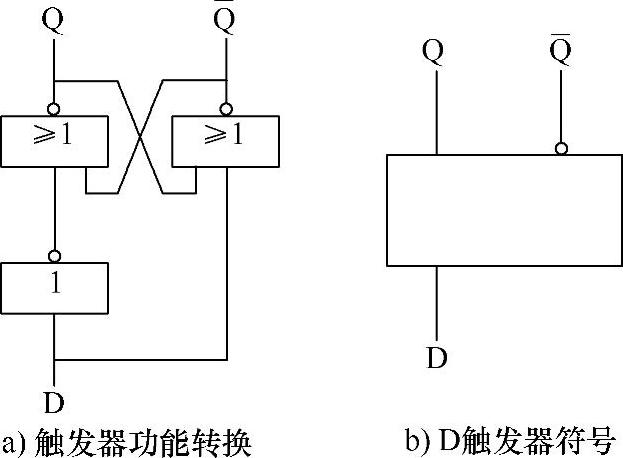

D和J-K触发器的功能由基本R-S触发器变换功能构成,通过添加功能转换逻辑实现。

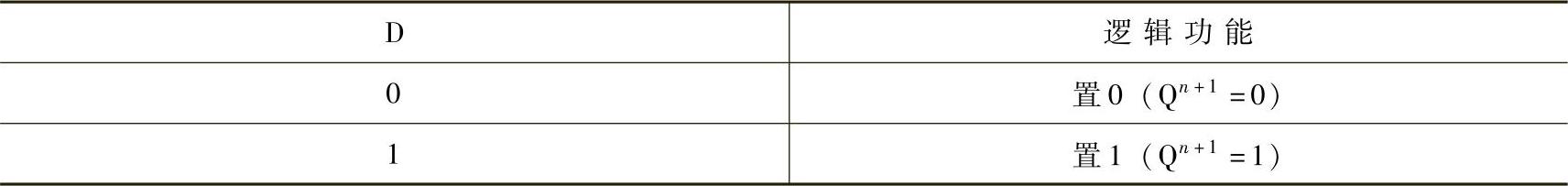

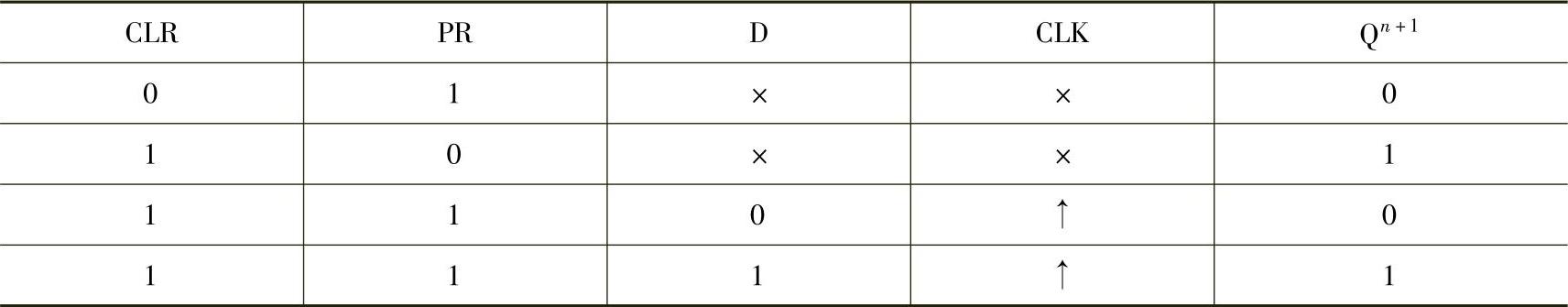

1)D触发器。D触发器的输入信号只有1个,名称为D。触发器的逻辑功能见表4-41。

表4-41 D触发器逻辑功能表

D触发器的功能简单,用基本R-S触发器添加1个非门即可实现功能转换,如图4-104a所示。

图4-104 R-S触发器转换为D触发器

图4-104b所示为D触发器图形符号。

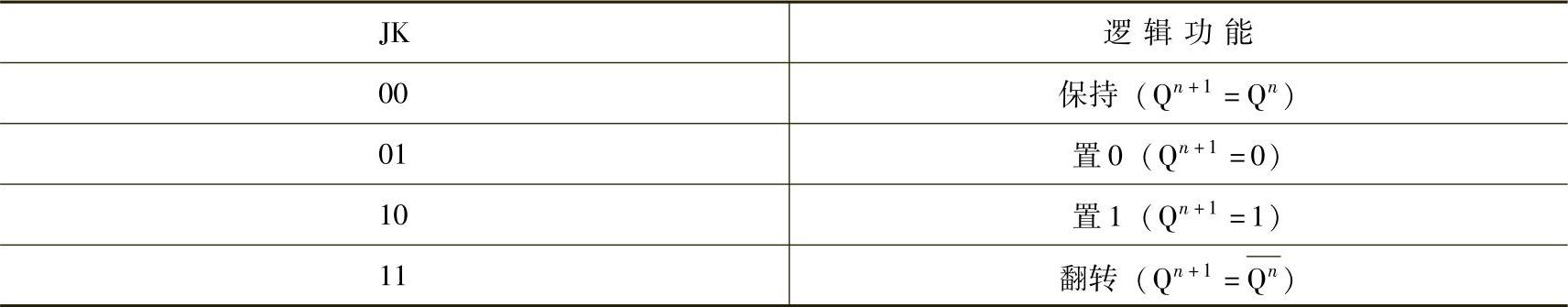

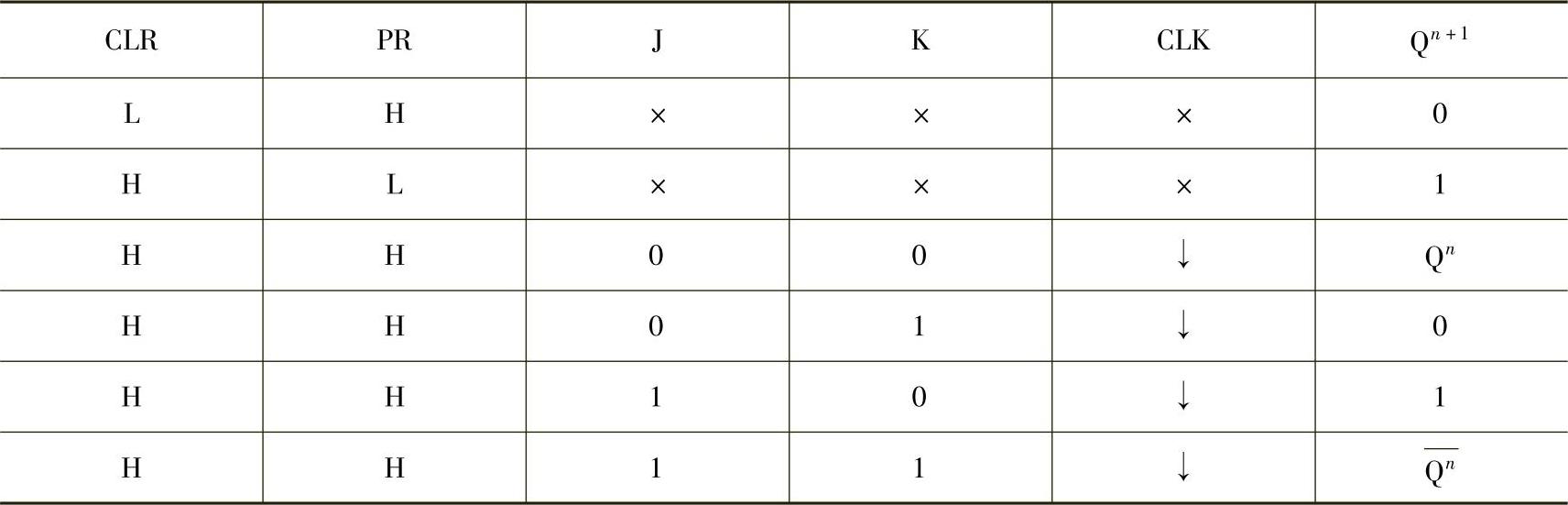

2)J-K触发器。J-K触发器是全功能型触发器,其逻辑功能见表4-42。

表4-42 J-K触发器的逻辑功能表

J-K触发器的功能可用D触发器转换实现,转换逻辑是

如图4-105所示是用与或逻辑将D触发器转换为J-K触发器。

也可用4个与非门(一片7400)制作4-6式转换逻辑,将D触发器转换为J-K触发器,读者可自己尝试。

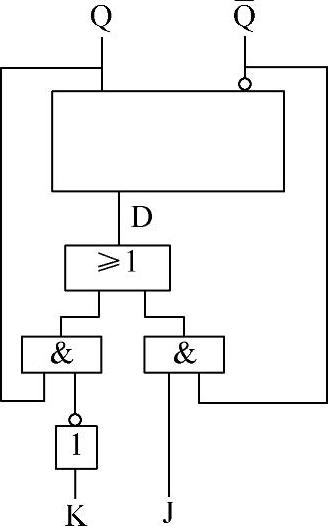

(2)添加时钟信号和清零、置位信号

1)CP信号。基本R-S触发器的输入信号直接影响输出端的状态,缺少控制功能。前面介绍的4043和4044的E信号只控制触发器对外输出,对输入信号无控制作用。实际使用需要对输入信号给予控制,为此给触发器增设一个时钟脉冲(CP),专门用于控制输入信号对输出端产生作用的时间(或时刻)。有CP信号的触发器叫做同步触发器。

图4-105 D触发器转换为J-K触发器

CP是触发器的特殊输入信号,只控制输入信号对触发器输出端产生作用的时间(或时刻),不影响触发器的逻辑功能。CP信号对触发器产生控制作用称为触发。受CP信号控制的输入信号称为同步输入信号。

实际触发器产品的CP信号常以CLK或G命名。

2)复位和置位信号。按使用需要触发器还应有复位RD(又称作清零CLR)和置位SD(又称作预置PR)信号。复位信号RD和置位信号SD应不受CP信号控制,称为直接输入信号(D脚标表示直接),RD和SD多采用低电平有效信号。

图4-106 同步D触发器结构

CP信号的引入通常是利用与门、或门、三态门的控制功能实现的,图4-106所示为同步D触发器引入 、

、 、

、 个信号的示意图,CP是三态缓冲门的使能端,控制D信号的输入。

个信号的示意图,CP是三态缓冲门的使能端,控制D信号的输入。

如图4-106所示,引入的CP信号属于电平触发,电平触发有高电平触发和低电平触发(加“○”表示)两种。电平触发(又叫脉冲触发)的触发器结构简单、价格低。但在CP信号的一次有效触发时间内,如果输入信号变化,触发器输出端也会跟着改变状态,这种变化称为空翻现象,会影响电路动作的准确性。

按理论要求,CP信号对触发器的一次有效控制,触发器只能做一个动作,称为一次触发。显然电平触发方式不够理想,若将CP触发的有效时刻设在信号电压上升或下降的过程中(称为边沿触发)可以确保一次触发效果。表示边沿触发的CP信号加标“∧”符号,无此符号为电平触发。边沿触发也分为上升沿触发(正触发)和下降沿触发(负触发,加“○”表示)两种。

边沿触发器的结构复杂,在数字集成电路中,电平触发的触发器产品较少,多数属于边沿触发或等效功能的主从触发器。

(3)同步触发器产品

时序逻辑电路按触发器的动作方式分为同步和异步两种类型。触发器动作统一的称为同步型,动作不统一的称为异步型。D和J-K触发器产品都有独立型、关联型和多输入端3种类型。其中独立型结构的触发器用于制作异步型时序电路,关联式结构用于制作同步型时序电路。

关联型D触发器和J-K触发器的产品类型很多,这里只介绍独立结构和多输入端的触发器产品。

1)独立结构的双D触发器7474和4013。TTL系列电路中的7474由两个独立结构的D触发器上升沿触发,各种信号齐备,内部结构和引脚功能如图4-107所示。

7474双D触发器的逻辑功能见表4-43。

图4-10 77474的内部结构和引脚功能

表4-43 7474的电路功能(CP为高电平触发)

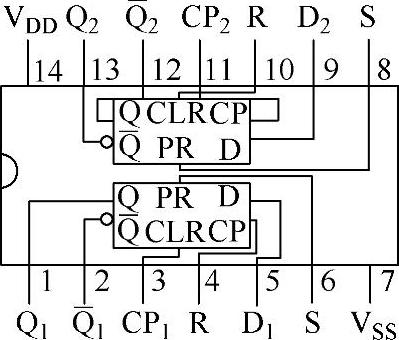

4013是CMOS系列的双D触发器(高电平触发),内部结构和引脚功能如图4-108所示。

图4-108 4013的内部结构和引脚功能

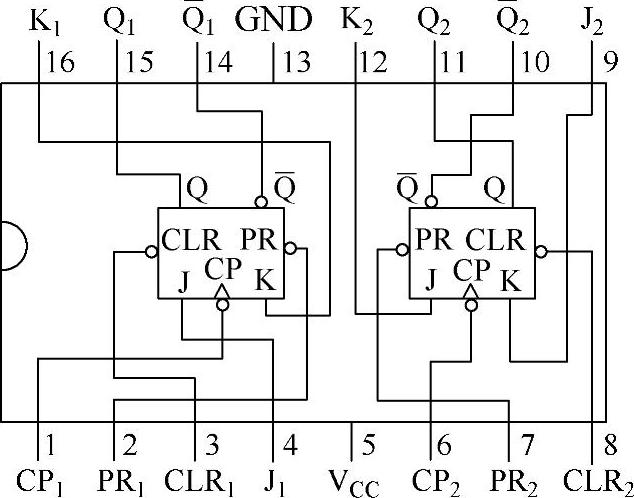

2)独立结构的双J-K触发器7476和4027。TTL系列电路中的7476是两个独立结构的下降沿触发J-K触发器,内部结构和引脚功能如图4-109所示。

图4-109 7476的内部结构和引脚功能

7476下降沿触发的双J-K触发器的逻辑功能见表4-44。

表4-44 7476J-K触发器功能表

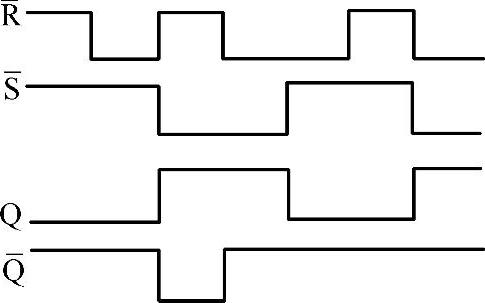

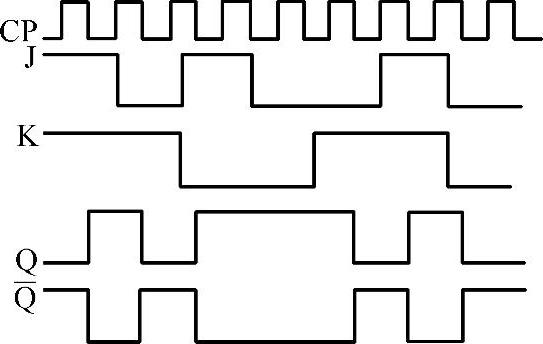

J-K触发器的波形如图4-110所示。

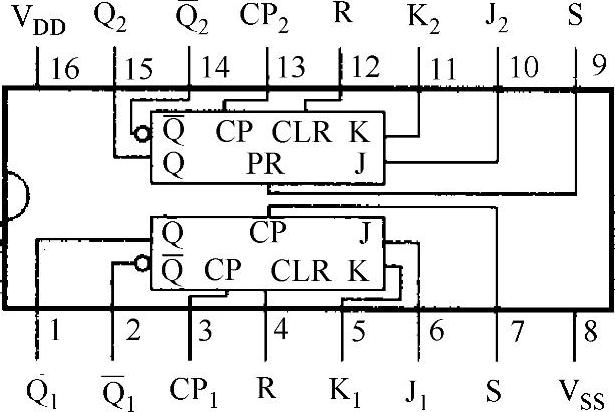

4027是CMOS系列的双J-K触发器(上升沿触发),内部结构和引脚功能如图4-111所示。

图4-110 J-K触发器的波形图

图4-111 4027双J-K触发器内部结构和引脚功能

3)多端同名输入的触发器。触发器的多个同名输入端都采用与逻辑关系输入。

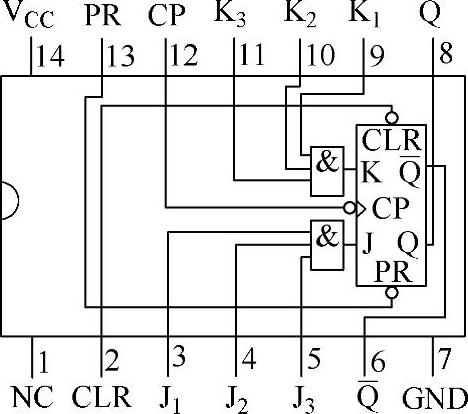

①TTL触发器74110。74110是个3输入端的J-K触发器,即J和K都有3个输入端,其内部结构和引脚功能如图4-112所示。

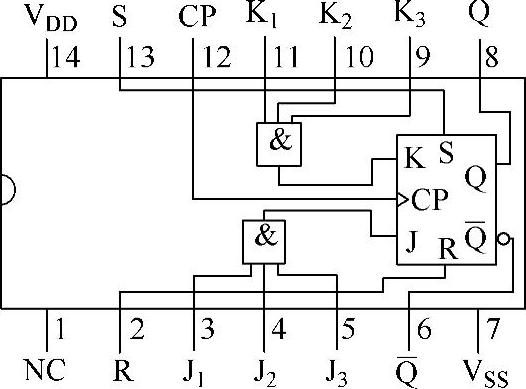

②CMOS触发器4095。4095也是个3输入端的J-K触发器,其内部结构和引脚功能如图4-113所示。

图4-112 74110的内部结构和引脚功能

图4-113 4095的内部结构和引脚功能

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。