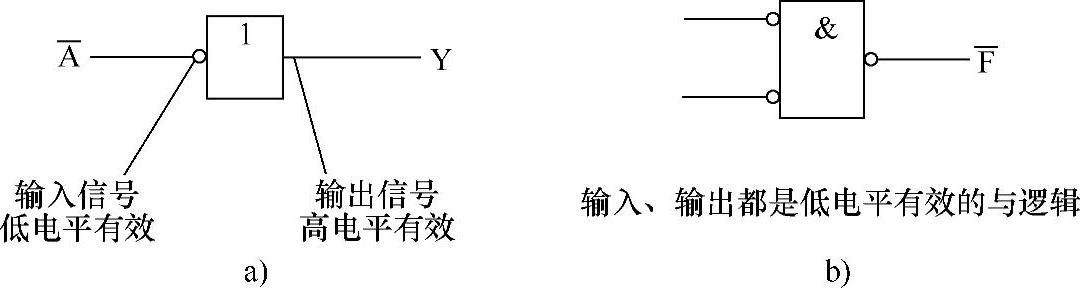

1.用负逻辑符号表示低电平有效的输入信号

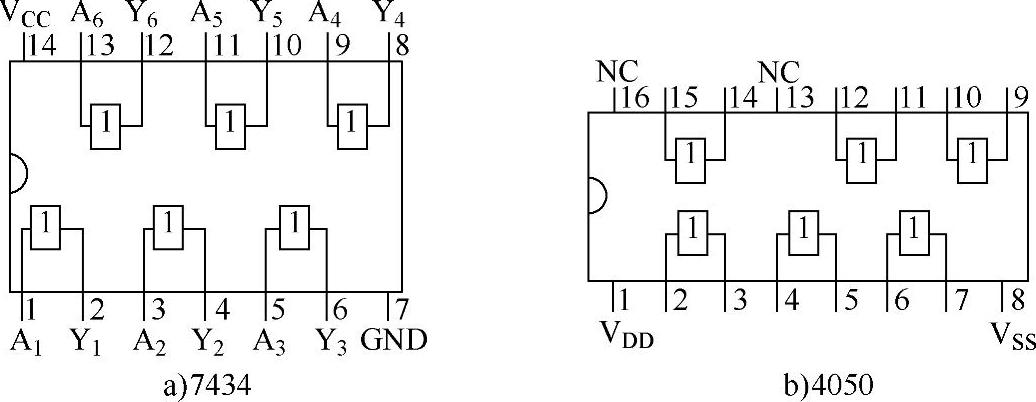

为使逻辑电路图便于阅读,常对低电平有效的信号线和信号字母给以直观标识。在输入信号线的终端、输出信号线的起始端加标一个小圆圈(非逻辑)表示该线信号是低电平有效;字母加非号表示该信号是低电平有效。无小圆圈的信号线和无非号的信号名称表示高电平有效,如图4-53所示。

图4-53 线路信号有效电平的表示方式举例

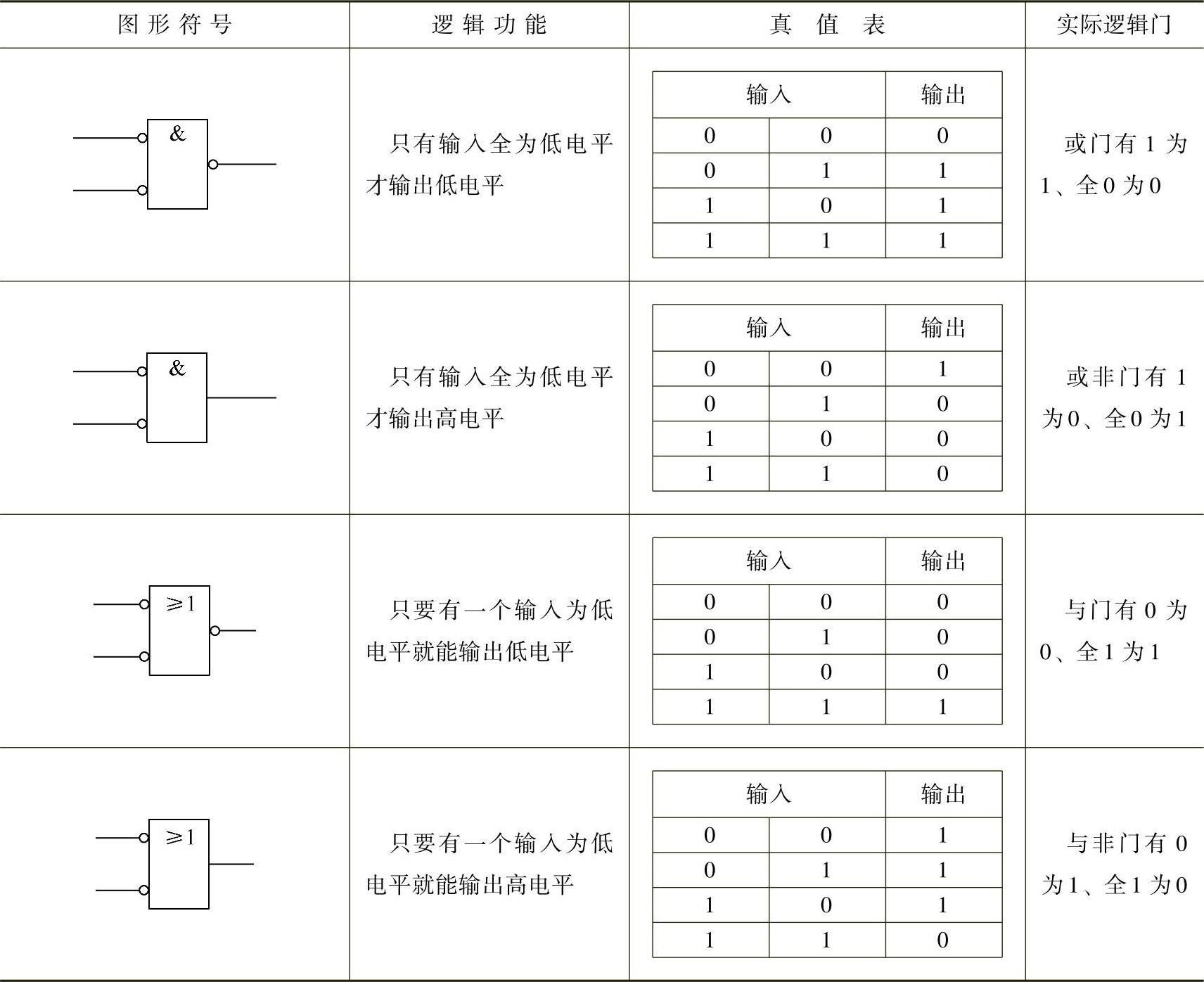

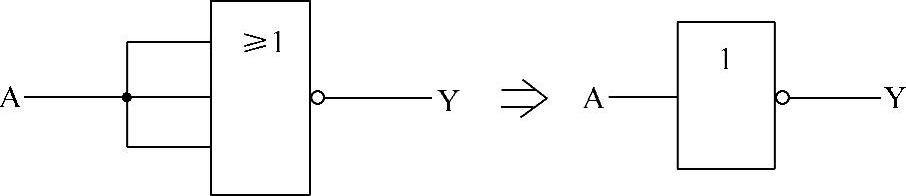

(1)将负逻辑符号转换为正逻辑符号

由于成品逻辑电路都按正逻辑命名,要确认正、负逻辑之间的对应关系,关键在于列出负逻辑的真值表,表4-26为4种实用的负逻辑符号及对应的正逻辑符号。

表4-26 4种实用的负逻辑符号及对应的正逻辑符号

(2)实例

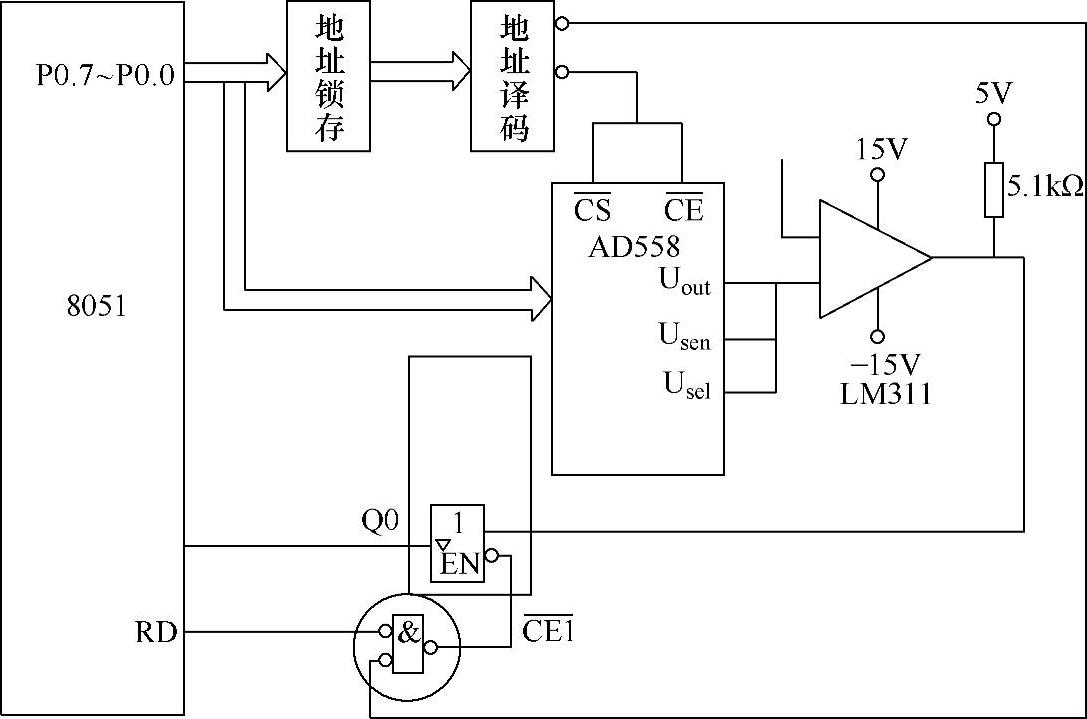

在图4-54中被圈的逻辑门就是为直观表示电路对信号有效状态和组合方式的要求而使用便于阅读的逻辑符号。

图4-54 便于阅读的逻辑符号实例

2.数字电路中的其他技术

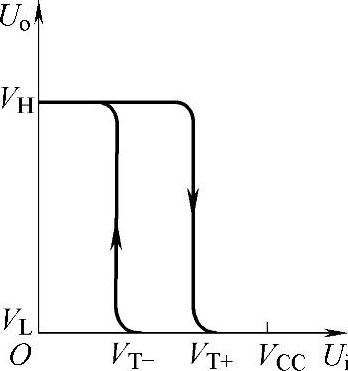

(1)使用施密特触发器对输入信号整形,提高抗干扰能力

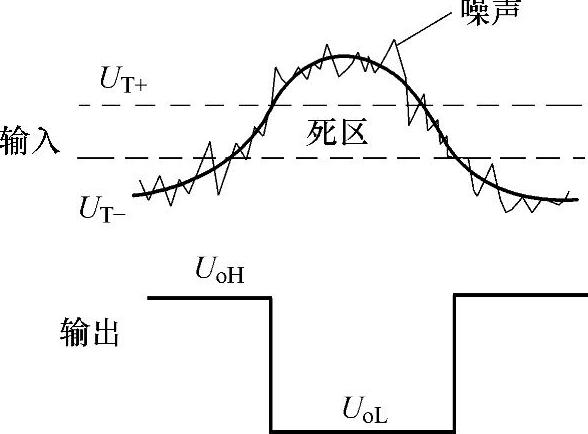

施密特触发器是一种功能特殊的电路,它的输出电压变化相对输入电压变化有明显的迟滞特性,它的电压特性曲线如图4-55所示。这个特殊电压特性曲线也是施密特触发器的专用标识。

施密特触发器特殊的电压特性使它具有很好的抗干扰性能和脉冲整形作用,其原理可用图4-56表示。

图4-55 施密特触发器的电压特性曲线

图4-56 施密特触发器的抗干扰原理

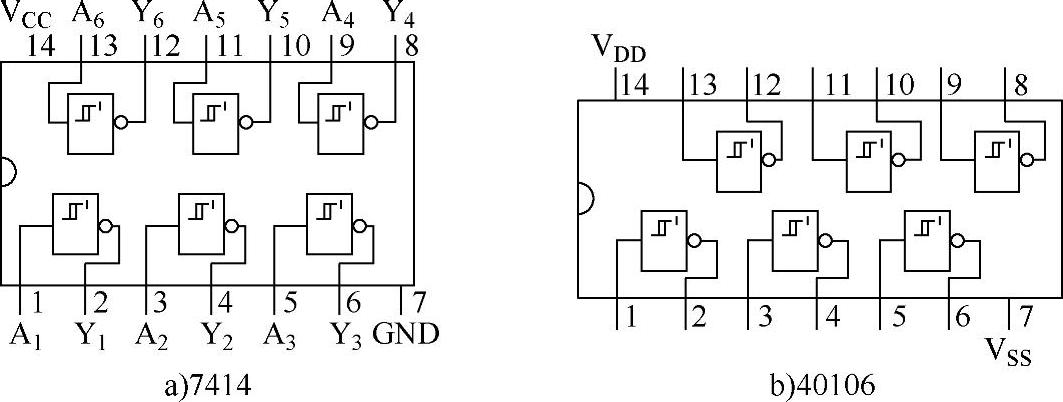

为了使一些数字集成电路产品具有良好的抗干扰和整形性能,在电路中引入施密特触发器,成为各种含有施密特触发器的逻辑电路产品,如图4-57所示。

图4-57 两个含施密特结构的六反相器

利用施密特触发器的抗干扰特性消除手动开关的颤动:本章第四、五节介绍的电路,要求输入信号要干净、准确,手动开关的颤动必须消除,简单实用的防颤电路可用7414(或7419、40106等)六施密特反相器,1片7414可构成6路防颤输入,如图4-58所示。

图4-58 具有防颤功能的逻辑输入装置

(2)传输门和缓冲门、驱动门

传输门没有逻辑转换功能,输出与输入同相。

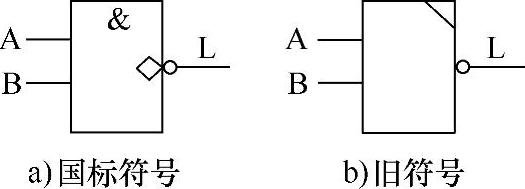

用于调节两级电路之间的电流匹配问题,能增加信号在电路中的传输时间的传输门又叫缓冲门。有较大输出功率,用于驱动负载的传输门叫驱动门,驱动门与模拟电路的射极输出器相似,输入电阻较大、输出电阻小,带载能力较强。两种性能兼备的合称为缓冲驱动门,如图4-59所示的7434和4050是缓冲驱动门的典型产品。

非逻辑的图形符号就是传输门的输出端加小圆圈(图形的非号)构成的。

(3)集电极开路的逻辑门(OC门)

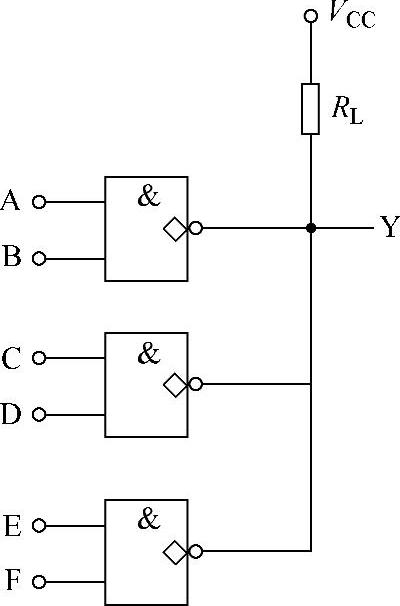

集电极开路的逻辑门又叫OC门,图4-60所示为OC与非门符号。

图4-59 7434和4050缓冲器

图4-60 OC与非门符号

电路内部的输出级晶体管的集电极不接电阻和电源,使用时输出端要由外部补接集电极电阻(通常叫上拉电阻)和电源。这样就为各类数字电路之间的电平转换、高压电源使用和直接驱动发光二极管(LED)提供了方便。在74系列中备有大量含OC结构的成品逻辑电路。

使用OC门还能实现“线与”(即通过连线实现与逻辑功能)关系简化电路,如图4-61所示。

3个OC门只要有一个输出低电平,输出端Y即低电平,只有当OC门都输出高电平时,线路才能呈高电平状态。电路的逻辑关系为

Y=(A+B)(C+D)(E+F)

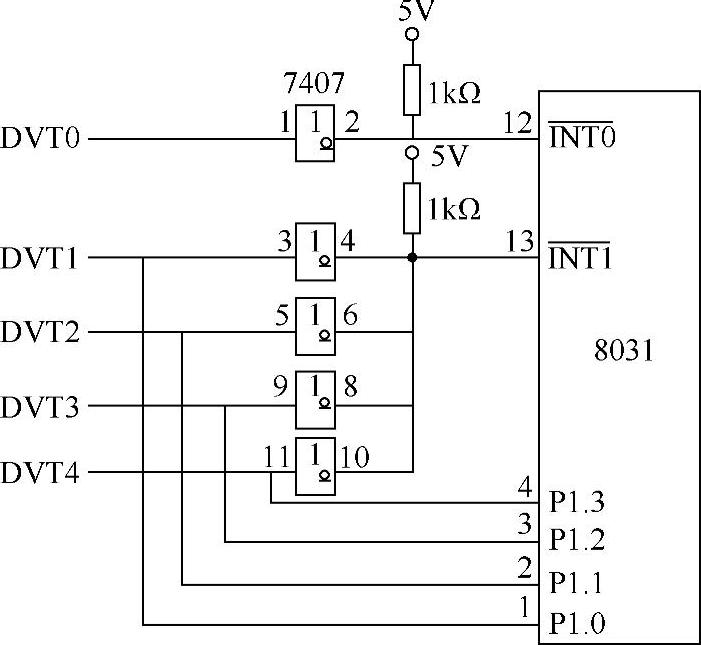

图4-62所示为OC驱动门(7407)的“线与”应用实例。

图4-61 用OC门构成的线与逻辑

图4-62 8031扩展多个外中断源

7407的驱动门在电路中起隔离和同相传输作用,接在8031单片机INT1信号输入端(13脚)的4个驱动门由线路连接方式构成“线与”(即这样接线具有与逻辑功能),为8031的INT1端扩展了多个外中断源。

(4)三态门

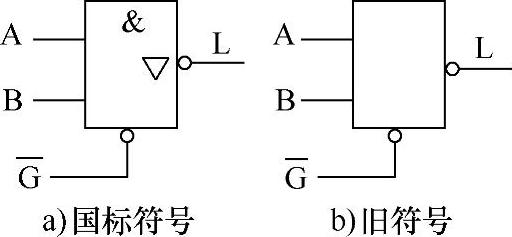

三态门是一种设有控制端的逻辑门,图4-63所示为三态与非门符号。

图4-63 三态与非门符号

控制端信号(常用G或EN表示,通常称为使能信号)有效时三态门按正常的逻辑门功能可输出0态和1态;当控制端信号为无效时,三态门的输出端与输入端之间呈高阻态(即呈近似断路状态)。三态门在数字电路中主要用于控制线路实现分时使用。

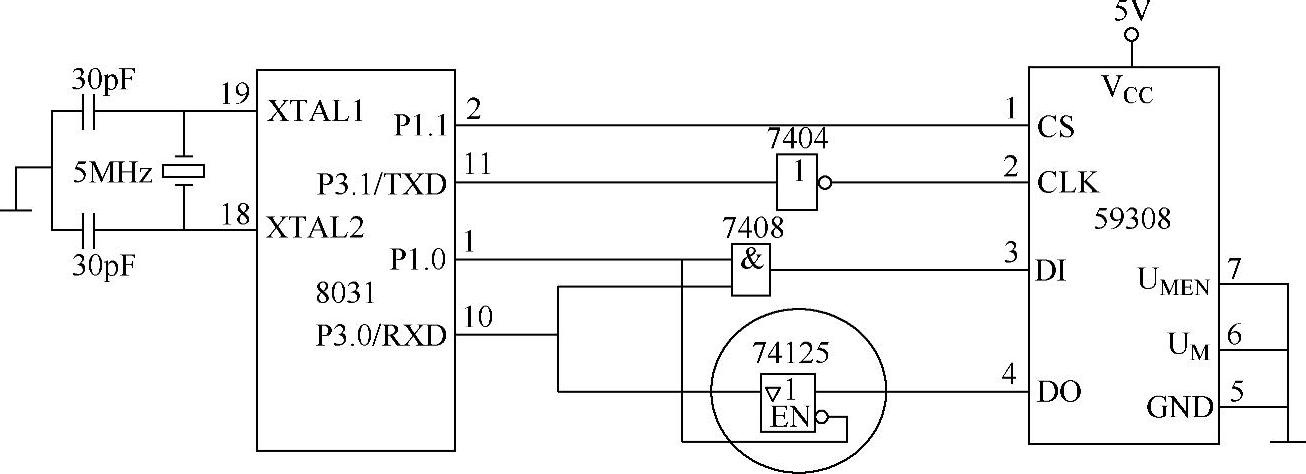

图4-64所示是一个为单片机8031扩展串行E2PROM(电可擦除可编程只读存储器59308)电路,其中含有三态传输门的应用。

电路中8031由P1.1输出高电平直送59308的CS(片选信号)输入端,用串行口的发送端(TXD)为E2PROM芯片59308发送时钟信号(CLK),为满足59308的时序要求信号需经非门(7404)倒相。8031的串行输出、输入都由P3.0(RXD)端执行,用与门(7408)和三态门(74125)进行串行数据的可控收、发,P1.0作收发控制端。P1.0=0时,与门被封锁、三态门打开、8031接收59308 DO(数据输出端)发出的数据;P1.0=1时,与门打开、三态门为高阻态、8031发送数据到59308的DI(数据输入端)。

图4-64 8031扩展串行E2PROM的电路

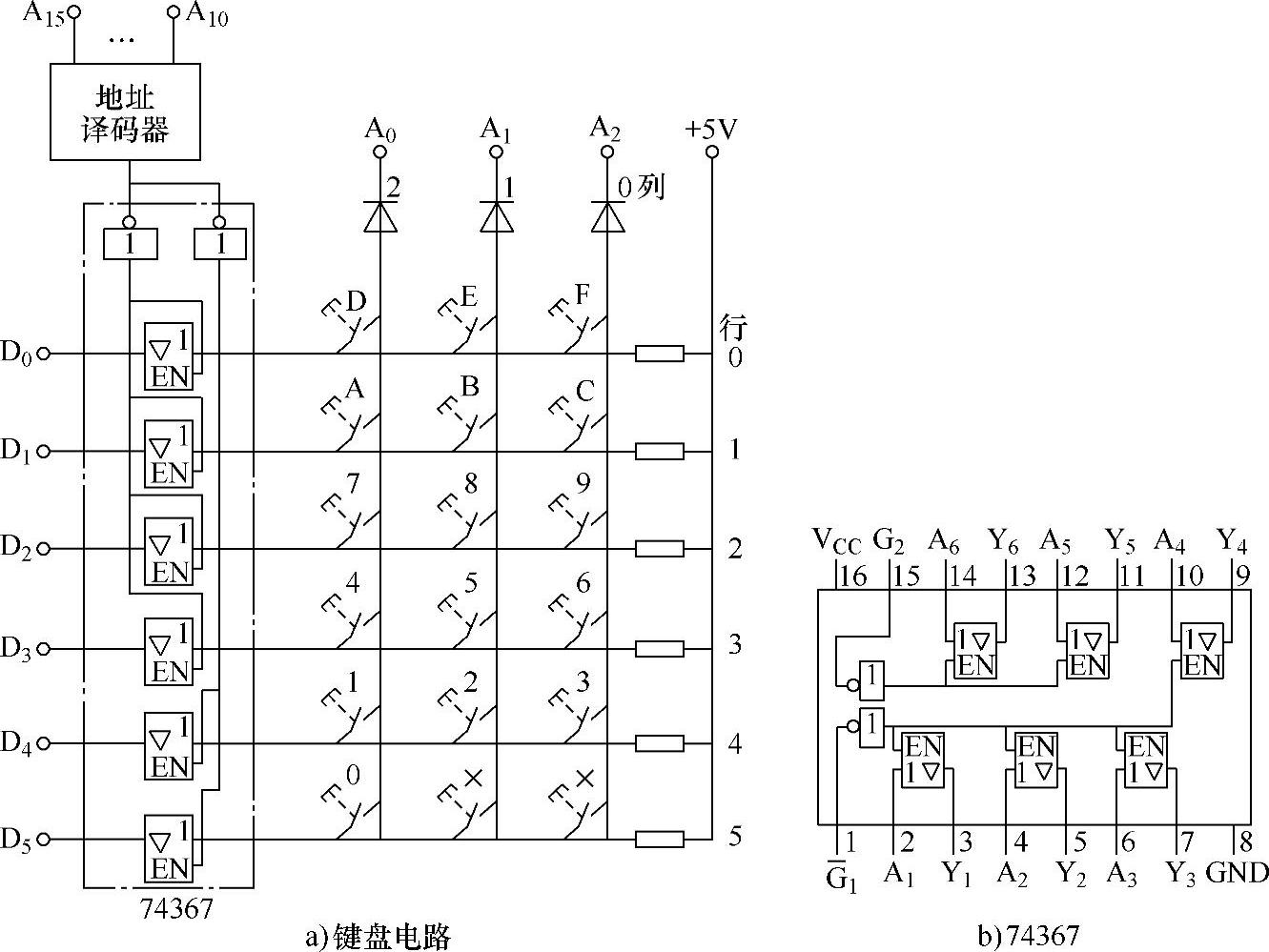

图4-65所示电路是用三态门电路74367为接口的键盘电路以及74367集成电路引脚分布。

图4-65 以74367为接口的键盘电路和74367集成电路

74367为三态六同相传输门,三态门的控制信号由地址译码器提供(低电平有效)。当把这个键盘的地址(设计时分配给这个键盘的地址)送入地址译码器时,74367从译码器得到低电平,开启传输门,把键盘操作的6位数据送到数据总线上。

74367集成电路为16引脚的双列直插封装的电路,除电源和地线外,有6个输入信号、6个输出信号,同相传输。6个传输门同时使用,三态门的控制信号取自译码器的同一输出端,有效电平都是低电平,可直接连接,不用插入逻辑转换。

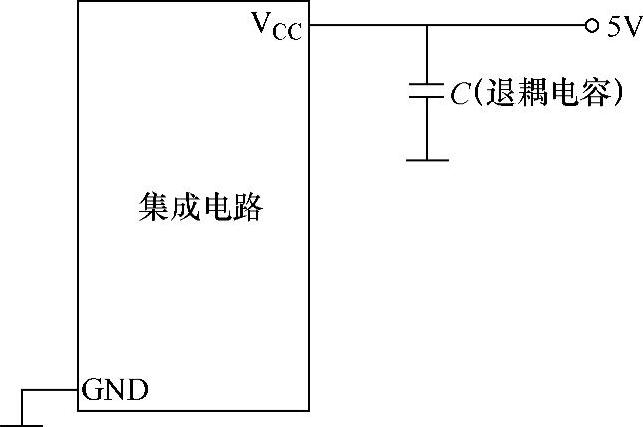

(5)退耦电路(https://www.daowen.com)

实用电源都有一定的内阻,在多单元电路中,电源内阻是造成各电路单元相互影响的串扰信号源。退耦电路是针对这类信号串扰而设置的。在数字电路(尤其是计算机电路)中,由于线路上的信号频率高,消除高频串扰是不可忽视的,常用办法是在集成电路的供电线路上挂接一个适当容量的电容,如图4-66所示。

3.逻辑门变换功能使用

(1)把与非门(或非门)作非门使用

数字电路中的与非门(或非门)产品,都是一个芯片内封装多个逻辑门,为充分利用资源、降低成本,可将剩余与非门的输入端连在一起,作一个输入端使用,与非门就变成非门,如图4-67所示,对或非门也可这样使用。

图4-66 数字电路中常用的退耦方式

图4-67 或非门作非门使用

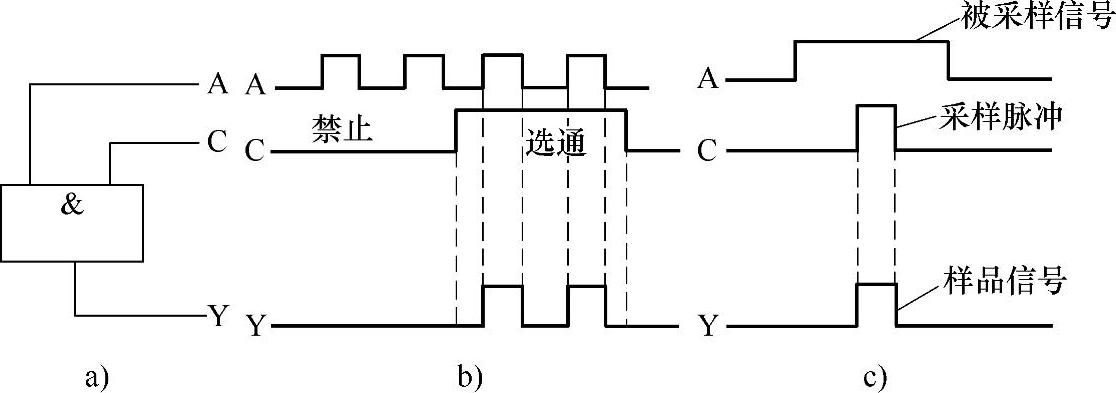

(2)把逻辑门作控制门使用

把逻辑门的一个输入信号作为控制信号,另一个作为被控制信号的使用方式在组合电路中是常见的。

1)与门。

由与逻辑的运算法则

A∩0=0

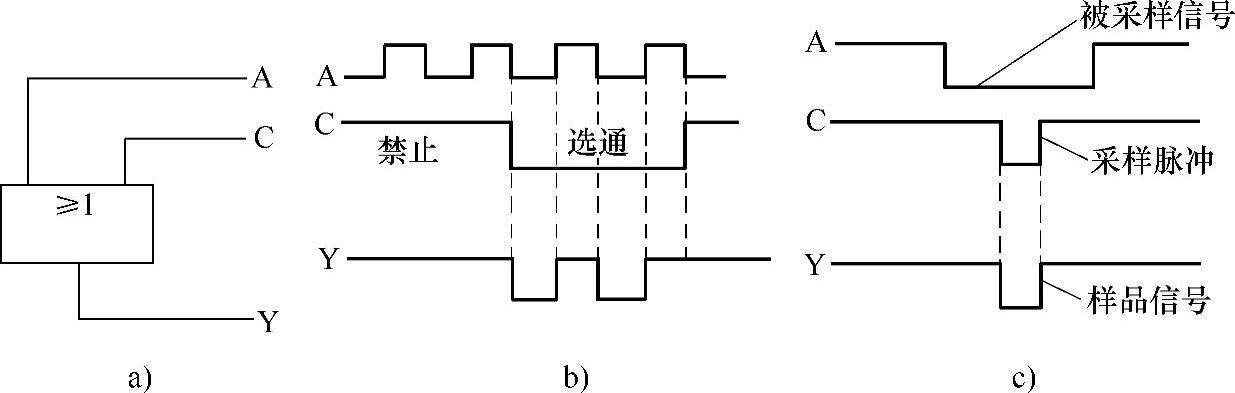

A∩1=A可以看出,一个输入端的0可以屏蔽其他输入端信号。即与门的一个输入端的0可以禁止另输入端1信号的通过,而这个输入端的1可以对另一输入端1信号进行采样或选通控制(采样或选通后的信号若需倒相,可用与非门)。与门的选通/禁止和采样功能如图4-68所示。

图4-68 与门作控制门使用

2)或门。

由或逻辑的运算法则

A+1=1

A+0=A

说明,或门的一个输入端的1可以屏蔽其他输入端信号,0使门打开。即或门的一个输入端的1可以禁止另一个输入端0信号的通过,而这个输入端的0可以对另一个输入端0信号给予采样或选通控制(采样或选通后的信号若需倒相,可用或非门)。或门的选通/禁止和采样功能如图4-69所示。

图4-69 或门作控制门使用

数据选择器和分配器是与门、或门的控制功能的实际应用。

用N位数字信号的二进制译码器可以生成2N个独立信号控制数据分配,也可以在2N个信号中进行选择,这就是数据分配器和数据选择器的结构原理。

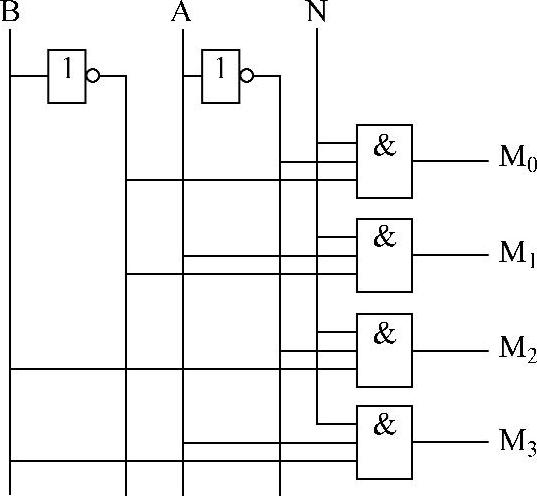

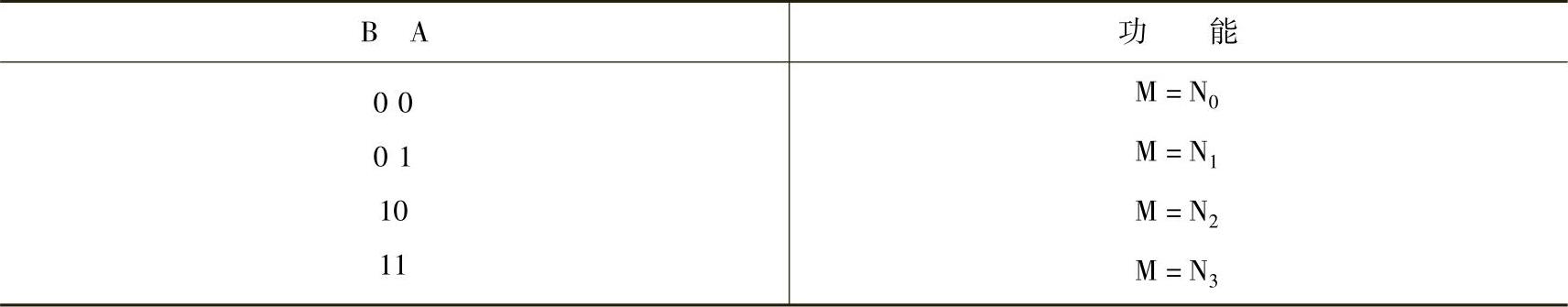

图4-70所示为一个输入信号、4个输出信号的四端数据分配器,B、A为两个分配控制信号。

从电路结构可以看出它的结构是个2-4译码器,再配合与门的禁止/选通控制功能,A、B两信号的4种状态组合分别开启4个与门,它的功能表见表4-27。

图4-70 四输出端数据分配器

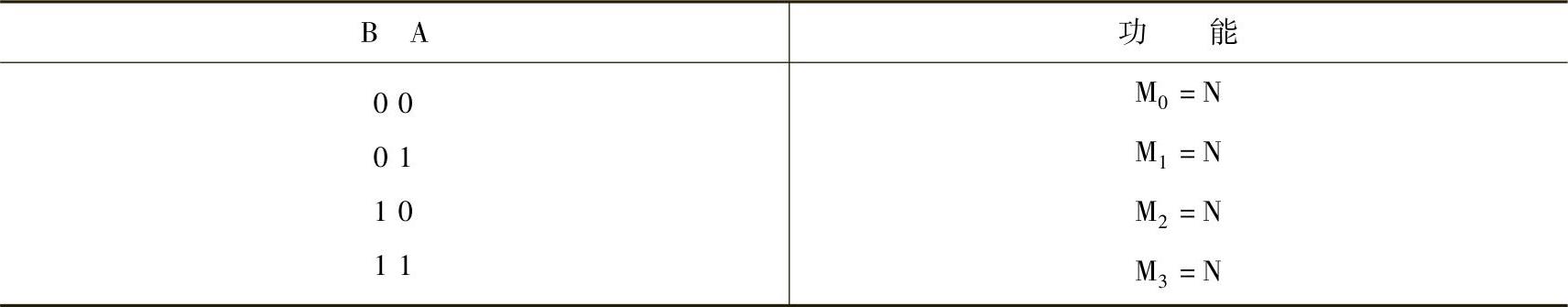

表4-27 数据分配器功能真值表

如果在分配器的输出端配置CMOS的传输门,还可以用于模拟信号的分配。

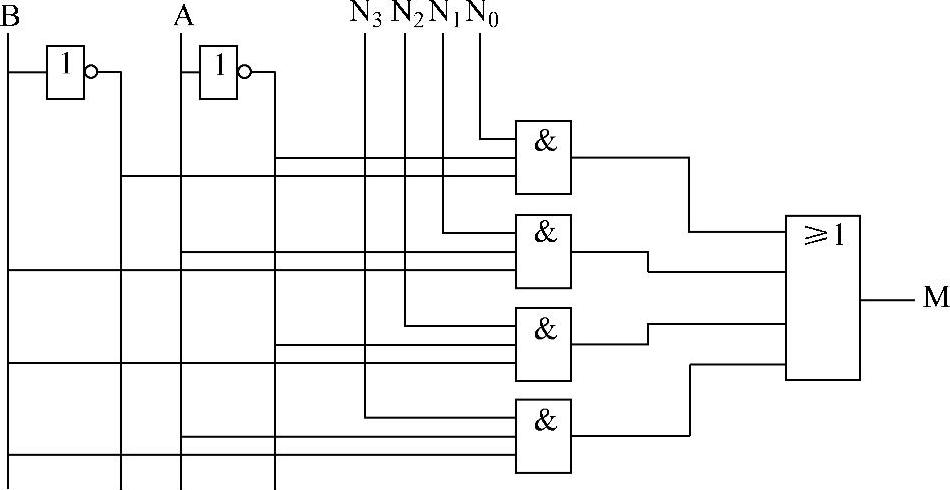

按照分配器的原理,还可以在译码器的基础上构制出数据选择器。图4-71所示为一个四选一的数据选择器,B、A为两个选择控制信号。

图4-71 四选一数据选择器

电路利用2-4译码器控制对信号的选择,又使用或门将4路信号汇合到输出电路中。它的功能真值表见表4-28。

表4-28 数据选择器功能真值表

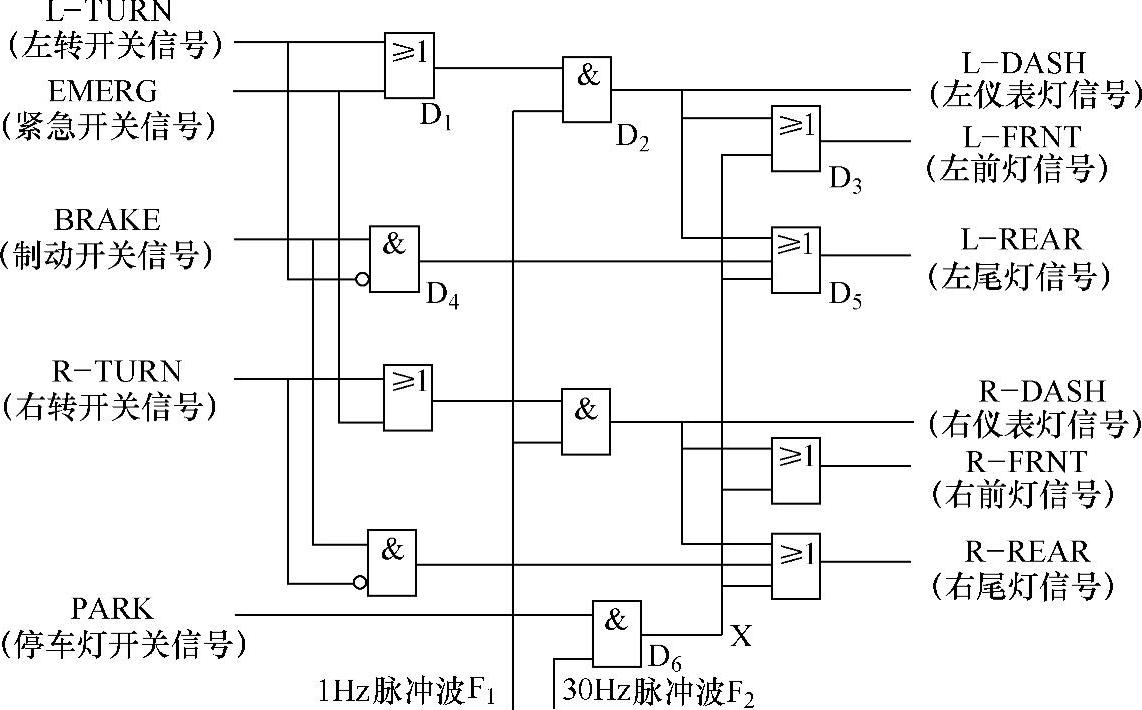

图4-72所示为控制汽车灯的组合逻辑电路也是与、或两种逻辑门的使用实例。

图4-72 车灯控制组合逻辑电路

电路中有7个输入信号,其中F1信号的频率为1Hz,使灯成闪动状态;F2信号的频率为30Hz,用于降低车灯亮度。

左、右两路信号灯控制电路的结构及原理相同,图中只对一路逻辑器件标有序号。

此电路控制汽车的转向、制动、停车和紧急4种状况的信号灯动作,电路中有7个输入信号,F1转向和紧急频闪信号,频率为1Hz;F2为停车频闪信号,频率为30Hz,其他控制信号都是高电平有效。

①制动状态:制动信号有效(此时转向信号为低电平),通过左右两路的D4与门、D5或门输出高电平,制动时左、右尾灯要同时亮,无闪动。

②左转向状态:紧急开关信号为0、左转开关信号为1,D1或门输出1,D2与门打开,输出F1转向频闪信号,通过D3、D5两个或门控制左侧前、后转向灯及仪表灯低频闪光。

③紧急状态:紧急开关信号为1,左、右两路转向灯及仪表灯同时低频闪亮。

④停车状态:停车信号平时为0,停车时为1,打开D6与门,F2信号经4个或门使所有转向灯高频闪亮,以警示其他车辆和行人。

6个输出信号的逻辑关系是:

设:X=PARK∩F2

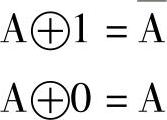

3)异或门。

按照异或逻辑的运算法则有

1使异或门变为倒相门,0使异或门变为同相门。图4-73所示为异或门换相波形。

图4-73 异或门换相波形

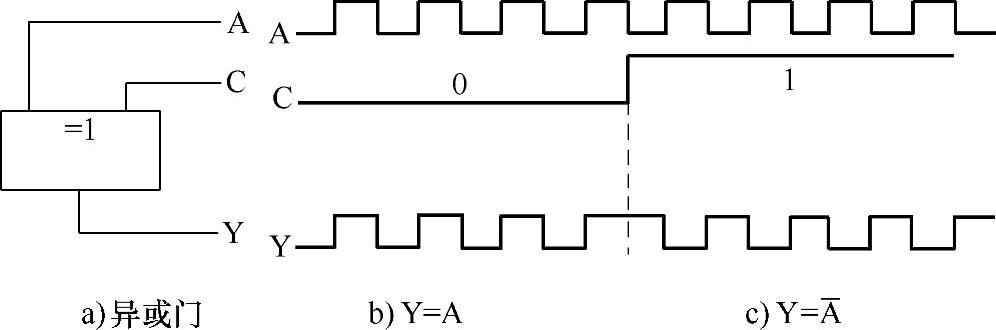

图4-74所示为7486典型应用实例。

7486的A、B两个异或门用一个输入端接地,使异或门转换为同相传输门,传输亮度信号(INTENSITY)和视频信号(VIDEO);C、D两个异或门用一个输入端经隔离电阻接电源,还有电容滤除干扰)使异或门转换为反相传输门,传输并倒相水平同步信号(HORIZOTAL)和垂直同步信号(VERTICAL)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。