PIC一般使用BiCMOS或BCD工艺。高性能BiCMOS电路于20世纪80年代初提出并实现,主要用于高速静态存储器、高速门阵列器件以及其他高速数字电路,还可用于含有数/模混合电路的系统集成芯片制造及系统集成。BCD是一种先进的单片集成工艺技术,1986年由意法半导体(ST)公司率先研制成功,这种技术能够将双极型晶体管CMOS和DMOS制作在同一芯片上,故称为BCD工艺。目前已成为PIC制作的主流工艺技术。

1.BiCMOS工艺

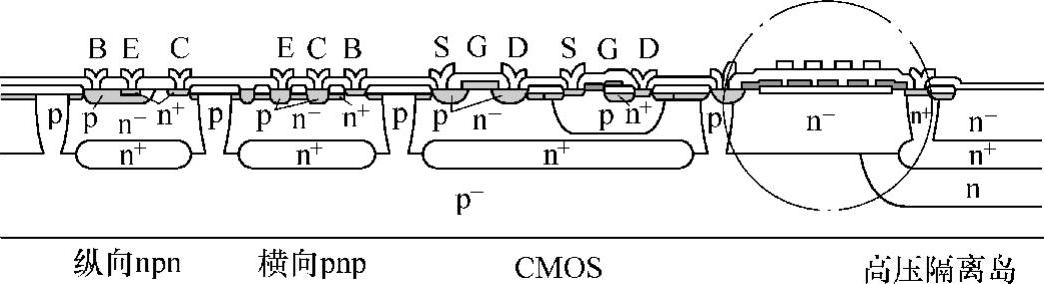

采用高、低压兼容工艺的600V Bi CMOS芯片纵向结构剖面如图8-21所示。先在p型衬底上注入砷作为n埋层,然后再生长n型外延层,并通过硼扩散形成隔离区,将纵向npn晶体管、横向pnp晶体管、CMOS及高压LDMOS分别做在不同的隔离岛内n外延层上,以实现高低压相容。其中高压LDMOS采用双埋层结构实现高压隔离。

在智能功率集成电路(SPIC)中,为了节约芯片面积,将内部LDMOS元胞用VDMOS元胞替换[32],可以实现1kV的击穿电压和0.34Ω·cm2的特征导通电阻,同时也能简化工艺,使SPIC具有更好的性能和更低的成本。

图8-21 高、低压兼容工艺的600V Bi CMOS芯片纵向结构剖面示意图

2.BCD工艺(www.daowen.com)

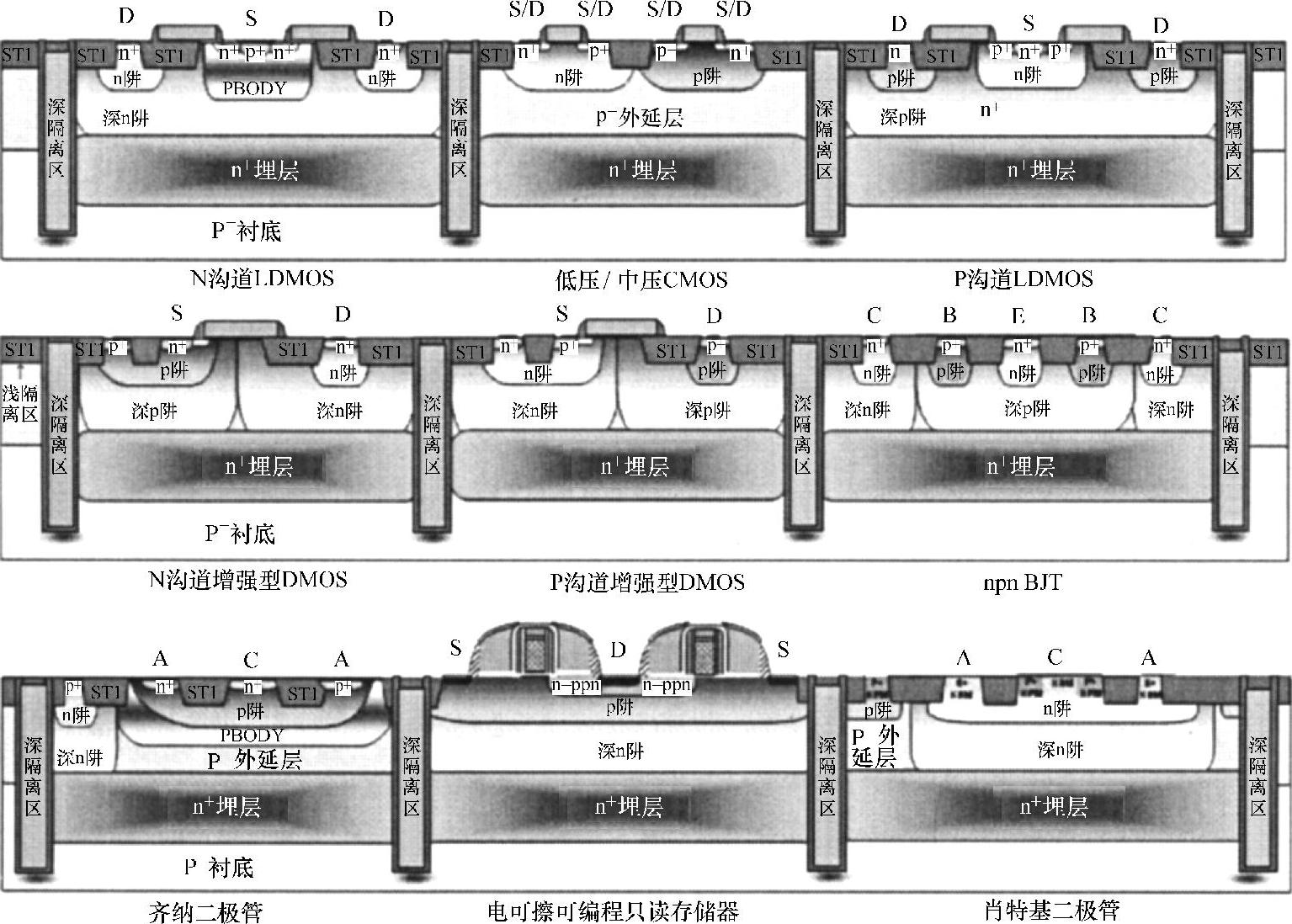

采用BCD工艺可将双极模拟电路、CMOS逻辑电路和高压DMOS器件集成在同一块芯片上。典型BCD工艺可制作低压CMOS管、高压MOS管、各种击穿电压的LDMOS、纵向npn与pnp晶体管、横向pnp晶体管、阱电阻、多晶电阻及金属电阻等元器件;有些工艺甚至还集成了电可擦可编程只读存储器(Electrically E-rasable Programmable Read-Only Memory,EEPROM)、齐纳二极管(Zener Di-ode)、肖特基二极管(Schttky Diode)等器件,如图8-22所示[33]。由于集成了如此丰富的器件,这给电路设计者带来极大的灵活性,可根据应用需要来选择最合适的器件,从而提高整个电路的性能。

由于BCD工艺包含的器件种类多,必须做到高压器件和低压器件兼容,双极工艺和CMOS工艺兼容,尤其是要选择合适的隔离技术。考虑到器件各区的特殊要求,为了减少实际光刻次数,降低制造成本,应尽量使同种掺杂能兼容进行。所以,需要采用精确的工艺仿真和巧妙的工艺设计,有时可能要在性能与工艺兼容性之间作折中选择。BCD通常采用双阱工艺,有时会用三阱甚至四阱工艺来制作不同击穿电压的高压器件。

目前,BCD工艺向高压、大功率、高密度三个方向分化发展。高压BCD工艺主要用于制作如300V以上的高压照明LED驱动、半桥/全桥驱动及AC/DC电源转换等高耐压但工作电流要求不大的器件。多采用外延工艺、pn结隔离和RESURFLDMOS结构,以提高器件的耐压。大功率BCD工艺主要用于大电流、中等电压(40~90V)控制电路的应用,如汽车电子等。重点是如何降低控制电路的成本和DMOS的导通损耗,并提高其可靠性。高集成度BCD工艺则主要用于需要与CMOS非挥发性存储电路工艺兼容的领域,电压范围是5~50V。目前的发展重点是100V以下的BCD工艺,应用领域最为广泛,趋势是线宽更小,功耗更低及更智能化。

图8-22 0.18μm BCD工艺集成的器件剖面示意图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。