1)基本RS触发器的结构及原理

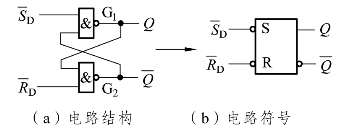

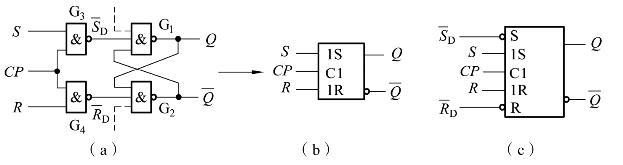

基本RS触发器是构成各种双稳态触发器的基础,其电路结构如图4.1.1(a)所示,图4.1.1(b)是其电路符号。双稳态触发器都有两个互补输出端Q(原端输出)和 (反端输出),并定义当Q=1,

(反端输出),并定义当Q=1, =0时为触发器处于置位(1)状态;当Q=0,

=0时为触发器处于置位(1)状态;当Q=0, =1时为触发器处于复位(0)状态。双稳态触发器有两个输入端:

=1时为触发器处于复位(0)状态。双稳态触发器有两个输入端: (Set)称为置位输入端,

(Set)称为置位输入端, (Reset)称为复位输入端。其下标D(Direct)表示该信号不受时钟的控制,可以直接导致触发器动作,其上划线表示低电有效。下面分析它的工作原理。

(Reset)称为复位输入端。其下标D(Direct)表示该信号不受时钟的控制,可以直接导致触发器动作,其上划线表示低电有效。下面分析它的工作原理。

当 =0,

=0, =1时,即复位输入端有效而置位输入端无效时,触发器被复位,处于0状态。当RD=1,

=1时,即复位输入端有效而置位输入端无效时,触发器被复位,处于0状态。当RD=1, =0时,即复位输入端无效而置位输入端有效时,触发器被置位,处于1状态。当

=0时,即复位输入端无效而置位输入端有效时,触发器被置位,处于1状态。当 =

= =1时,即复位输入端和置位输入端均无效时,因为信号1对于G1门和G2门是开放的,G1门的输出取决于G2门反馈过来的信号,G2门的输出取决于G1门反馈过来的信号,而这两个反馈信号就是触发器原来的状态,所以触发器保持初始状态不变。当

=1时,即复位输入端和置位输入端均无效时,因为信号1对于G1门和G2门是开放的,G1门的输出取决于G2门反馈过来的信号,G2门的输出取决于G1门反馈过来的信号,而这两个反馈信号就是触发器原来的状态,所以触发器保持初始状态不变。当 =

= =0时,即复位输入端和置位输入端同时有效时,触发器的输出端将出现Q=

=0时,即复位输入端和置位输入端同时有效时,触发器的输出端将出现Q= =1的情况,这与双稳态触发器的定义冲突,因此应禁止输入

=1的情况,这与双稳态触发器的定义冲突,因此应禁止输入 =

= =0。

=0。

用两个或非门也能构成基本RS触发器,这样的基本RS触发器的复位输入端和置位输入端变成高电平有效。

综上所述,不管是与非门还是或非门构成基本RS触发器,其共同特点是:有一对互补信号输出,复位端有效将触发器复位,置位端有效将触发器置位,复位端和置位端均无效触发器不响应,复位端和置位端均有效不允许。因此在观察触发器电路图时首先应确定触发信号是高电平有效还是低电平有效。另外,触发信号只需维持到触发器获得稳定输出后就可以撤销(输入端为高阻状态),此后触发器依赖自身的输出信号反馈回来使自己的状态维持不变。这就是触发器的存储原理。

2)触发器逻辑功能的表示方法

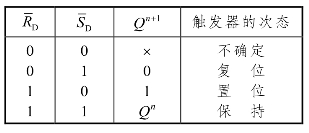

(1)特性表。表4.1.1所示是基本RS触发器的特性表。表中Qn表示信号输入前触发器的状态,称为初态。Qn+1表示信号输入后触发器的状态,称为次态。

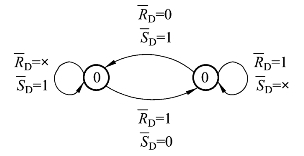

(2)状态转换图。图4.1.2所示是基本RS触发器的状态转换图。箭头的起点表示触发器的初态,箭头的终点表示触发器的次态。

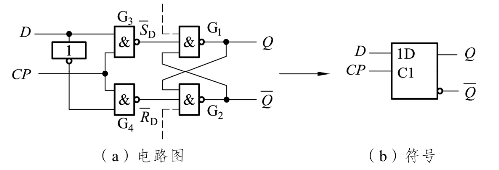

图4.1.1 基本RS触发器的电路及符号

图4.1.2 基本RS触发器的状态转换图

表4.1.1 RS触发器的特性表

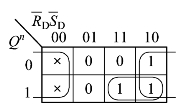

图4.1.3 基本RS触发器的卡诺图

(3)特性(次态)方程,图4.1.3所示是基本RS触发器的次态卡诺图,由卡诺图得基本RS触发器的特性方程。因为![]() 不能同时为0,即

不能同时为0,即![]() 。所以(4.1.1)式是带约束条件的特性方程:

。所以(4.1.1)式是带约束条件的特性方程:

【例4.1.1】如图4.1.4(a)所示是一个防抖动输出的开关电路,试分析其原理。

解:当开关K切换时,触点间碰撞不可避免地引起触点作阻尼振动,导致输入信号抖动,如图4.1.4(b)所示。例如,当K切换到 端的瞬时

端的瞬时 =0,使触发器复位(Q=0)。因为振动,触点K瞬间离开

=0,使触发器复位(Q=0)。因为振动,触点K瞬间离开 端,此时

端,此时 =

= =1,触发器保持复位状态,所以输出信号Q的波形不会出现抖动,如图4.1.4(b)所示。

=1,触发器保持复位状态,所以输出信号Q的波形不会出现抖动,如图4.1.4(b)所示。

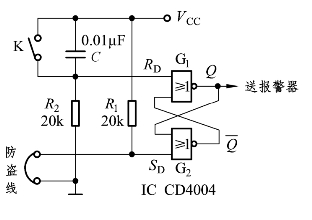

【例4.1.2】如图4.1.5所示是断线式防盗报警电路。CD4004是四2输入或非门,两个或非门构成高电平触发的基本RS触发器。接通电源电容C开始充电的瞬时RD=1,而SD=0,使基本RS触发器复位,Q输出低电平,不让报警器发声。充电完毕RD=0,而SD仍为0,基本RS触发器保持复位状态。当有贼闯入将防盗线(细导线)碰断时SD=1,RD=0,基本RS触发器置1,Q变为高电平使报警器发声。即使盗贼将防盗线又接上也不能使输出状态发生变化,除非将复位开关K闭合。

(www.daowen.com)

(www.daowen.com)

图4.1.4 例4.1.1的电路及波形图

图4.1.5 例4.1.2的电路

2.时钟电平控制的RS触发器

图4.1.6(a)是带时钟控制的RS触发器电路,图4.1.6(b)是其电路符号。该电路的时钟信号CP高电平有效。即当CP=0时,R 和S 信号被阻止,![]() ,触发器的状态保持。当CP=1时R 和S 信号被开放,允许触发器动作。且此时

,触发器的状态保持。当CP=1时R 和S 信号被开放,允许触发器动作。且此时![]() ,代入式(4.1.1)得带时钟控制的RS触发器的特性方程:

,代入式(4.1.1)得带时钟控制的RS触发器的特性方程:

图4.1.6 时钟电平控制的RS触发器的电路及符号

式(4.1.2)与式(4.1.1)的区别是:式(4.1.2)中的特性方程是在CP=1的条件下才成立,而式(4.1.1)中的特性方程是恒等式。式(4.1.2)中的R、S 受CP的控制且高电平有效,即只有当CP=1时才可能导致触发器动作,常将R称为同步复位触发信号,S 称为同步置位触发信号。而式(4.1.1)中的![]() 可以直接使触发器复位/置位(下标D表示直接之意),即不受时钟CP控制,所以

可以直接使触发器复位/置位(下标D表示直接之意),即不受时钟CP控制,所以![]() 为异步触发复位端,

为异步触发复位端,![]() 为异步触发置位端。

为异步触发置位端。

图4.1.6(c)是保留了异步复位/置位输入端的时钟控制RS触发器的电路符号,它是图4.1.6(a)中的G1门和G2门各自多接了一个输入信号(虚线),显然这两个信号各自具有直接复位/置位功能。

【说明】时钟控制信号是为了协调时序逻辑电路中多个触发器步调一致而引入的。例如,某电路中有三个带时钟控制的RS触发器,若要三个触发器同时复位,三个触发器的CP端应并联,且初始CP为0,当三个复位信号R1,R2,R3(均为1)分别到达后,CP才跳变为1,此时三个触发器同时复位。

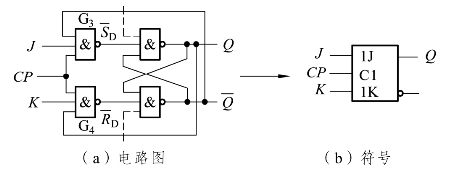

3.时钟电平控制的JK触发器

为了摒弃时钟RS触发器对输入信号的约束,将时钟RS触发器的输出信号反馈到输入级即得到时钟JK触发器,如图4.1.7所示。因为反馈到输入级的是一对互补信号,所以图4.1.7中的 和

和 不会同时为0,当然就不需要约束条件了。将G3门的输入

不会同时为0,当然就不需要约束条件了。将G3门的输入 视为式(4.1.2)的S,将G4门的输入KQ视为式(4.1.2)的R,由式(4.1.2)得的特性方程:

视为式(4.1.2)的S,将G4门的输入KQ视为式(4.1.2)的R,由式(4.1.2)得的特性方程:

图4.1.7 时钟电平控制的JK触发器的电路及符号

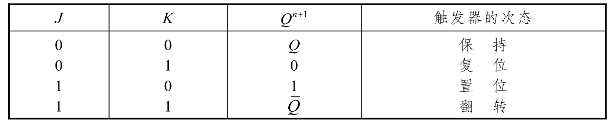

根据(4.1.3)式可得JK触发器的特性表4.1.2。由表4.1.2可知,J、K高电平有效,J为同步置位端,K为同步复位端,JK触发器无约束条件。

表4.1.2 JK触发器的特性表

4.时钟电平控制的D触发器

D触发器是单端输入的触发器,如图4.1.8所示。将S=D,R= 代入式(4.1.2),得时钟电平控制的D触发器的特性方程:Qn+1=D(CP=1)。因为信号D送入G3门和G4门相异,所以无约束条件。

代入式(4.1.2),得时钟电平控制的D触发器的特性方程:Qn+1=D(CP=1)。因为信号D送入G3门和G4门相异,所以无约束条件。

图4.1.8 时钟电平控制的D触发器的电路及符号

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。