1.3~8译码器的设计

译码是编码的逆过程,译码器是对输入的n位代码进行译码,从2n个不同的输入端产生一个对应的有效信号输出。

3~8译码器的设计:定义输入代码为3位二进制数,输出信号高电平有效。根据定义列出译码器的逻辑真值表,如表3.2.2所示。

表3.2.2 3~8译码器的真值表

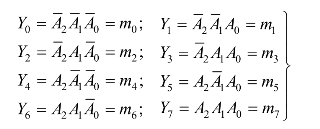

根据真值表得逻辑函数式为

![]()

根据3.2.5式可画出输出信号为高电平有效的3~8译码器的电路图。从3.2.5式可知该译码器的每个输出信号对应于一个逻辑最小项,因此高电平输出有效的译码器就是逻辑最小项发生器。

验证74HC138

2.3~8译码器74LS138

对(3.2.5)式两边取非得到低电平输出有效的译码器。另外增加三个片选输入端![]() 。当

。当![]() 时,允许该电路译码。否则该电路被禁止译码,输出信号全为1。于是得3~8译码器74LS138的逻辑函数及电路图3.2.5。

时,允许该电路译码。否则该电路被禁止译码,输出信号全为1。于是得3~8译码器74LS138的逻辑函数及电路图3.2.5。

图3.2.5 74LS138的电路

图3.2.6 例3.2.2的电路

【例3.2.2】试用两片74LS138构造一个4~16译码器。该译码器输入代码为4位二进制数,输出信号低电平有效。

解:如图3.2.6所示,当输入代码D3D2D1D0=1×××时,第Ⅰ片被片选,第Ⅱ片被禁止,第Ⅰ片译码产生一个有效信号输出;当输入代码D3D2D1D0=0×××时,第Ⅰ片被禁止,第Ⅱ片被片选,第Ⅱ片译码产生一个有效信号输出。

3.数据分配器

对(3.2.6)式两边取非,并将片选输入信号 ,

, 接地,S0为串行数据(逐位传输的数据)输入端D,于是得1→8数据分配器的逻辑函数Yi=miD(i=0,1,…,7)。图3.2.7为其电路及功能示意图。其功能是将输入数据D分配到地址码A2A1A0所指定的某输出端输出。(https://www.daowen.com)

接地,S0为串行数据(逐位传输的数据)输入端D,于是得1→8数据分配器的逻辑函数Yi=miD(i=0,1,…,7)。图3.2.7为其电路及功能示意图。其功能是将输入数据D分配到地址码A2A1A0所指定的某输出端输出。(https://www.daowen.com)

图3.2.7 数据分配器及功能示意图

4.显示译码器

1)七段数码管

七段数码管是用来显示十进制数字的,它的每一段是一只发光二极管,如图3.2.8(a)所示。七段数码管分为共阴极和共阳极两种,分别如图3.2.8(b),(c)所示。对于共阴极的七段数码管,当a~g端为高电平时对应的那段二极管亮,当a~g端为低电平时对应的那段二极管灭。对于共阳极的七段数码管,当a~g端为高电平时对应的那段二极管灭,当a~g端为低电平时对应的那段二极管亮。

图3.2.8 七段数码管

2)显示译码器的设计

用于驱动共阴极七段数码管的显示译码器,其输入代码为8421BCD码,输出信号高电平有效。根据定义列该显示译码器的逻辑真值表如表3.2.3所示。

表3.2.3 显示译码器的真值表

图3.2.9 显示译码器的卡诺图

根据真值表得a,b,…,g的卡诺图如图3.2.9所示。用“圈0法”求得逻辑函数式

根据式(3.2.7)画出显示译码器的逻辑电路图,如图3.2.10所示。

图3.2.10 显示译码器

3)显示译码器CC14547

CC14547的输入代码为8421BCD码,输出信号高电平有效。CC14547还有一个消隐控制输入端 (

( 与a~g 端分别相与输出),当

与a~g 端分别相与输出),当 =0时,a~g端输出均为低电平,使七段数码管熄灭;当

=0时,a~g端输出均为低电平,使七段数码管熄灭;当 =1时,译码输出有效。另外,CC14547的输出级采用双极型晶体管结构,具有较大的输出驱动电流能力,可直接驱动LED或其他显示器件。

=1时,译码输出有效。另外,CC14547的输出级采用双极型晶体管结构,具有较大的输出驱动电流能力,可直接驱动LED或其他显示器件。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。