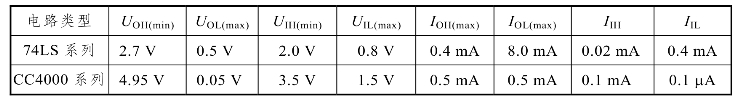

在不同类型的电路连接时,因为前一级电路的输出信号要符合后一级电路的输入要求,所以驱动门与负载门需从电压和电流两方面达到匹配,即必须同时满足四个条件:UOH(min)≥UIH(min),UOL(max)≤UIL(max),IOH(max)≥IIH,IOL(max)≥IIL。如表2.4.1所示给出TTL电路和CMOS电路在电源电压均为5 V的情况下,其输入/输出特性参数。

表2.4.1 TTL电路和CMOS电路的输入/输出特性参数

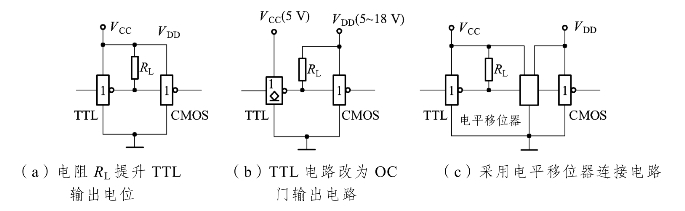

1.TTL电路驱动CMOS电路

当TTL电路驱动CMOS电路时,上述四个条件中有三个条件满足,但是不满足UOH(min)≥UIH(min)。

(1)当VDD=VCC=5 V时,在TTL门电路的输出端加上拉电阻RL来提升TTL的输出电位,见图2.4.4(a)。因为当TTL门电路的输出高电平时,其T5管截止,VDD→RL→GND不是通路,则RL两端等电位,所以TTL门电路的输出电位提高了。

图2.4.4 TTL驱动CMOS的电路

(2)当VCC=5 V,VDD=5~18 V,即VDD>VCC时,常将TTL电路改用OC门输出,见图2.4.4(b)。因为当OC门输出高电平时,RL两端等电位,CMOS的输入电平等于VDD。

(3)采用专门的电平移位器进行连接,见图2.4.4(c)。

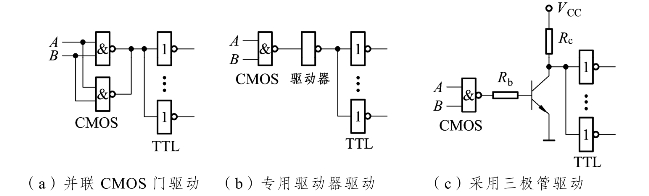

2.CMOS电路驱动TTL电路

(1)当VDD=VCC=5 V时,若只有一个负载门,CMOS电路可以直接驱动TTL电路。但是当负载门较多时,应采用以下方法:

① 同一芯片上的CMOS门并联使用,以增大CMOS电路输出的总电流,见图2.4.5(a)。

② 增加一级专用的驱动器,例如CC4049,见图2.4.5(b)。

③ 采用三极管电路驱动,见图2.4.5(c)。(https://www.daowen.com)

(2)当VDD>VCC时,采用专门的电平移位器连接,即如图2.4.4(c)所示的方法解决。

图2.4.5 CMOS驱动TTL的电路

3.CMOS电路与TTL电路的比较

(1)TTL电路是电流控制器件,而CMOS电路是电压控制器件。

(2)TTL电路的速度快,传输延迟时间短(5~10 ns)。CMOS电路的速度慢,传输延迟时间长(25~50 ns)。传输延迟时间是指从输入信号的变化到输出信号响应所需的时间。

(3)TTL电路的最高工作频率比CMOS电路的最高工作频率高,CMOS电路的最高工作频率一般低于10 MHz,而TTL电路的最高工作频率可达100 MHz以上。

(4)CMOS电路的电压工作范围大,可以在VDD=3~18 V范围内正常工作。注意VDD越大,则输出的高电平越大。而TTL电路的工作电压一般为5 ~7 V。

(5)CMOS电路的逻辑摆幅大,电源利用率高。当VDD=5 V时,逻辑摆幅=UOH(min)- UOL(max)=4.95-0.05=4.90(V),电源利用率为逻辑摆幅与电源电压之比,此时电源利用率接近1。

(6)CMOS电路的抗干扰能力强。当VDD=5 V时,高电平噪声容限UNH和低电平噪声容限UNL均为1.45 V,比TTL电路(74LS系列)的噪声容限0.4 V大得多。

(7)CMOS电路的静态功耗低。静态功耗是指虽然CMOS电路加了电源电压,但未加输入信号时的电路功耗。例如,PC机断电后,CMOS RAM芯片由一块后备的锂电池供电,即使系统掉电其存储信息也不会丢失。CMOS RAM芯片存储的是关于系统配置的具体参数,其内容可通过设置程序进行读写。另外,COMS电路的动态功耗与输入信号的脉冲频率有关,频率越高,功耗越大,芯片越热。

(8)CMOS电路的扇出系数大,对负载的驱动能力小。TTL电路的扇出系数小,对负载的驱动能力大。注意扇出系数和对负载的驱动能力是两个不同的概念,前者是指电路带同类逻辑门的能力,后者是指提供给负载的电流大小。

(9)CMOS电路的温度稳定性好,这是因为CMOS管比晶体三极管的温度稳定性好。

(10)对多余输入端的处理。CMOS电路的输入端不允许悬空,因为悬空会使电位不定,破坏正常的逻辑关系。另外,悬空时输入阻抗高,易受外界噪声干扰,使电路产生误动作,而且也极易造成栅极感应静电而击穿。所以CMOS与门的多余输入端要接高电平,CMOS或门多余输入端要接低电平。若电路的工作速度不高,且功耗不需特别考虑时,则可以将多余输入端与使用端并联。而TTL电路的多余输入端悬空时相当于输入端接高电平,因为这时可以看作输入端接了一个无穷大的电阻。所以TTL与门的多余输入端悬空,TTL或门多余输入端要接地。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。