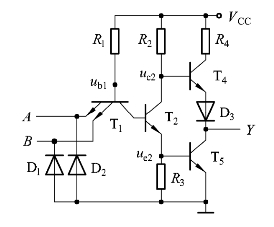

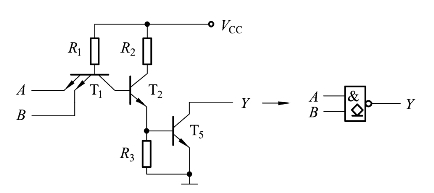

1.TTL与非门

TTL与非门电路如图2.2.4所示,其输入端是一个多发射极结构,即多个发射结并联。当输入信号均为UIH时,此时相当于TTL非门电路的第2种状态,即输出信号uO为低电平。当有一个或多个输入信号为UIL时,那么T1管都会导通使ub1钳位于1 V,此时相当于TTL非门电路的第1种状态,即输出信号uO为高电平,所以![]() 。

。

或非门逻辑 功能验证

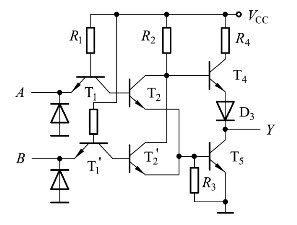

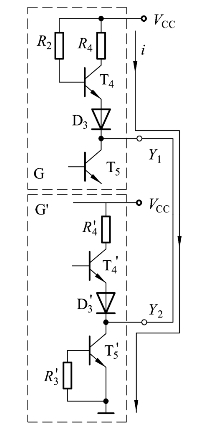

2.TTL或非门

如图2.2.5所示是TTL或非门电路,当A端输入高电平时,则T2管和T5管饱和导通,输出端Y为低电平;当B端输入高电平时,则T2′管和T5管饱和导通,输出端Y为低电平;当A,B两端输入均为低电平时,使T2管和![]() 管同时截止,输出端Y为高电平,所以

管同时截止,输出端Y为高电平,所以![]() 。

。

图2.2.4 TTL与非门电路

图2.2.5 TTL或非门电路

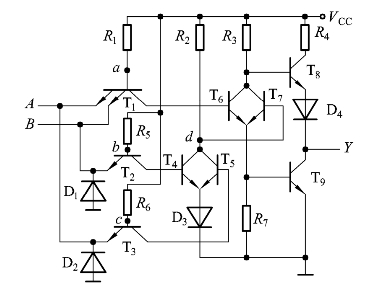

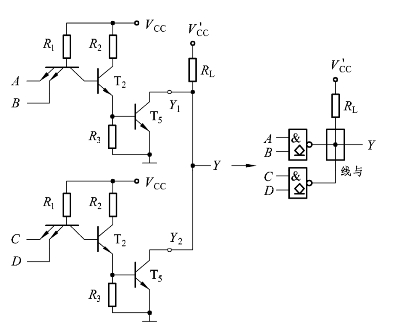

3.TTL与或非门

如图2.2.6所示是TTL与或非门电路,其电路原理请读者自己分析。

图2.2.6 TTL与或非门电路

【说明】平均传输延时tpd是指门电路的开关速度,它表示从输入信号发生跳变到输出信号作出响应的时间。也就是说tpd越小门电路响应速度越快。上面介绍的与非门、或非门、与或非门同图2.2.1的TTL非门电路一样,信号从输入到输出都经过输入级→倒相级→输出级,因此tpd是相同的。所以这些门电路称为基本逻辑门,这里的tpd称为基本门延时,其值为5~10 ns。1 ms=10-3s,1 μs=10-6s,1 ns=10-9s,1 ps=10-12s。

4.TTL异或门

(1)如图2.2.7所示是TTL异或门电路,当A,B两端输入均为低电平时,ua=ub=uc=1 V,T4管、T5管和D3管截止。因为支路VCC→R2→T7→T9→GND是通路,则T7管和T9管导通、T8管截止,所以输出端Y为低电平。

(2)当A,B两端输入均为高电平时,ua=4.3 V导致T6管和T9管导通、T8管截止,所以输出端Y为低电平。

(3)当A端输入为低电平,而B端输入为高电平时,ua=uc=1 V导致T5管和T6管截止,ub=4.3 V导致T4管和D3管导通,ud=1 V使T7管和T9管截止,T8管和D4管导通,所以输出端Y为高电平。

(4)当A 端输入高电平,而B端输入为低电平时,与第(3)种状态相同。

图2.2.7 TTL异或门电路

综上所述,Y =A B。

B。

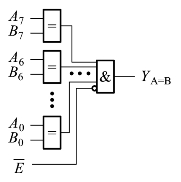

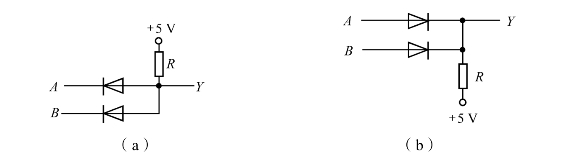

异或门取非即为同或门,如图2.2.8所示是由8个同或门和一个与门构成的8位数据比较器74LS520,与门左边的小圆圈表示 取非后送入与门。当允许比较信号

取非后送入与门。当允许比较信号 =0时,输出信号YA=B=1表示A=B,输出信号YA=B=0表示A ≠B;当

=0时,输出信号YA=B=1表示A=B,输出信号YA=B=0表示A ≠B;当 =1时,输出信号YA=B保持低电平,74LS520的比较功能失效。在数字电路中,习惯上将控制信号的标记加一条上划线表示低电平有效,未加上划线表示高电平有效。

=1时,输出信号YA=B保持低电平,74LS520的比较功能失效。在数字电路中,习惯上将控制信号的标记加一条上划线表示低电平有效,未加上划线表示高电平有效。

图2.2.8 8位数据 比较器74LS520

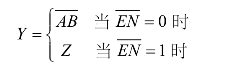

5.TTL三态输出门

如图2.2.9所示是TTL三态输出门电路,其输出有三种状态:高电平、低电平和高阻。高阻(Z)状态亦称为浮空状态,它既不是高电平也不是低电平,这种状态将输入逻辑信号阻断,使之不能送往下一级电路。

当 =0时,p点为高电平,D管截止,此时的电路等效于与非门,即Y=

=0时,p点为高电平,D管截止,此时的电路等效于与非门,即Y= 。当

。当 =1时,p点为低电平,T1管导通,其基极钳位于1 V,使T2管和T5管截止。因为支路VCC→ R2→q→D→p是通路,所以D管导通,使q点电位钳位于1.1 V(0.4 V+0.7 V)以下,T4管的基极电位没有达到1.4 V以上,则T4管截止。由于T4管和T5管同时截止,所以输出端既不是高电平也不是低电平,处于浮空状态。

=1时,p点为低电平,T1管导通,其基极钳位于1 V,使T2管和T5管截止。因为支路VCC→ R2→q→D→p是通路,所以D管导通,使q点电位钳位于1.1 V(0.4 V+0.7 V)以下,T4管的基极电位没有达到1.4 V以上,则T4管截止。由于T4管和T5管同时截止,所以输出端既不是高电平也不是低电平,处于浮空状态。

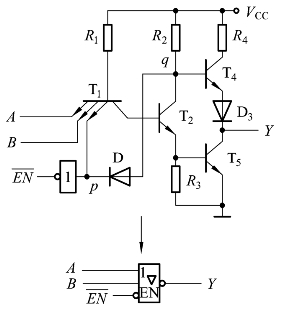

如图2.2.10所示是双向数据缓冲器74LS245,当输出使能信号 =1时,所有的三态门被阻断,A端与B端隔离。当

=1时,所有的三态门被阻断,A端与B端隔离。当 =0时,方向控制信号DIR=1将左边的三态门选通,右边的三态门阻断,数据由A端送往B端;方向控制信号DIR=0将右边的三态门选通,左边的三态门阻断,数据由B端送往A端。

=0时,方向控制信号DIR=1将左边的三态门选通,右边的三态门阻断,数据由A端送往B端;方向控制信号DIR=0将右边的三态门选通,左边的三态门阻断,数据由B端送往A端。

图2.2.9 TTL三态输出门电路及符号

(https://www.daowen.com)

(https://www.daowen.com)

图2.2.10 双向数据缓冲器74LS245

【说明】在计算机内部,CPU与外部数据总线通过双向数据缓冲器连接,CPU发出的读/写控制信号打在双向数据缓冲器的方向控制端,就可以实现对外部数据的读或写操作。

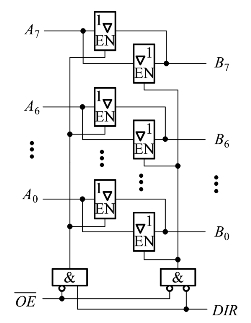

【阅读】二极管与、或电路的局限*

有的教材将图2.2.11所示的电路称为二极管与门、或门电路,这是绝对错误的。因为门电路不仅要具备某种逻辑功能,而且还要有一定的噪声容限。

对于图2.2.11(a),当输入信号A、B中任一个为低电平0 V时,其输出Y=+0.7 V可视为低电平,该电路存在逻辑与的关系。但是当A、B信号均为低电平+0.3 V时,其输出Y=+1.0 V就不是正常的逻辑信号了。

图2.2.11 二极管与、或电路

对于图2.2.11(b),当输入信号A、B中任一个为高电平+5 V,其输出Y=+4.3 V可视为高电平,该电路存在逻辑或的关系。但是当A、B信号均为高电平+2.5 V时,其输出Y=+1.8 V就不是正常的逻辑信号了。而且当输入信号A、B均为低电平+0.3 V时,其输出Y=-0.4 V也不是正常的逻辑信号。

综上所述,若按图1.1.1(c)定义数字信号,对于图2.2.11所示的与、或电路连正常的数字信号都不能通过,其噪声容限几乎为0,还能叫门电路吗?这就是为什么TTL基本门电路都是由输入级→倒相级→输出级三级构成的。若图2.2.11中的A、B信号来自TTL门电路的输出,就不能保证得到的输出信号Y一定是数字信号,这样的电路还有多少实际价值呢?

6.集电极开路输出(OC)门*

普通TTL 门电路的输出级采用的是推拉式输出电路结构(见图2.2.1),这种电路结构的特点是T4管和T5管不会同时导通,且具有输出电阻很小的优点。但是这种结构电路的输出端不能并联。TTL门电路输出端短接电路如图2.2.12所示。若Y1为高电平,Y2为低电平,则VCC→R4→T4→D3→T5′→GND是通路,其输出电平会大于UOL(max)而小于UOH(min),引起逻辑混乱。而且此时Y1为3.6V的高电平,Y2为0.3 V的低电平,Y1与Y2之间的电压达3.3 V而电阻几乎为零,故电流很大会损毁T5′管。

如图2.2.13所示是集电极开路输出的门电路,该电路能够克服上述缺点。这种电路工作时需要外接电源和上拉电阻。当A,B同时为高电平时T5管饱和导通,Y输出低电平;当A,B有一个为低电平时T5管截止,外接电源和上拉电阻使Y输出高电平,则Y=AB。

图2.2.12 TTL门电路输出端短接

图2.2.13 OC与非门电路及符号

1)OC 门主要的应用

(1)实现线与。图2.2.14是两个OC结构的与非门的输出端并联。只要Y1,Y2有一个是低电平,则必有一个T5管处于饱和导通状态,使Y为低电平;只有Y1,Y2同时为高电平时,两个T5管都处于截止状态,才导致Y为高电平,所以Y=Y1·Y2,即多个OC门的输出线并联,逻辑上是“与”关系。

(2)实现电平转换。VLSI的发展趋势之一就是要降低功耗,现在许多VLSI芯片的工作电压只有3.3 V,有的甚至更低。那么TTL门电路如何为工作电压只有3.3 V的VLSI芯片提供逻辑信号呢?当然需要进行电平转换,图2.2.15就是实现这种转换的电路。当输入A为高电平时T5管饱和导通,输出Y为低电平。当输入A为低电平时T5管截止,此时+3.3 V→RL→Y→T5→GND不是通路(忽略T5管截止时微弱的漏电流),uY≈+3.3 V。即输出高电平的范围变为UOH(min)~+3.3 V,输出信号Y 则可送入工作电压只有3.3 V的VLSI芯片。

图2.2.14 OC门输出端的线与连接

图2.2.15 用OC门实现电平变换的电路

(3)驱动大电流负载。有些OC门的输出管设计尺寸较大,足以承受较大的电流和较高的电压。例如,OC驱动门74LS07的最大负载电流为40 mA,外接电源可达15 V。通常用来驱动发光二极管、七段数码管、微型步进电机等负载。

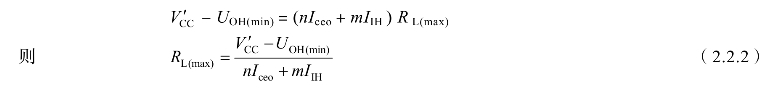

2)上拉电阻的选择

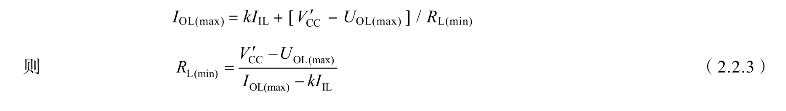

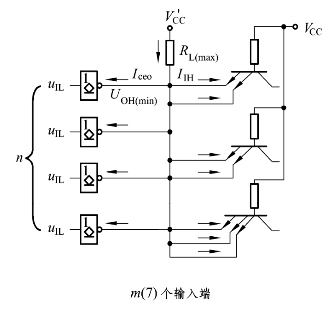

计算OC门负载电阻最大值的电路图如图2.2.16所示。当所有OC门同时截止时,输出uO为高电平。显然RL的值越大导致uO的电位越低。但是不允许输出高电平低于UOH(min),所以

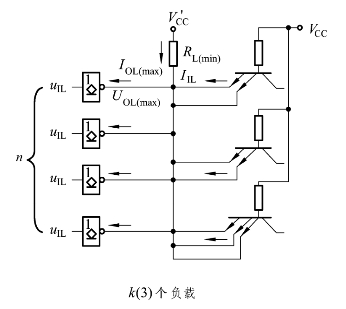

计算OC 门负载电阻最小值的电路图如图2.2.17所示。当OC门中只有一个饱和导通时,输出uO为低电平。显然RL的值越小导致流入这个OC门的电流越大,但是不能超过该OC门输出为低电平时的最大允许电流IOL(max),所以

图2.2.16 计算OC门负载电阻最大值的电路

图2.2.17 计算OC门负载电阻最小值的电路

注意门电路输入端的电流IIH和IIL的方向是相反的,请参看2.4.1。对于图2.2.16和图2.2.17的电路,n=4,m=7,k=3,VC′C=5 V,UOH(min)=2.4 V,IIH=40 μA,UOL(max)=0.4 V,IOL(max)=16 mA,IIL=1.6 mA,Iceo=200 μA,则可求得RL(max)≈ 2.41 kΩ,RL(min)≈0.41 kΩ。则上拉电阻RL取值1~2 kΩ。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。