单片机层次原理图的PCB设计和FPGA设计是本节的重点内容,此部分内容综合度高,与前面内容相关度较强,有助于进一步熟悉层次原理图的操作和元件库的自主设计等。

常见问题:

1)混淆PCB向导和PCB封装向导,无法进入正确的向导界面。PCB向导(PCB BOARD WIZARD)一般在“File”窗口的最下面,需要鼠标拖动,隐藏一部分不用的子窗口才能看到。而封装向导在PCB编辑器的“File”菜单中“File”→“New”→“Pcb Library”。

2)没有根据实际需要选用相应的PCB。在工程文件下用“Add”→“New”→“Pcb”命令添加的PCB文件,实际上使用默认的PCB(双层普通PCB),这种板适合THT或常规应用的设计和排布,但不一定适合SMT或其他高端应用的设计和排布。所以在特定应用条件下,应使用PCB向导先建立一个合适的PCB,再将它添加到工程文件中,而不是直接创建。

3)忽略掉PCB软件设计和实际生产的密切关系,出现致命设计缺陷。在本节项目资讯6.2.2中将PCB设计中的常见错误进行了小结,这些错误原理上并不难理解,但却是企业实际生产中经常碰到的具体问题,是企业生产管理经验的总结。所以读者不能够忽略这些重要的资讯,在学习过程中应提醒自己加以注意,养成良好的设计习惯。

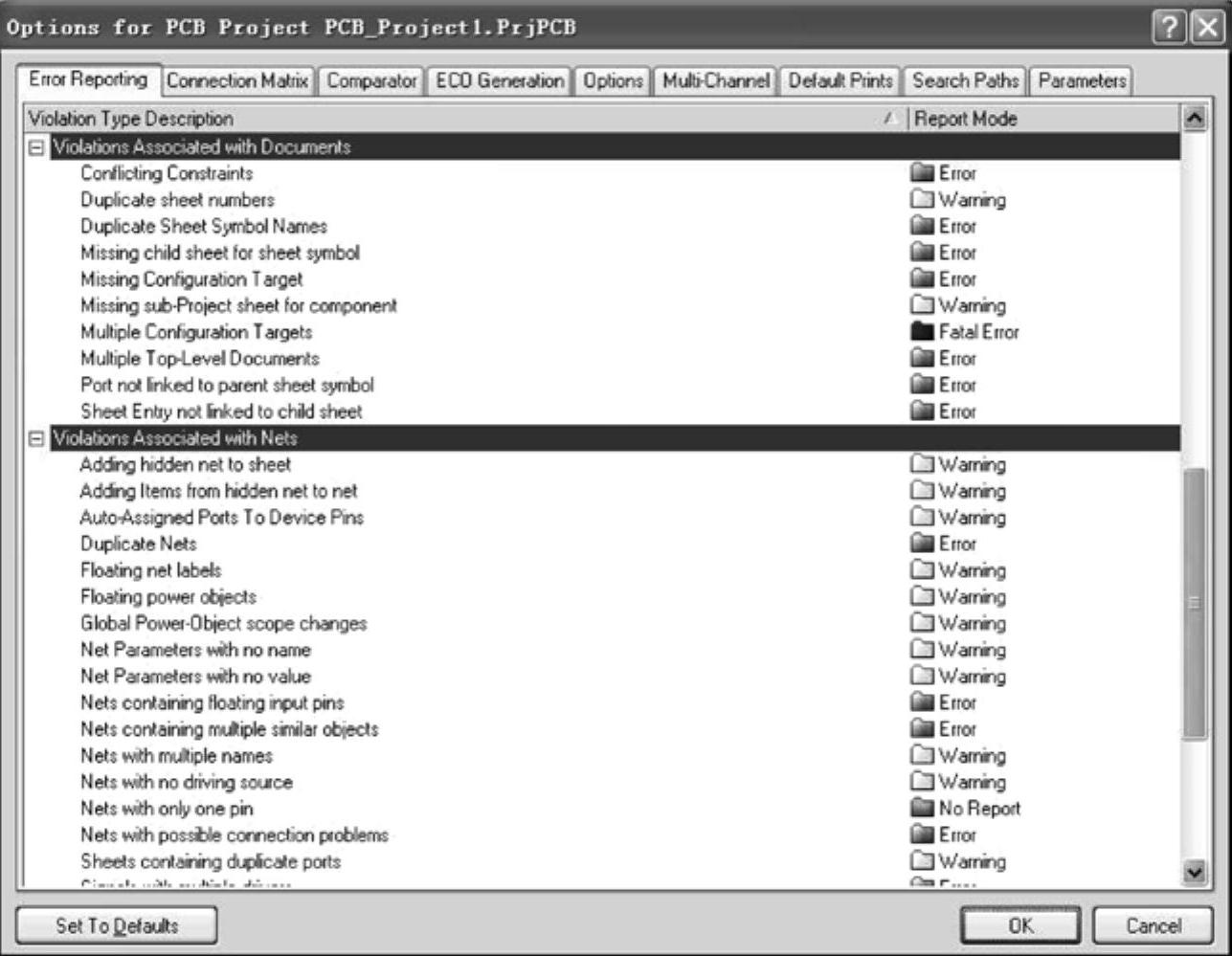

4)没有正确给出原理图仿真信息,导致仿真失败。原理图仿真与ERC检查有很大不同,ERC仅仅是电气检查,检查报错规则在工程文件“Project”→“Option”选项中,如图6-66所示。

图6-66 原理图的ERC检查规则

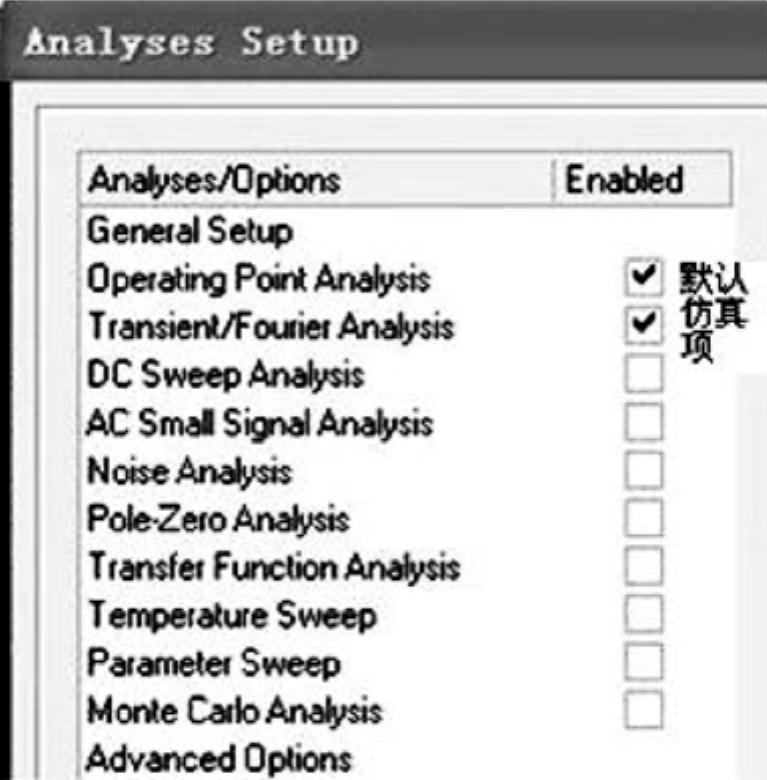

实际上,ERC检查是一个先决条件,没有通过ERC检查的原理图不可能进行仿真操作,但通过了ERC检查,仅仅表明所有电路连接,所有网络都符合电气标准,并不代表仿真可以进行。也就是说,仿真操作的要求比ERC的要求更高,需要更详细的元件信息,引脚信息,和关于仿真的信号条件,仿真的具体节点等。这里面任何一项出现问题,都会导致仿真无法进行。另外,如果没有特殊仿真要求,可以使用默认的仿真项目,如图6-67所示。

(https://www.daowen.com)

(https://www.daowen.com)

图6-67 仿真对话框的默认仿真项

使用默认项,在缺乏部分有效信息的条件下仍可以进行基本分析,如直流分析。

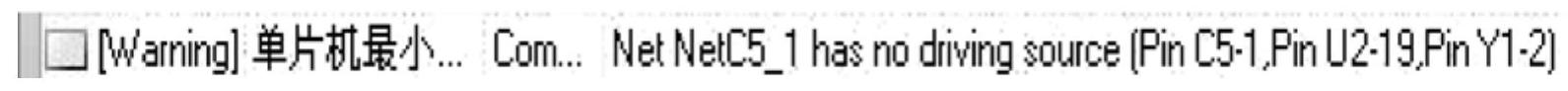

5)丢失引脚的仿真属性,导致仿真错误。一般独立元件库中的元件都有自己的引脚仿真信息,但在层次原理图中,经常报告原理图入口(Port)与元件引脚的电气属性不匹配的错误。这时候为了通过ERC检查,常常把元件引脚的电气属性改为“Passive”。但这在仿真时会报告丢失激励错误,如图6-68所示。

图6-68 丢失激励源的消息框

这是因为DXP不允许电源(VCC、GND)引脚与其他I/O属性的接口相连,要解决此问题,在层次原理图设计中,子图与子图或子图与母图只能用普通I/O入口相联系,而尽量避开采用电源接口;如果实在需要电源接口联系,就不要进行复杂的仿真操作。

6)无法对层次原理图进行PCB导入。层次原理图与普通原理图的PCB导入步骤完全一样,都需要建立一个空白PCB文件,然后在放置在同一工程文件下进行内部更新。工程中只有原理图文件是无法进行更新操作的。

7)不理解元件手动排布的重要性,用自动排布代替手动排布,这是初学者最容易犯的一种错误。元件的自动排布,不论采用哪种方案,都只能得到一个PCB雏形,这个雏形既不能满足元件的布局效果,又不能满足元件布线综合效果。所以手动调整是一个不可省略的步骤,手动调整既针对PCB整体效果,又针对单个元件的走线特点,即力求飞线距离最短和交叉飞线最少。

8)不理解FPGA工程与普通PCB工程的区别,不了解VHDL语言的特点,盲目使用FPGA工程。实际上,VHDL语言是针对大型电路项目的一种先进开发语言,只需要给出信号的输入,输出信息,即可以生成对应电路模块,是适合大规模集成电路的设计方案。FPGA工程包含更多的专用元件库和原理图符号,其原理图频繁使用总线和端口组,PCB则要求更紧密、更合理和更专业的元件排布,是综合难度很高的一种设计方案。所以,本节仅仅介绍一些基本使用方法和基本操作,对于普通电路应用,即使是层次原理图,并不非要采用复杂的FPGA项目方案。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。