【摘要】:DXP支持VHDL语句的文件,可以由VHDL语言直接生成,下面以一个单片机电路为例,介绍如何进行FPGA的设计。首先新建一个FPGA工程文件“FPGA Project”,然后添加一个或若干个(看需要)空白的VHDL文件,如图6-58所示。图6-59 VHDL的预声明图6-60 元件的声明图6-61 网络表声明完成语句书写后,进行编译,使用“Simulator”→“Simulate”命令,如图6-62所示。图6-62 VHDL编译命令图6-63 用VHDL生成原理图符号然后会出现询问对话框,询问元件符号的引脚放置形态,如图6-64所示。

DXP支持VHDL语句的文件,可以由VHDL语言直接生成,下面以一个单片机电路为例,介绍如何进行FPGA的设计。

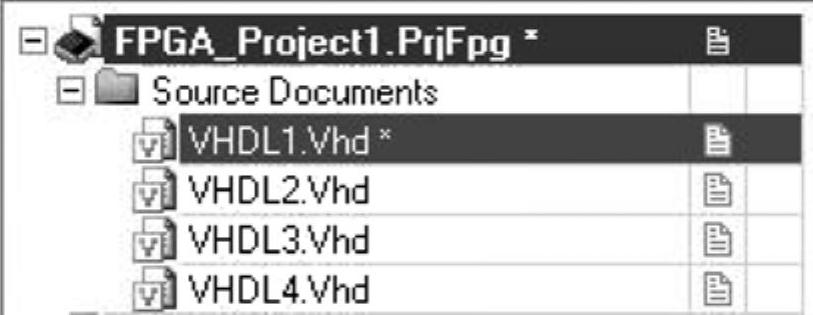

首先新建一个FPGA工程文件“FPGA Project”,然后添加一个或若干个(看需要)空白的VHDL文件,如图6-58所示。

图6-58 新建的FPGA工程

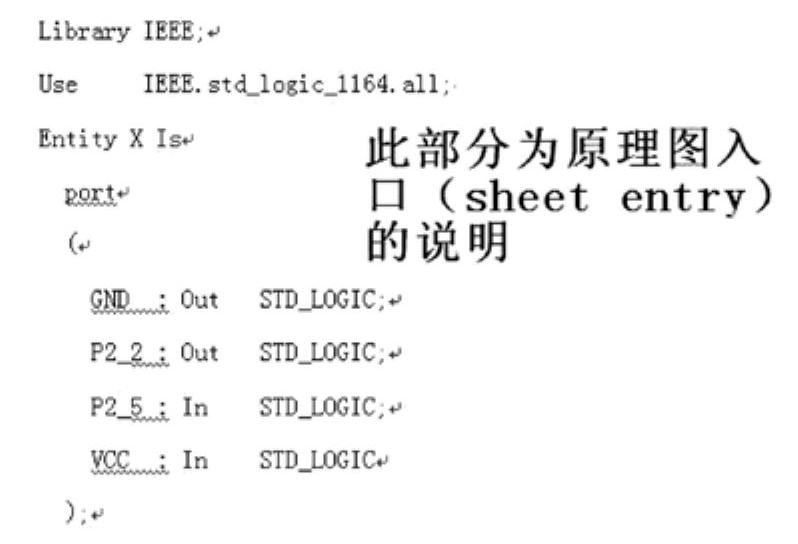

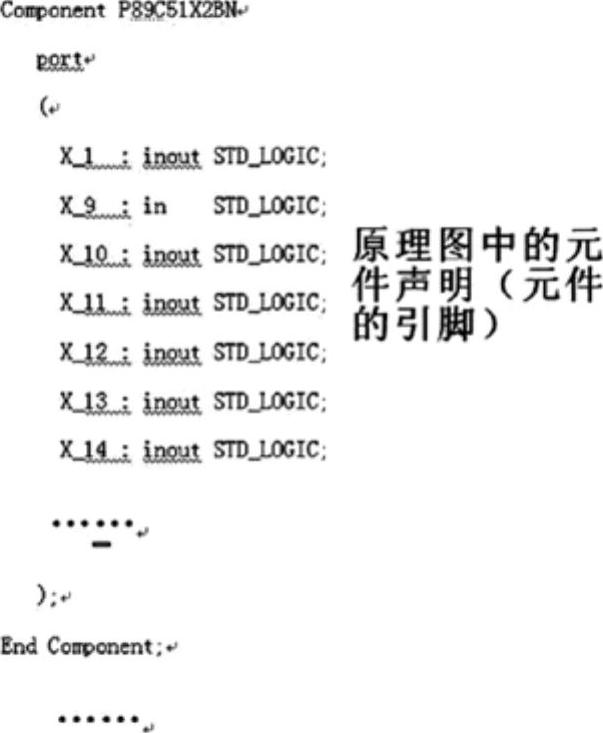

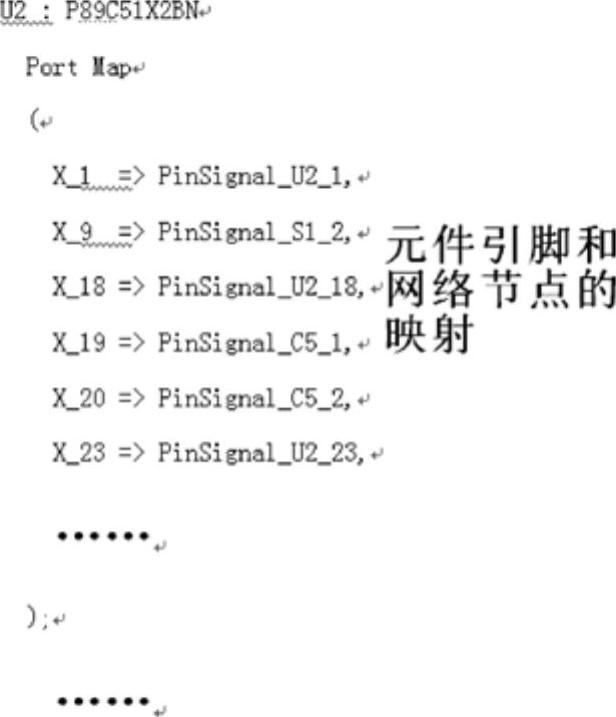

然后在空白VHDL文件中写入VHDL语句。VHDL的语句结构如图6-59至图6-61所示。

图6-59 VHDL的预声明

图6-60 元件的声明

图6-61 网络表声明

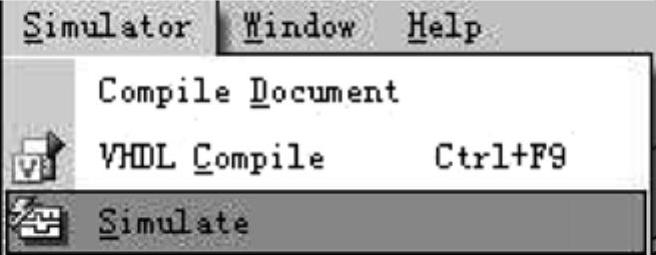

完成语句书写后,进行编译,使用“Simulator”→“Simulate”命令,如图6-62所示。

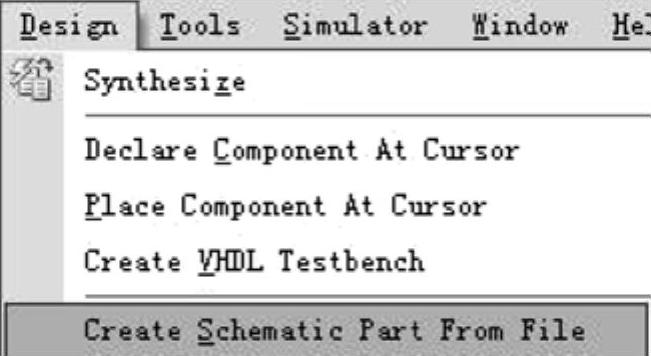

如果编译无误,则可以进行转换,用“Create”→“Create Schematic Part From File”命令,将VHDL语句转换成原理图符号文件,按图6-63操作。(www.daowen.com)

图6-62 VHDL编译命令

图6-63 用VHDL生成原理图符号

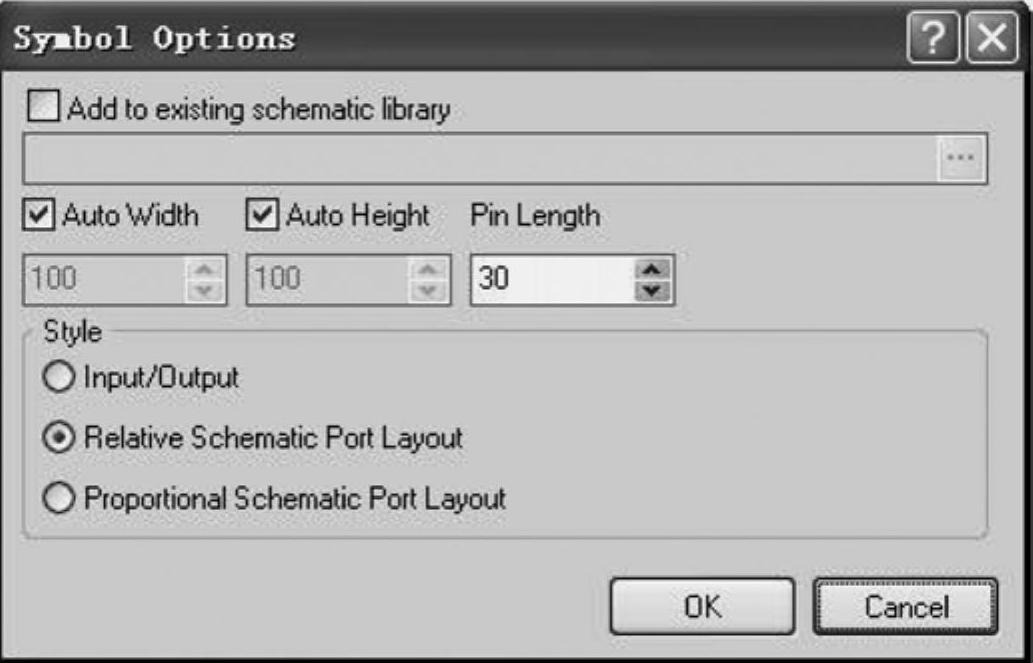

然后会出现询问对话框,询问元件符号的引脚放置形态,如图6-64所示。

图6-64 “引脚形态询问”对话框

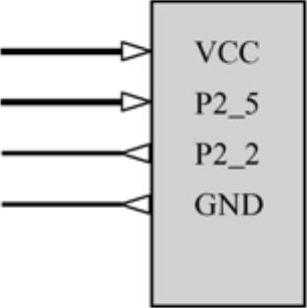

生成的元件符号如图6-65所示。

此元件默认保存于“schlib1.schlib”库文件中。

图6-65 得到原理图元件

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。