global memory在GPU的存储层次中容量最大,但访存延迟又很高。但是,在GPU编程过程无法避免使用global memory。因此,global memory的访存优化对整个GPU程序的性能有着至关重要的作用。

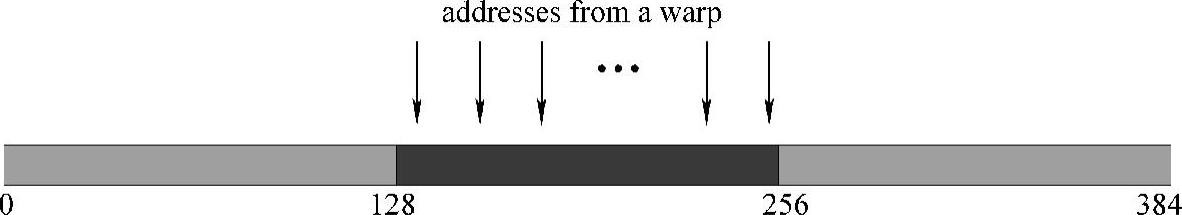

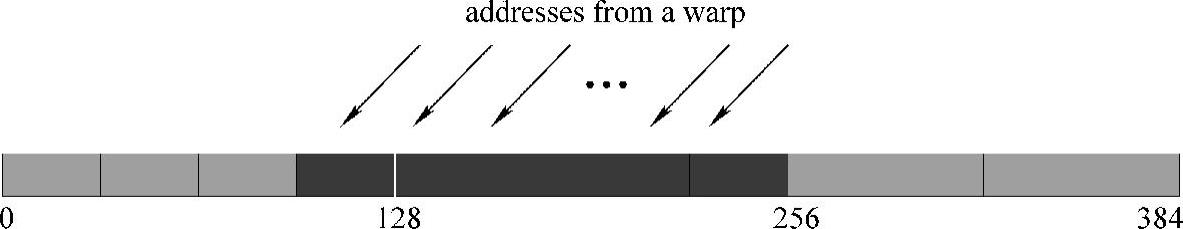

自Fermi架构以来,NVIDIA GPU引入了一级和二级缓存,要求在global memory的访存中每个warp访存的大小是一个128B的cache line或多个cache line。因此,CU-DA中提供了一种合并访存机制优化global memory访存。合并访存是指当一个warp访存的数据是连续的、对齐的(必须对齐在内存地址的32B的整数倍上)且数据大小是128B的整数倍时,warp内线程的访存会被合并为一次或多个访存。如果warp的每个线程访问相邻的4B的数据,并且warp对齐在128B的内存片断上,那么可以实现global memory合并访存机制如图5-2所示。如果warp与内存映射没有对齐,访存机制如图5-3所示。因此,实现warp与内存映射的对齐和充分利用cacheline可以有效提高global memory的访存效率。

图5-2 global memory合并访存机制(www.daowen.com)

图5-3 访存机制

因此,在global memory的访存优化中应该尽可能使其合并访存或充分利用cache line机制。global memory访存的连续性和对齐就显得尤为重要,无论是访存的不连续还是不对齐都会导致访存效率急剧下降。在访存连续且对齐的情况下,一般通过向量化可以实现global memory的合并访存或者cache line的充分利用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。