【摘要】:图5.18MIPI的DSI逻辑叠成结构框图在DSI数据传输过程中,了解物理层接口运用特性规范十分关键。图5.19MIPI的物理通道信号电平示意图当供电电压为2.5~3.3 V时,低功耗信令模式的通道信号高电平为典型值1.2 V,低电平为参考地,一般选择0;高速信令方式时,通道信号共模电压为典型值200 mV,差模电压为典型值200 mV。在HS数据突发期间,时钟通道应处于高速模式,向MIPI从设备提供DDR时钟。

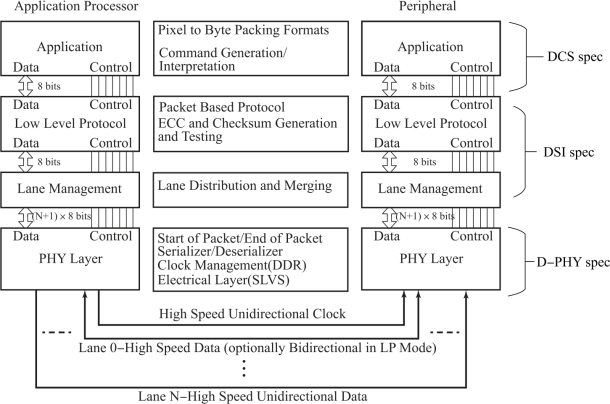

图5.18 MIPI的DSI逻辑叠成结构框图

在DSI数据传输过程中,了解物理层(D-PHY)接口运用特性规范十分关键。MIPI的物理层接口具有同步、高速、低功耗、低成本等优点,一般芯片的MIPI接口物理支持大于或等于2通道,并主要支持3种通道类型:单向时钟通道、单向数据通道、双向数据通道。MIPI的物理层通道接口采用差分信号接口,且支持两种速度的通信模式:一种为低速模式,即低功耗信令模式,这种模式主要用于发送控制指令,每个通道最大频率不超过10 MHz;另外一种为高速信令方式,这种模式主要用于高速数据传输,每个通道速度范围为80 Mb/s~1 Gb/s。两种传输模式的速度不一样,其本质原因在于两种模式的信号电平阈值不一样,如图5.19所示。

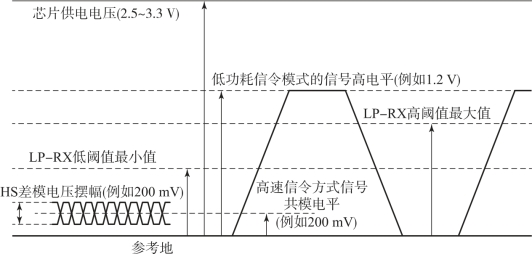

图5.19 MIPI的物理通道信号电平示意图(www.daowen.com)

当供电电压为2.5~3.3 V时,低功耗信令模式的通道信号高电平为典型值1.2 V,低电平为参考地(Reference ground),一般选择0;高速信令方式时,通道信号共模电压为典型值200 mV,差模电压为典型值200 mV。在高速模式下,时钟通道为高速数据传输提供从主机到从机的低摆幅差分DDR(半速率)时钟信号。时钟开始和停止过程如图5.20所示。

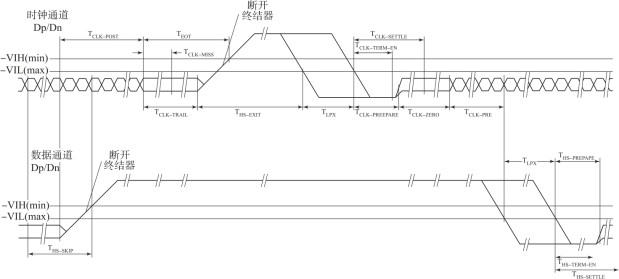

图5.20 时钟通道信号在高速模式和低功耗模式之间的切换示意图

高速数据传输以突发形式发生。传输从停止状态开始,并以停止状态结束。在突发之间的中间时间内,数据通道应保持停止状态,除非在通道上出现回传或退出请求。在HS数据突发期间,时钟通道应处于高速模式,向MIPI从设备提供DDR时钟。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。

有关光学相控阵天线技术的文章