【摘要】:D 触发器的逻辑符号如图8-8a所示。图8-8b为D 触发器的波形图。表8-4为D 触发器的逻辑功能真值表。表8-4D触发器的逻辑功能真值表图8-8D触发器图8-9为双D 触发器CC4013的芯片管脚功能图。每片含两个相同的D 触发器,可以单独使用。解 电路中,F1 的Q1 接F2 的D2,F2 的 接F1 的D1,两个D 触发器共用一个CP脉冲。

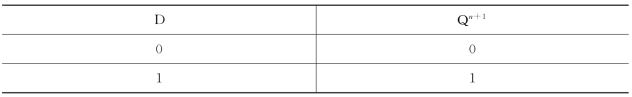

D 触发器的逻辑符号如图8-8a所示。它有一个信号输入端D 和一个时钟脉冲输入端CP,上升沿触发, 、

、 为直接置0、置1端,负脉冲有效。

为直接置0、置1端,负脉冲有效。

D 触发器的状态方程为

![]()

即在CP脉冲的作用下,D 触发器的新状态,总是与D 端的状态相同。图8-8b为D 触发器的波形图。表8-4为D 触发器的逻辑功能真值表。

表8-4 D触发器的逻辑功能真值表

图8-8 D触发器

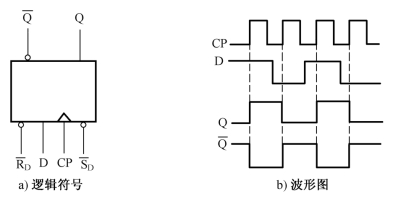

图8-9为双D 触发器CC4013的芯片管脚功能图。每片含两个相同的D 触发器,可以单独使用。它们都是CP 脉冲的上升沿触发,该芯片的直接置位、复位端信号为正脉冲有效。

图8-9 D触发器CC4013管脚功能图(www.daowen.com)

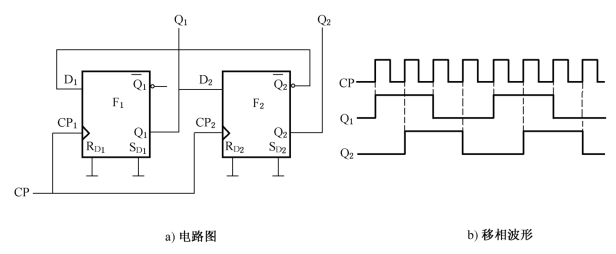

例8-2 如图8-10a所示为由一片双D 触发器组成的移相电路,可输出两个频率相同,相位差90°的脉冲信号,已知CP波形,试画出Q1和Q2 端的波形,设F1 和F2 的初态为0。

解 电路中,F1 的Q1 接F2 的D2,F2 的 接F1 的D1,两个D 触发器共用一个CP脉冲。在CP脉冲的作用下,可得如图8-10b所示的Q1、Q2 端的波形。可见Q1 超前Q290°。

接F1 的D1,两个D 触发器共用一个CP脉冲。在CP脉冲的作用下,可得如图8-10b所示的Q1、Q2 端的波形。可见Q1 超前Q290°。

图8-10 例8-2图

[思考题]

1.为什么说门电路没有记忆功能,而触发器有记忆功能?

2.基本RS触发器在置1 或置0 脉冲消失后,为什么触发器的状态保持不变?

3.同步RS触发器有什么缺点?

4.试由JK 触发器的真值表推导出其状态方程。

5.D 触发器的![]() 端有什么作用? 使用时如何处理?

端有什么作用? 使用时如何处理?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。

有关电工与电子技术的文章